|

Внутренняя организация МП семейства 80х86 в реальном режиме работы

|

|

|

|

В реальном режиме работы (например, под управлением MSDOS) любой из процессоров семейства 80х86 функционирует просто как 16-разрядный "быстрый" МП 8086, т.е. полностью соответствуют его программной модели.

Внутренние регистры МП

В состав МП входят следующие блоки регистров (табл. 5):

табл. 5

| CS | сегмент кода | |||

| DS | сегмент данных | Сегментные | ||

| SS | сегмент стека | Регистры | ||

| ES | дополнительный сегмент | |||

| IP | указатель команд | |||

| SP | указатель стека | |||

| BP | указатель базы | Регистры | ||

| SI | индексный регистр | |||

| DI | индексный регистр | Общего | ||

| AX | AH | AL | аккумулятор | |

| BX | BH | BL | указатель базы | Назначения |

| CX | CH | CL | счетчик | |

| DX | DH | DL | расширитель аккумулятора | |

| F | регистр флагов |

· блок сегментных регистров. 4 сегментных регистра используются для хранения 16-и разрядных сегментных адресов начала сегмента.

· IP – 16-и разрядный регистр указателя команд, в котором хранится адрес смещения команды в кодовом сегменте.

· регистры общего назначения (РОН) могут использоваться для хранения любой информации. Но, как правило, РОН AX, BX, CX и DX используются в основном для хранения данных и допускают раздельное использование их байтов, а регистры SP,BP,SI,DI используются, в основном, для хранения адресной информации. Кроме того, каждый из РОН имеет специальные функции, которые используются по умолчанию в некоторых командах.

· регистр флагов (признаков) F содержит признаки последней выполненной АЛУ операции.

Организация памяти

Память представляет собой последовательность байтов, каждый из которых имеет 20-и разрядный физический адрес (исполнительный адрес) в диапазоне 00000-FFFFF. Все пространство памяти представляется как набор сегментов, определяемых программным путем. Размер каждого сегмента составляет 64К. В каждый момент времени в памяти имеется 4 сегмента: CS, SS, DS, ES. Эти сегменты могут не пересекаться, могут частично пересекаться, а если содержимое сегментных регистров одинаково, то они полностью совпадают.

|

|

|

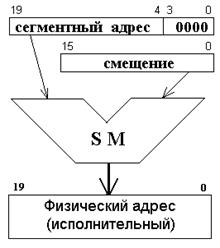

Для определения физического адреса памяти необходимо знать начальный адрес сегмента и внутрисегментное смещение. Физический адрес формируется сумматором блока шинного интерфейса МП (рис. 1) в соответствии со следующей формулой:

FA = SR*16 + ЕА, где:

FA – физический адрес;

SR – содержимое текущего сегментного регистра;

ЕА – эффективный адрес.

рис. 1

Сегментный адрес хранится в одном из сегментных регистров (16 старших разрядов 20-ти разрядного адреса памяти). При вычислении физического адреса памяти к содержимому сегментного адреса дописываются нули. Поэтому начальные адреса сегментов всегда кратны 16.

Смещение в сегменте формируется процессором в зависимости от его режима работы. Если процессор выполняет выборку команд из памяти, то сегментный адрес берется из регистра CS, а смещение – из указателя команд IP (рис. 2). Во всех остальных случаях смещение формируется из содержимого РОН, индексных или базовых регистров. Способ вычисления смещения является способом адресации.

рис. 2

Внутрисегментный адрес называется смещением, если речь идет об аппаратных средствах. В системе команд в этом случае используется понятие эффективный адрес.

Для точного указания адреса в памяти используется логический адрес, который имеет следующий формат записи:

SR:EA; где SR – содержимое сегментного регистра; EA – эффективный адрес.

Например, пусть DS=2000H, EA=3100H. Тогда:

Логический адрес: 2000:3100

Физический адрес: 2000 0 + 3100 = 23100

Иногда объем памяти измеряется в параграфах (§): 1§ = 16 байт.

Система прерываний МП

|

|

|

Прерывание – это событие, которое прерывает нормальный ход выполнения программы (процесса).

МП 80х86 имеет эффективную систему прерываний, в которой каждому прерыванию поставлен в соответствие код (от 0 до 255), который идентифицирует тип прерывания. В системах с МП 8086 различают внешние и внутренние прерывания.

Внешние прерывания – это прерывания, обусловленные каким-либо внешним событием. Сигнал свершения этого события поступает на один из двух входов МП:

INTR – вход маскируемого запроса прерывания от внешних устройств;

NMI – вход немаскируемого запроса прерывания.

Для разрешения обслуживания внешних прерываний используется выход подтверждения прерывания  .

.

МП имеет только один вход для запроса прерывания, а устройств, требующих обслуживания по прерыванию в системе может быть несколько. Для обслуживания прерываний от нескольких устройств используется специализированная МС - программируемый контроллер прерывания (ПКП). ПКП выполняет следующие основные функции:

· фиксирует запросы прерываний от внешних устройств;

· анализирует приоритеты поступивших прерываний;

· запрашивает у МП и, в случае подтверждения прерывания, выдает МП номер прерывания с наивысшим приоритетом.

При поступлении на один из входов ПКП IRQ0-IRQ7 запроса прерывания от внешнего устройства (рис. 3), ПКП фиксирует это прерывание, анализирует его приоритет и, если поступившее прерывание имеет наивысший в данный момент приоритет, выдает МП сигнал запроса прерывания INTR. При поступлении на вход INTR сигнала высокого уровня процессор заканчивает выполнение текущей команды и выдает сигнал подтверждения прерывания  , который поступает на соответствующий вход ПКП. В ответ на этот сигнал ПКП процессору информации не передает. Затем процессор вырабатывает еще один сигнал

, который поступает на соответствующий вход ПКП. В ответ на этот сигнал ПКП процессору информации не передает. Затем процессор вырабатывает еще один сигнал  , в ответ на который ПКП передает МП по шине данных байт, определяющий номер (тип) прерывания (0 ¸ 255). Этот номер однозначно связан с ПП обслуживания прерывания, на которую затем переходит процессор.

, в ответ на который ПКП передает МП по шине данных байт, определяющий номер (тип) прерывания (0 ¸ 255). Этот номер однозначно связан с ПП обслуживания прерывания, на которую затем переходит процессор.

рис. 3

Прерывания по входу INTR можно разрешить или запретить(замаскировать), управляя состоянием флага I. Для этих целей имеются две специальные команды:

CLI – очистить флаг I=0 (запретить прерывания по входу INTR);

|

|

|

STI – установить флаг I=1 (разрешить прерывания по входу INTR).

Если пришел запрос прерывания, а прерывания были запрещены (I=0), то процессор не обслуживает этот запрос и не запоминает его.

Запрос прерывания по входу NMI является немаскируемым и программно его запретить нельзя. После появления сигнала на входе NMI процессор автоматически переходит к обслуживанию прерывания типа 2 (подтверждение прерывания при этом не требуется). Обычно сигнал запроса прерывания по входу NMI используют события, требующие немедленной обработки (например, аварийное отключение питания).

Запрос прерывания по входу NMI запоминается в МП и имеет более высокий приоритет, чем прерывания по входу INTR.

Внутренние прерывания связаны с определенными событиями внутри процессора или инициируются при помощи команд. В случае внутренних прерываний не вырабатываются сигналы подтверждения прерываний  , процессор просто переходит по вектору, заданному типом прерывания. Виды внутренних прерываний:

, процессор просто переходит по вектору, заданному типом прерывания. Виды внутренних прерываний:

1. прерывание при ошибке деления на “0”. Возникает в том случае, если частное слишком велико или делитель = 0 (тип 0);

2. прерывание по переполнению. Выполняется по команде INTO при условии, что установлен флаг переполнения V=1 (тип 4);

3. прерывание при трассировке. Возникает по окончании команды, если установлен флаг трассировки Т=1 (тип 1);

4. прерывание типа 3. Возникает при выполнении однобайтной команды INT 3. Используется для установки контрольных точек разрыва при отладке программ.

5. программные прерывания при выполнении двухбайтных команд INTn (где n – номер прерывания). Программные прерывания на самом деле ничего не прерывают, а являются удобным средством для доступа к стандартным подпрограммам (функциям ОС).

Рассмотрим взаимосвязь между типом прерывания и п/пр обслуживания прерываний.

Таблица векторов прерываний

рис. 4

Для обслуживания прерываний в системах с МП 8086 используется таблица векторов прерываний объемом 1Кбайт, расположенная с нулевого адреса памяти (0...3FF). На каждый тип прерывания отводится 2 слова (4 байта) памяти, в которых хранится логический адрес п/пр обслуживания прерывания. Слово с большим адресом загружается в сегментный регистр CS, а с меньшим адресом – в регистр указателя команд IP. Таблица векторов прерываний имеет вид представленный на рис. 4.

|

|

|

Таким образом, получив номер типа прерывания, процессор умножает номер типа прерывания на 4 и получает адрес вектора прерывания. При переходе к п/пр обслуживания прерываний МП сохраняет в стеке содержимое CS,IP,F. Затем CS и IP загружаются новым содержимым из вектора прерываний. Возврат из п/пр осуществляется по команде IRET, которая восстанавливает содержимое регистров CS,IP,F из стека.

|

|

|