|

Реализация основного алгоритма

|

|

|

|

Входные блоки модуля накопления выполняют накопление и промежуточное хранение данных первого (младшего) байта. Основными структурными элементами здесь являются счётные блоки, блоки суммирования, и накопительные ОЗУ. Адресация ячеек ОЗУ происходит синхронно канальным импульсам системы регистрации. Накопление происходит непрерывно в каждом цикле регистрации. Число каналов накопления может быть задано. В соответствии с алгоритмом программы микроконтроллера периодически (один раз за несколько циклов регистрации) должна происходить быстрая автоматическая трансляция данных одного из накопительных ОЗУ в буферное ОЗУ.

Описанный механизм реализуется в блоке Kern совместно с внешними микросхемами ОЗУ. В соответствующем схемном файле Kern.gdf объединены счётные блоки, блоки суммирования, адресный блок и необходимые схемы управления.

Для реализации счётного блока с минимальными значениями параметра мёртвого времени на канал используется схема, состоящая из двух буферных счётчиков. Переключение потока входных импульсов между счётчиками производится управляющим триггером синхронно канальным импульсам системы регистрации (рис.5.3).

В то время, когда один из счетчиков находится в режиме счета приходящих на его вход импульсов, данные со второго счетчика через регистр и далее через мультиплексор поступают в последующее устройство обработки информации. Таким образом, мертвое время на канал сокращается до значения равного времени переключения триггерной ячейки внутри ПЛИС. Быстродействие счетчиков характеризуется собственным значением мертвого времени, которое определяет время нечувствительности счетчика, возникающее после регистрации им входного импульса. Параметр регистровой (триггерной) задержки в ПЛИС серии MAX7000S не превышает 2 нс. Это позволяет говорить о том, что предельная входная загрузка может с многократным запасом превышать 107 имп./с.

|

|

|

Счётный блок реализован файлом Count.gdf в графическом редакторе системы MAX+PLUS II. При составлении схемы использованы параметризованные модули (LPM) счётчиков и регистров, а также другие примитивы для комбинационных и последовательных участков схемы. Схемный файл Count.gdf находится в ПРИЛОЖЕНИИ 2.

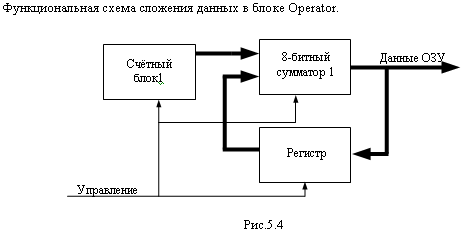

Суммирование выходных данных счётных блоков с данными ОЗУ выполняется в блоке и одноимённом файле Operator. На рисунке 5.4 представлена функциональная схема сложения данных для одного тракта регистрации. В Operator структурно входит два счётных блока, данные с которых, поступают на входы параметризованных модулей сумматоров. На второй вход сумматоров поступают данные ОЗУ, предварительно зафиксированные в регистрах. Фиксация в регистрах необходима для разделения во времени двунаправленных шин данных внешних микросхем ОЗУ.

Управление регистрами осуществляется от внешнего блока Clocking. Кроме указанных элементов на схеме присутствует логика управления и схема перевода выходов сумматоров в третье (высокоимпедансное) состояние.

Полный вариант схемы в виде файла Operator.gdf представлен в ПРИЛОЖЕНИИ 2.

Выборка ячеек внешних микросхем ОЗУ производится адресным блоком, построенным в схемном файле Adr.gdf. Значение адреса генерируется 12-ти разрядным адресным счётчиком на вход, которого подаются, в зависимости от режима работы, канальные импульсы (в процессе накопления) либо тактовые импульсы с частотой 400 кГц (в режиме быстрой автоматической трансляции данных в буферное ОЗУ). Сброс адресного счетчика происходит по приходу стартового импульса схемы регистрации или по приходу сигнала Hold со стороны триггерного блока Trig. Сигнал Hold устанавливается в начале нерабочего режима системы регистрации в том случае, если микроконтроллер программно установил флаг запроса трансляции данных первого байта в буферное ОЗУ (рис.5.5)

|

|

|

Адресный счёт начинается с 000h. Последним на шину выдаётся пороговый адрес. Далее вырабатывается строб окончания счёта Endcount поступающий на вход триггерного блока. Значение порога для адресного счетчика может быть установлено микроконтроллером. Для этого используются дешифратор значений порогового адреса с входами установки P 0 и P 1. По умолчанию пороговым является адрес 4095 (FFFh), для нужд эксперимента программно могут быть установлены значения 2047 (7FFh), 1023 (3FF) и 511 (1FF).

Схемный файл адресного блока Adr.gdf находится в ПРИЛОЖЕНИИ 2.

В процессе автоматической трансляции данных в младшие 12 разрядов 13-ти разрядной шины адреса буферного ОЗУ подключается шина адреса накопительных ОЗУ. Сигнал Selram устанавливаемый микроконтроллером и формируемый триггерной схемой Trig определяет выбор микросхем ОЗУ1 или ОЗУ2 для передачи их данных в конце текущего цикла регистрации. Этот же сигнал подаётся на 13-й (старший) разряд шины адреса буферного ОЗУ. Таким образом происходит разделение пространства памяти буферного ОЗУ на два банка, каждый из которых предназначен для временного хранения данных ОЗУ1 и ОЗУ2.

Триггерная схема (файл Trig.gdf) выполняет роль набора регистров управления элементами блока Kern со стороны микроконтроллера. Схема построена из набора D-триггеров и дополнительных примитивов MAX+PLUS II. Непосредственно микроконтроллером устанавливаются сигналы P 0, P 1 и Selram. Управляющий сигнал Hold устанавливается через определённое время задержки в ответ на сигнал Endcount адресного блока и осуществляет перевод блока Kern и других вышестоящих узлов в режим работы с буферной памятью. Задержка необходима для завершения последней операции записи-чтения ячеек накопительных ОЗУ с пороговым адресом. Функция задержки реализована с использованием четырёхразрядного счётчика, тактируемого внешним сигналом Read.

Файл Trig.gdf графического редактора системы MAX+PLUS II находится в ПРИЛОЖЕНИИ 2.

Корректная работа с микросхемами быстрой статической оперативной памяти невозможна без стогового соблюдения протоколов обмена в соответствии с технической документацией.

|

|

|

Наиболее важным параметром статических ОЗУ является время выборки. Оно характеризует максимальную частоту операций чтения или записи. Современные микросхемы памяти имеют время выборки порядка 30 – 100 нс, что удовлетворяет требованиям проекта. Данный параметр является качественной характеристикой, но наряду с ним существуют и другие параметры, которые необходимо учитывать разработчику при проектировании систем использующих оперативную память. В частности к ним относятся:

- минимальное время удержания активного уровня сигнала CS (выбор кристалла);

- минимальное время удержания активного уровня сигнала WE (разрешение записи) в режиме записи данных;

- минимальное время удержания активного уровня сигнала ОЕ (разрешение выходов) в режиме чтения данных

- минимальное время подачи управляющего сигнала записи с момента установления данных в режиме записи

- минимальное время удержания данных на входах ОЗУ после снятия управляющего сигнала записи в режиме записи

- минимальное время подачи управляющего сигнала чтения с момента установления адреса в режиме чтения и др.

Помимо непосредственного соблюдения протокола обмена синхронных ОЗУ в модуле накопления, нужно учесть и другие особенности их применения. Наличие двунаправленной шины данных между блоками суммирования и микросхемами ОЗУ (рис.4.2) заставляет обратить особое внимание на необходимость правильного разделения во времени потоков данных. Речь идёт о недопустимости одновременного (даже кратковременного) наличия на разделяемой шине данных, двух источников сигналов. То есть между сигналами разрешающими выход данных со стороны двух присутствующих на шине устройств, работающих в режиме непрерывного обмена, должен быть определённый временной интервал.

Всего модуль накопления должен содержать 4 элемента ОЗУ: буферное ОЗУ объёмом 8 Кбайт, системное ОЗУ объёмом 32 Кбайт и два элемента ОЗУ для накопления данных первого байта (ОЗУ1 и ОЗУ2) с объёмом 4 Кбайт каждая. Выработка управляющих сигналов «чтение», «запись» для накопительных ОЗУ в режимах накопления и автоматической трансляции данных, а также сигнала «запись» для буферного ОЗУ в режиме трансляции, происходит в схеме тактирования Clocking (схемный файл Clocking.gdf).

|

|

|

Схема (блок) тактирования производит выдачу управляющих сигналов в соответствии с алгоритмом «чтение-модификация-запись» (рис.4.3) Для соблюдения требуемого протокола обмена, учитывающего все параметры, в схеме организована специальная сетка тактирования с использованием четырёхразрядного счётчика. Определённые выходные значения интерпретируются аналитической схемой как маркерные точки для своевременной установки или снятия сигналов OE, WE, CS микросхем накопительной памяти и сигнал WrBRAM микросхемы буферной памяти. Генератор управляющих стробов выдаёт указанные сигналы синхронно импульсам Canal или Read в соответствии с состоянием сигнала Hold, формируемого триггерной схемой. Помимо перечисленных сигналов блок тактирования генерирует строб приёма данных ClkRG для регистров операторного блока Operator. Положительный фронт сигнала ClkRG соответствует времени появления действительных данных на выходах накопительных ОЗУ.

Схема (блок) тактирования производит выдачу управляющих сигналов в соответствии с алгоритмом «чтение-модификация-запись» (рис.4.3) Для соблюдения требуемого протокола обмена, учитывающего все параметры, в схеме организована специальная сетка тактирования с использованием четырёхразрядного счётчика. Определённые выходные значения интерпретируются аналитической схемой как маркерные точки для своевременной установки или снятия сигналов OE, WE, CS микросхем накопительной памяти и сигнал WrBRAM микросхемы буферной памяти. Генератор управляющих стробов выдаёт указанные сигналы синхронно импульсам Canal или Read в соответствии с состоянием сигнала Hold, формируемого триггерной схемой. Помимо перечисленных сигналов блок тактирования генерирует строб приёма данных ClkRG для регистров операторного блока Operator. Положительный фронт сигнала ClkRG соответствует времени появления действительных данных на выходах накопительных ОЗУ.

Тактовый, меандровый сигнал с частотой 20 МГц подаётся на счётчик от внешнего, относительно ПЛИС генератора. В режиме накопления сигнал тактирования дополнительно проходит через делитель частоты на 5, выполненный на базе четырёхразрядного счётчика из набора макрофункций системыMAX+PLUS II.

Принцип работы блока тактирования отражён на функциональной схеме (рис.5.6).

Схемный файл блока тактирования Clocking.gdf находится в ПРИЛОЖЕНИИ 2.

Тестирование блока проведено в сигнальном редакторе системы MAX+PLUS II. В качестве входных тестовых векторов введены сигналы: с lk (сигнал тактирования частотой 20 МГц), с anal (канальные импульсы системы регистрации), read (сигнал тактирования режима быстрой трансляции) и hold (сигнал перевода в режим быстрой трансляции).

В режиме накопления блок тактирования генерирует сигналы управления eo (enable output) и write синхронно импульсам с anal, в режиме быстрой трансляции дополнительно генерируется сигнал записи буферного ОЗУ wrBRAM синхронно импульсам read. Результаты тестирования обоих режимов приведены на рисунке 5.7. Временные интервалы на диаграмме указаны в микросекундах.

Адресный блок вырабатывает значение адреса ячеек накопительного ОЗУ по отрицательному фронту импульса canal или read в зависимости от режима работы. Сигналы разрешения выходов формируются не ранее 120 нс. Выдача сигнала защёлкивания (чтения) данных в обоих случаях происходит не ранее чем через 200 нс после импульса ео. Послестояние данных при операциях записи ОЗУ составляет не менее 19 нс. Такие временные параметры призваны обеспечить устойчивую работу модуля накопления.

|

|

|

В режиме быстрой трансляции необходимо проводить запись нулевых байтов в ячейки накопительного ОЗУ, данные которых, уже перенесены в буферное ОЗУ.

За время нерабочего режима системы регистрации может быть произведена трансляция данных только одной из микросхем накопительного ОЗУ (в соответствии со значением сигнала Selram). При этом незанятое накопительное ОЗУ должно находится в режиме хранения данных.

Таким образом, необходимо обеспечить раздельную выдачу команд управления (EO, WR) для каждого накопительного ОЗУ.

Функции разделения команд, а также дополнительные функции выдачи сигналов обнуления на формирователи шин данных накопительных ОЗУ реализованы в блоке формирования Form. Соответствующий схемный файл Form.gdf графического редактора MAX+PLUS II находится в приложении 2.

Помимо рассмотренных устройств, в блоке Kern присутствуют дополнительные элементы, не включённые ни в один внутриструктурный файл этого блока. К ним относятся схема формирователя шины данных для буферного ОЗУ, управляемая сигналами hold и Selram, и триггер разрешения счёта импульсов от внешних трактов регистрации.

Триггер разрешения счёта должен использоваться для работы модуля в режиме снятия амплитудных спектров, для запуска счёта на очередном этапе сканирования.

Файл Kern.gdf графического редактора системы MAX+PLUS II находится в приложении 2.

|

|

|