|

Двухступенчатые триггеры структуры «МS»

|

|

|

|

Студент должен

Знать:

· Назначение, принцип работы двухступенчатых триггеров и их особенности;

· Параметры, характеризующие работу триггера;

Уметь:

· Выбирать микросхему триггера исходя из заданных параметров и условий использования.

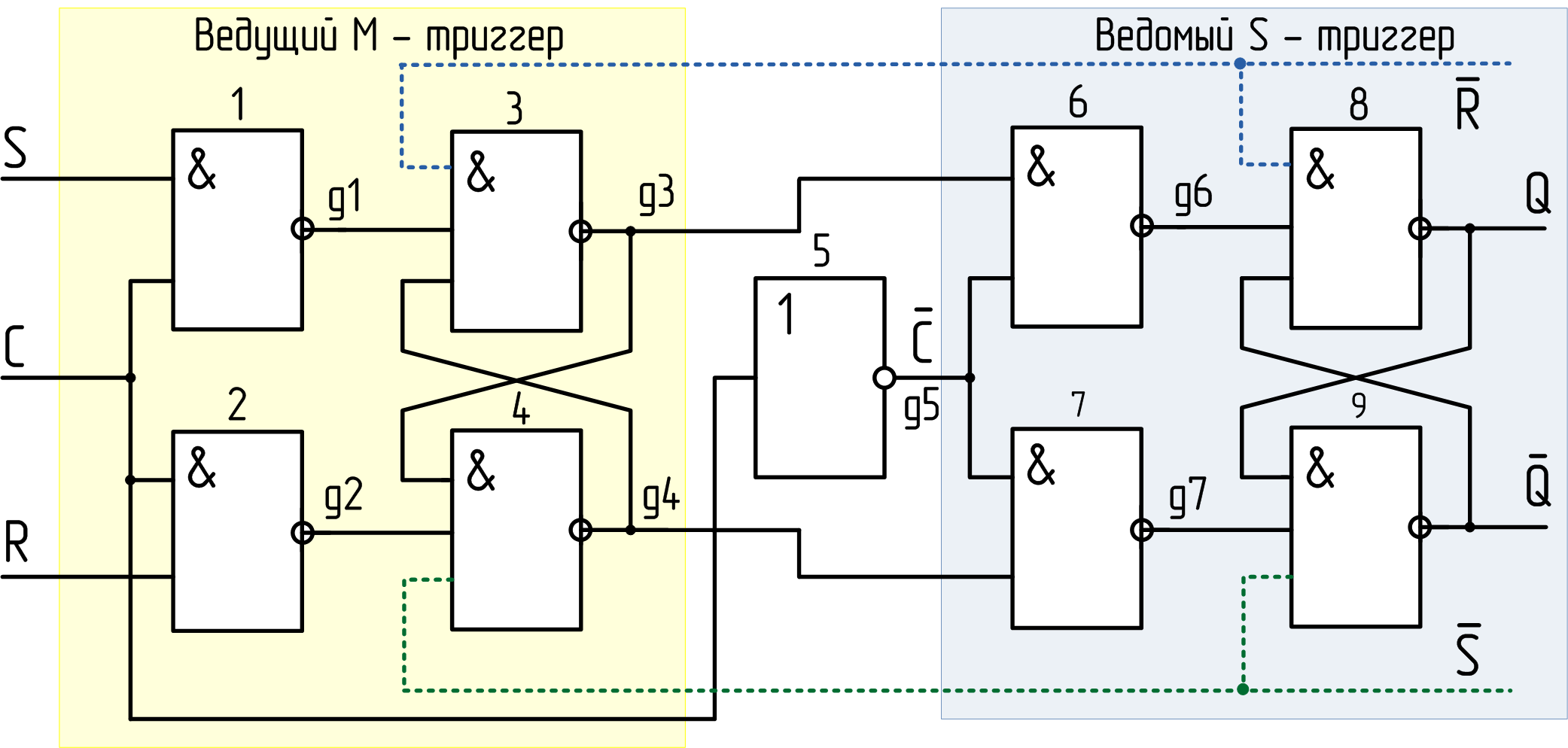

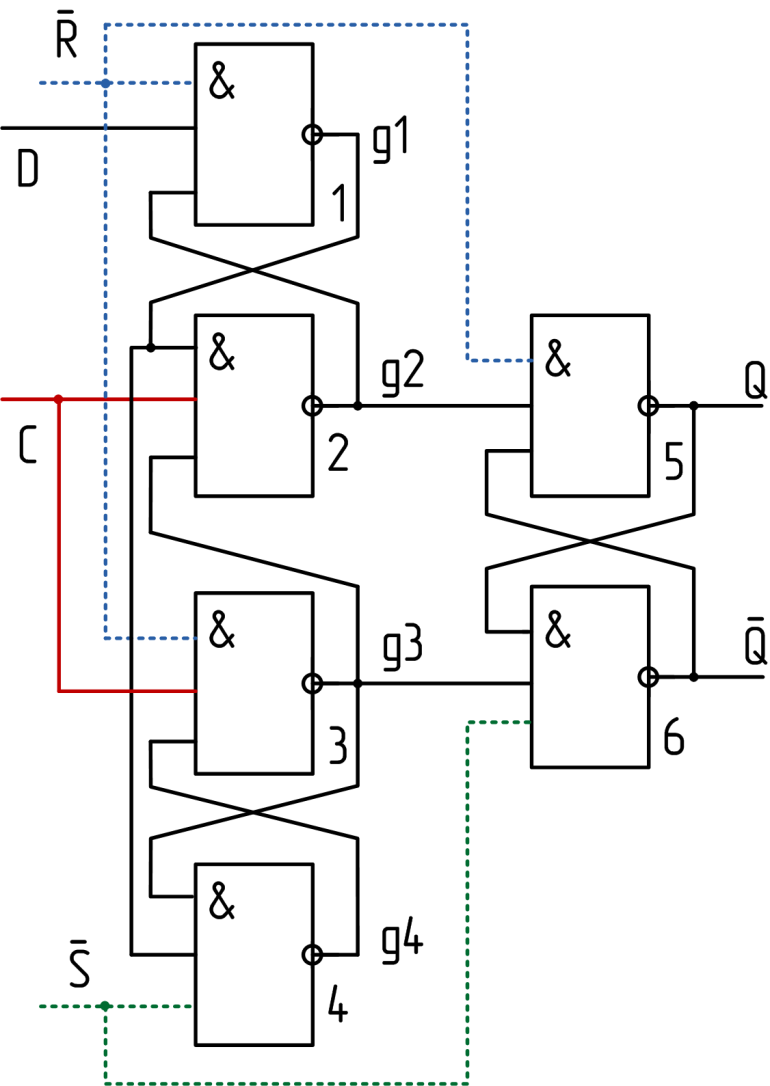

На рисунке 5.12 дана схема и условное обозначение двухступенчатого RS -триггера MS -структуры («ведущий-ведомый») на элементах И-НЕ.

Триггер состоит из двух одинаковых синхронных RS -триггеров со статическим управлением. Тактовый вход ведущего триггера (М) связан с входом ведомого (S) инвертором 5.

Рисунок 5.12

До прихода тактового импульса (С =0) входные элементы 1 и 2 заперты, q1=q2=1 и ведущий (М) триггер хранит информацию от предыдущего такта. Ведомый (S) триггер, на тактовом входе которого действует сигнал q5=1, открыт и повторяет состояние ведущего, характеризуемое сигналами q3 и q4.

С приходом импульса С=1 в ведущий М - триггер заносится информация с входов S и R. Ведомый S - триггер в это время блокирован, поскольку q5=  =0.

=0.

С прекращением тактового импульса запирается ведущий М - триггер, а ведомый открывается и принимает состояние ведущего. С этого момента на выходах будут сигналы Qn+1=Sn и Qn+1=Rn

В двухступенчатом триггере в отличие от одиночного синхронного триггера со статическим управлением смена входной информации может происходить и во время действия тактового импульса, так как перезапись сигналов из первой ступени во вторую происходит с окончанием тактового импульса, т.е. по принципу внутренней задержки.

Двухступечатый RS – триггер функционирует согласно таблице истинности для асинхронных триггеров, выполненных на логических элементах ИЛИ - НЕ.

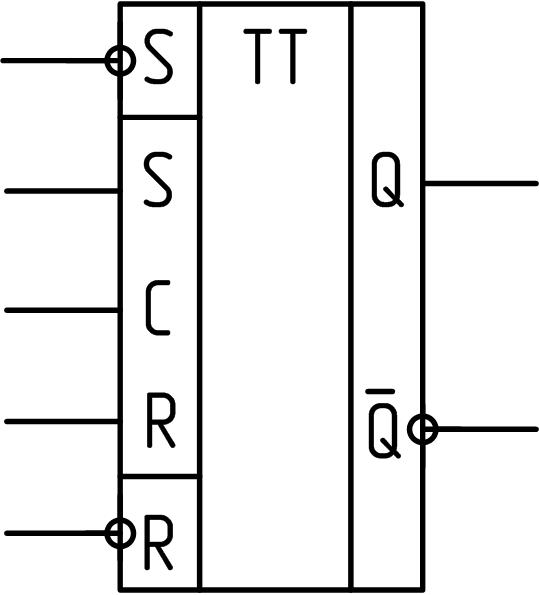

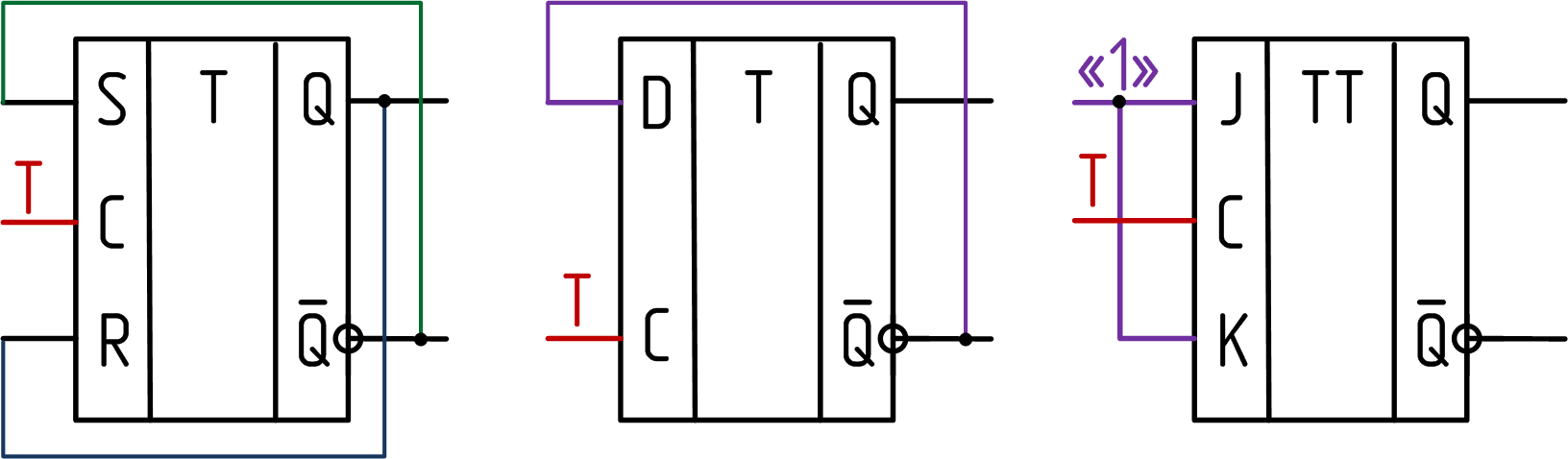

Условное обозначение MS - триггера со статическим управлением показано на рисунке 5.13. Две буквы Т (ТТ) в основном поле микросхемы указывают о двухступенчатой структуре триггера.

|

|

|

Рисунок 5.13

Триггеры MS – структуры используются для надежной работы триггерных ячеек в многоразрядных устройствах (регистрах, счетчиках), благодаря замечательному свойству: входы приема данных во время загрузки 1 бита информации не имеют сквозной связи с выходными цепями (такой триггер называют непрозрачным, у него входы и выходы изолированы).

Контрольные вопросы:

1. Что такое триггер? Перечислите области их применения?

2. Благодаря чему триггер обладает памятью?

3. Перечислите разновидности RS – триггеров?

4. Какие входы имеет RS – триггер? Их назначение?

5. Какими способами можно описать закон работы триггера?

6. Какие сигналы переключат триггер (рисунок 5.8) в нулевое состояние?

7. Что такое запрещенная комбинация? Когда она возникает? Чем опасна запрещенная комбинация?

8. Какими достоинствами и недостатками обладают синхронные RS триггеры?

9. Объяснить принцип работы синхронного триггера структура которого показана на рисунке 5.11, а.

10. Чем отличается принцип работы синхронных триггеров со статическим и динамическим управлением?

11. Построить временную диаграмму работы синхронного RS триггера на логических элементах ИЛИ-НЕ с динамическим управлением по срезу?

12. Как устроен двухступенчатый триггер МS – структуры?

13. Для чего входы синхронизации ведущего и ведомого триггера соединены через инвертор?

14. Составьте таблицу истинности триггера МS – структуры со статическим управлением.

15. Представьте временные диаграммы работы МS – триггера со статическим управлением (на диаграмме показать выходные сигналы ведущего и ведомого триггеров).

16. По временной диаграмме объяснить принцип работы триггера МS – структуры.

17. Почему триггер МS – структуры называют «непрозрачным»?

|

|

|

18. Как по условному обозначению определить, что триггер имеет двух ступенчатую структуру?

JK – триггеры

Студент должен

Знать:

· Назначение, принцип работы, особенности триггеров JK -типа;

· Параметры, характеризующие работу триггера.

Уметь:

· Выбирать микросхему триггера исходя из заданных параметров и условий использования.

По принципу работы JК – триггер подобен синхронному RS -триггеру, но не имеет запрещённых состояний. Вход J играет роль входа S, а К – вход соответствует R – входу.

Своё название триггер берёт от слов Jerk – резкий толчок, внезапное включение и Kill – убивать, отключение.

В схемном отношении JK -триггеры отличаются от триггеров RS – типа наличием обратных связей с выходов на входы.

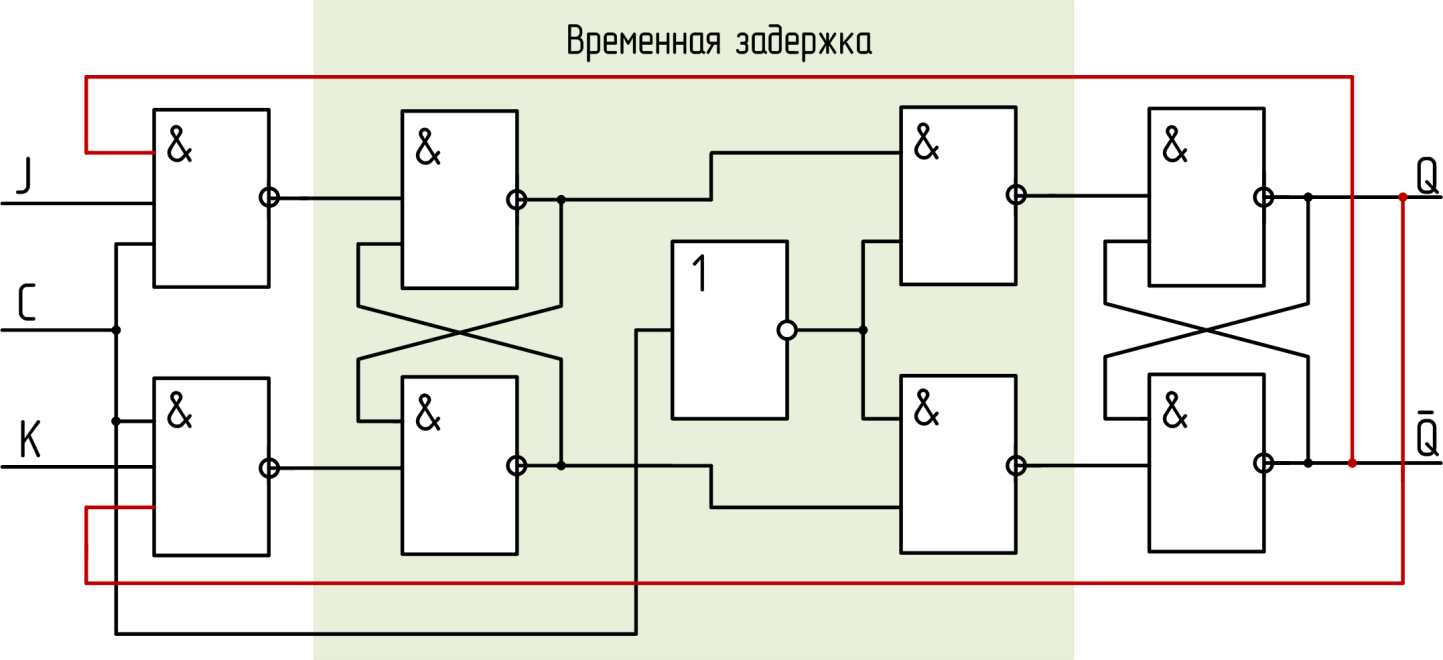

В цифровой интегральной схемотехнике применяются только синхронные JK –триггеры. Логическая структура простейшего синхронного JK -триггера показана на рисунке 5.14.

Рисунок 5.14

Функциональная особенность JK – триггеров состоит в том, что при всех входных комбинациях, кроме одной Jn = Kn = 1 они действуют подобно RS – триггеру. При входной комбинации Jn = Kn = 1 с поступлением импульса синхронизации происходит переключение триггера в противоположное состояние. Триггер работает в счетном режиме.

На рисунке 5.15 представлена упрощенная логическая структура JK – триггера.

Рисунок 5.15

В схеме (рисунок 5.15) элементы 1 и 2 представляют устройство управления, элементы 5 и 6 образуют ячейку памяти.

Элементы 3 и 4 представляют временную задержку между моментом ввода входной инормации  и началом формирования выходной

и началом формирования выходной  без этих цепей во время действия входной комбинации J=K=1 возникает момент, когда на входе Jn сигнал ещё не прекратился, а на выходе

без этих цепей во время действия входной комбинации J=K=1 возникает момент, когда на входе Jn сигнал ещё не прекратился, а на выходе  уже появилась новая информация

уже появилась новая информация  , которая подаётся на вход первого логического элемента, вызывая новое переключение триггера в этом же такте. Для предотвращения многократных переключений время задержки должно быть выше длительности тактового импульса, поэтому JK – триггеры строят по двухступенчатой структуре.

, которая подаётся на вход первого логического элемента, вызывая новое переключение триггера в этом же такте. Для предотвращения многократных переключений время задержки должно быть выше длительности тактового импульса, поэтому JK – триггеры строят по двухступенчатой структуре.

Как и в любом двухступенчатом триггере по фронту тактового импульса информация с выходов J и K записывается в первый триггер (на элементах DD1.1 – DD1.4), а по срезу – во второй триггер (на элементах DD2.1 – DD2.4) (рисунок 5.14).

|

|

|

Функционирование JK -триггера отражено в таблице 5.4 из которой видно, что при трех комбинациях входных сигналов (J = K = 0; J = 1, K = 0; J = 0, K = 1) JK -триггер работает как синхронный RS -триггер, т.е. обратные связи не влияют на его работу, а при комбинации J = K = 1 триггер работает с четном режиме.

Таблица 5.4 - Функционирование JK - триггера

| Такт n | Такт n+1 | ||

| Jn | Kn | Qn+1 | Режим работы |

| Qn | Хранение информации | ||

| Запись 0 | |||

| Запись 1 | |||

| Счётный режим |

Условное графическое обозначение JK -триггера приведено на рисунке 5.16.

Рисунок 5.16

JK – триггеры являются универсальными, поскольку на его основе можно получить триггеры RS -, D - и Т - типов, соединив входы J и K по определенной схеме.

JK – триггеры могут быть использованы в сдвиговых регистрах, счетчиках, делителях частоты.

Триггеры JK – типа производятся во многих сериях интегральных микросхем и имеют маркировку ТВ, например К155ТВ1, К561ТВ1, К155ТВ15.

Контрольные вопросы:

1. Для чего в триггере JK типа выполняются две положительные обратные связи?

2. Какую роль выполняют элементы 3 и 4, входящие в логическую структуру JK – триггера (рисунок 5.15)?

3. Объяснить работу триггера при подаче на его вход сигналов: J=0, K=1, C=0; J= 1, K=0, C= 1; J= 1,K=1,C=1 (рисунок 5.14).

4. Представить временные диаграммы работы JK – триггера (рисунок 5.14).

5. Какие сигналы на входах обеспечивают сброс триггера?

6. Какие входные комбинации сигналов не допустимы для JK – триггеров?

7. Почему на условном обозначении JK – триггера в основном поле две буквы Т (ТТ)?

8. Почему JK – триггер называют универсальным?

Триггеры D – типа

Студент должен

Знать:

· Назначение, принцип действия триггера D-типа;

· Временные диаграммы, таблицы переключений триггера D-типа;

· Параметры D-триггеров.

Уметь:

· Выбрать микросхему триггера исходя из заданных параметров и условий использования.

D -триггеры имеют один информационный вход D -вход для установки в нулевое или единичное состояние и вход С для подачи синхроимпульсов.

Функциональная особенность триггеров этого типа состоит в том, что сигнал с входа D записывается в триггер и передаётся на выход Q при поступлении на вход синхронизации активного уровня сигнала.

|

|

|

Другими словами D - триггер задерживает на один такт информацию, существовавшую на входе D. Для устойчивой работы схемы необходимо, чтобы информация на входе D не изменялась во время действия импульса синхронизации.

Обозначение входа D - это первая буква английского слова delay - затяжка, задержка. D -триггеры часто так и называют - триггерами задержки.

Закон функционирования D-триггера очень прост:

Qn+1 = Dn

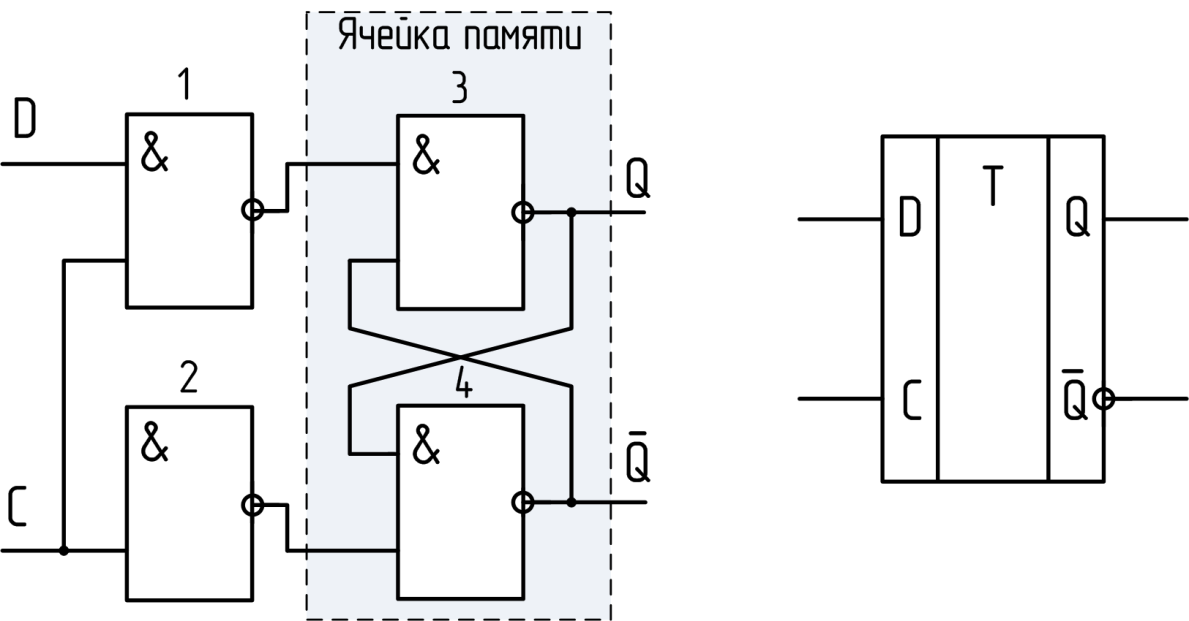

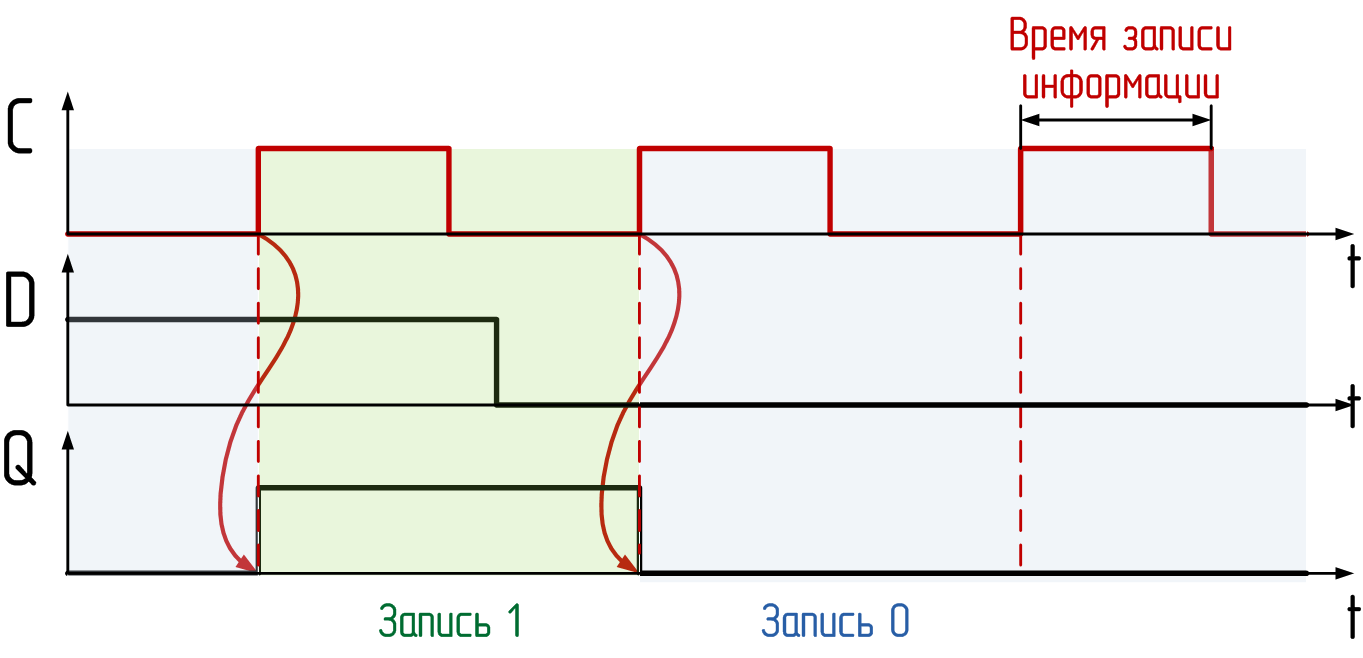

На рисунке 5.17, а и б показана логическая структура и условное обозначение D -триггера со статическим управлением.

а) б)

Рисунок 5.17

Триггер выполнен на элементах И-НЕ. Элементы 3 и 4 образуют ячейку памяти, а 1 и 2 -схему управления.

В паузах между импульсами синхронизации элементы 1 и 2 закрыты и на их выходах существуют сигналы высокого уровня, что служит нейтральной комбинацией для основной ячейки памяти. Так как хранение информации D -триггерами обеспечивается за счет цепей синхронизации, поэтому все реальные D -триггеры - тактируемые.

При поступлении импульса синхронизации данные с входа D записываются в триггер и передаются на выход Q.

Принцип работы триггера поясняет сокращённая таблица 5. 5 и временные диаграммы, приведённые на рисунке 5.18.

Таблица 5.5 - Функционирование D - триггера

| Такт n | Режим работы | ||

| С | Dn | Qn+1 | |

| Запись 0 | |||

| Запись 1 | |||

| Х | Qn | Хранение информации |

Примечание: Х - любое состояние (0 или 1).

Рисунок 5.18

Управление по входу синхронизации входу может быть также динамическим.

D- триггер можно получить преобразованием синхронного RS - или JK -триггера, если на их информационные входы одновременно подавать взаимно инверсные сигналы. Однако выгоднее применять специализированные ИМС т.к. в каждом корпусе располагаются 2, 4, 6 или 8 триггеров.

Способы преобразования RS - и JK – триггеров в D – триггеры представлены на рисунке 5.19, а и б.

Рисунок 5.19

Микросхемы D триггеров имеют маркировку ТМ, например, К155ТМ2.

Микросхема К155TM2

В одном корпусе микросхемы находится два одинаковых триггера, связанных только общим питанием (рисунок 5.20).

Рисунок 5.20

Логическая структура одного такого триггера приведена на рисунке 5.21.

Рисунок 5.21

От схемы D -триггера со статическим управлением на рисунке 5.17 она отличается тем, что вместо одного логического элемента 1 или 2 здесь применены бистабильные ячейки 1-2 и 3-4. Эти триггеры - с прямым управлением: запись информации происходит по фронту перехода тактового импульса от 0 к 1.

Кроме того, есть дополнительные входы Ra и Sa для асинхронной установки триггера в нулевое и единичное состояния. Чтобы не загромождать схему, цепи асинхронного управления показаны штриховыми линиями.

|

|

|

Закон функционирования триггера с учетом асинхронного режима приведен в таблице 5.6.

Таблица 5.6 - Таблица состояний триггера К155ТМ2

| Такт n | Такт n+1 | Режим | |||

| Sa | Ra | C | Dn | Qn+1 | |

| Синхронный | |||||

| X X X | Qn Qn Qn | Хранение | |||

| X | X | Асинхронный | |||

| X | X | ||||

| X | X | Q=Q=1 | Режим запрета |

Триггеры DV – типа

Триггеры DV – типа представляют собой модификацию D – триггеров (рисунок 5.22).

Рисунок 5.22

Вход V является входом разрешения действия синхросигнала на триггер.

Когда V=1, триггер функционирует как D – триггер, а при V=0, он переходит в режим хранения информации независимо от смены сигналов на входе D.

Временные диаграммы работы DV-триггера представлены на рисунке 5.23.

Рисунок 5.23

Наличие V – входа расширяет функциональные возможности D – триггера, позволяя в нужные моменты времени сохранять информацию на выходах в течение требуемого числа тактов.

DV – триггеры широко применяются в устройствах запоминания двоичной информации в качества разряда регистра или счётчика и в других узлах цифровой техники. Эти триггеры очень удобны в быстродействующих системах, поскольку передача информации происходит по одному входу, т. е. исключено состязание сигналов.

Контрольные вопросы:

1. Объяснить назначение D, С, входов триггеров.

2. Почему D -триггер задерживает выходную информацию?

3. Используя таблицу переключений микросхемы триггера К155 ТМ2, объяснить его режимы работы.

4. Область применения триггеров D -типа.

5. Показать условное обозначение DV – триггера и объяснит назначение его входов?

6. Представьте временные диаграммы триггера DV – типа.

7. Используя временные диаграммы триггера DV – типа объяснить принцип его работы.

8. Область использования триггеров DV – типа.

Т – триггеры

Студент должен

Знать:

· Назначение, принцип работы триггеров T,TV - типа;

· Временные диаграммы, таблицы переключений триггеров T,TV - типа.

Уметь:

· Производить преобразование различных триггеров в триггер T,TV - типа.

Триггер Т-типа, или счетный триггер, имеет один информационный T- вход (от англ. Toggle -чека коленчатый рычаг) на который поступают счётные импульсы. Каждый счётный импульс изменяет состояние триггера на противоположное.

По способу ввода входной информации Т -триггеры могут быть асинхронными и синхронными со статическим или динамическим управлением.

Условное обозначение асинхронного триггера с динамическим управление по срезу и временные диаграммы, поясняющие работу, представлены на рисунке 5.24.

Рисунок 5.24

Принцип работы триггера асинхронного триггера с динамическим управление по срезу представлен в таблице 5.7.

Таблица 5.7 - Функционирование асинхронного Т – триггера с динамическим управлением по срезу

| Tn | Qn+1 | Режим работы |

| Qn | Хранение информации | |

| Qn | ||

| Qn | ||

| Счётный режим |

Поскольку управление происходит по одному входу, Т-триггеры неопределенных состояний не имеют.

Т – триггер может использоваться в качестве делителя частоты входных сигналов. Из временной диаграммы работы триггера (рисунок 5.24) видно, что он является делителем частоты на два. При периодическом входном сигнале выходная частота уменьшается в два раза  и скважность выхода всегда равна двум Q=Т/tимп.=2 независимо от частоты сигнала на счётном входе.

и скважность выхода всегда равна двум Q=Т/tимп.=2 независимо от частоты сигнала на счётном входе.

Синхронный Т-триггер отличается наличием на входе Т конъюнктора, один из входов которого выполняет роль счётного входа T, а второй является входом синхронизации.

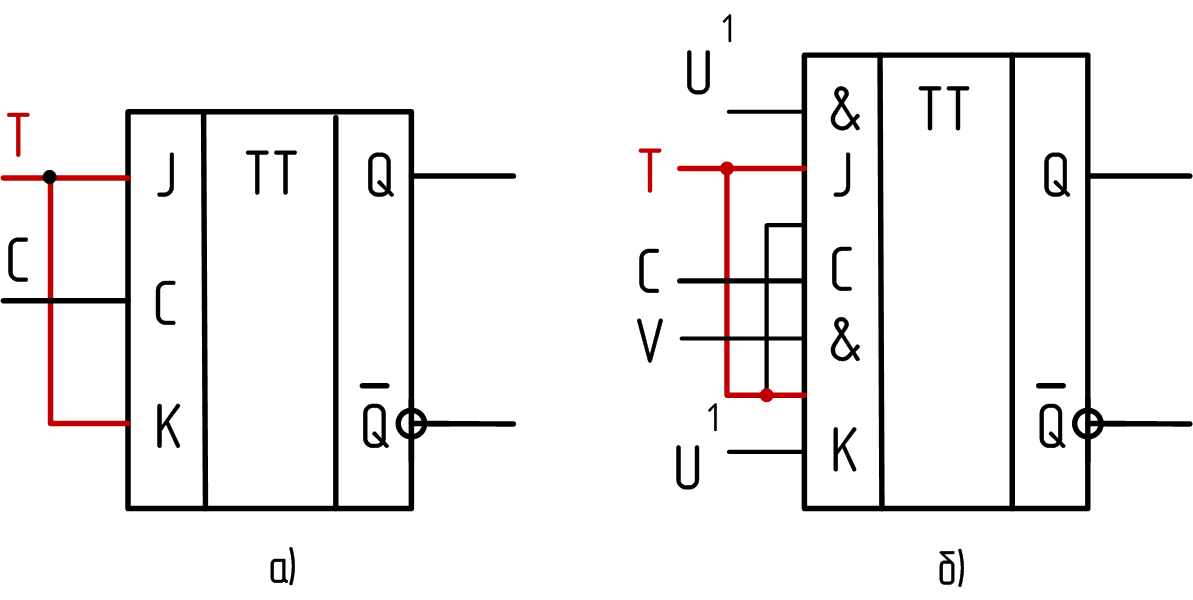

Синхронный Т-триггер представлен на рисунке 5.25.

Рисунок 5.25

В интегральном исполнении в виде самостоятельных изделий Т -триггеры не производятся. Т – триггеры получают из RS-, D-, JK- триггеров путем определенных соединений выводов.

На рисунке 5.26 показаны способы получения асинхронных Т -триггеров из триггеров RS-, D-, JK – типа.

Рисунок 5.26

На рисунке 5.27 представлено преобразование JK -триггера в синхронный счётный триггер.

Рисунок 5.27

Триггер TV-типа

Триггер TV -типа кроме счетного входа имеет второй, управляющий V -вход для разрешения приема информации с счётного входа Т.

Переключательные функции TV –триггера характеризует таблица 5.8.

Таблица 5.8 - Состояния TV – триггера

| Такт n | Такт n + 1 | Режим работы | |

| Vn | Tn | Qn+1 | Хранение информации |

| Qn | |||

| Qn | |||

| Qn | |||

| Режим переключения |

В литературе TV –триггер иногда называют тактируемым или синхронным счетным триггером. Его легко получить из JK –триггера (рисунок 5.28).

Асинхронные и синхронные Т– и TV –триггеры в основном применяются для счета входных импульсов и для деления их частоты. Их применение в счетчиках основано на том, что каждому входному импульсу соответствует один переброс, т.е. число перебросов равно числу входных импульсов.

Последовательная цепочка из n счетных триггеров представляет собой простейший двоичный счетчик емкостью 2n. В таком счетчике состояние выходов триггеров отображает в двоичном коде число входных импульсов.

Рисунок 5.28

Контрольные вопросы:

1. Какое назначение имеют триггеры Т – типа?

2. Привести примеры построения асинхронных и синхронных счетных триггеров из триггеров других типов.

3. Объяснить принцип работы счетного триггера, используя таблицу истинности и временные диаграммы.

4. Привести примеры использования триггеров Т – типа.

5. Как получить триггер ТV – типа? Привести примеры построения.

6. Объяснить принцип работы TV – триггера с помощью временных диаграмм.

Регистры

| Регистром называют выполненное на триггерах того или иного типа последовательностное устройство, основной функцией которого является хранение информации в виде N-разрядного двоичного кода. |

Элементами структуры регистра являются синхронные триггеры D-, RS- или JK- типа с динамическим или статическим управлением. Простейшим регистром является триггер. Способный хранить 1 разряд (1 бит) информации. Количество триггеров в регистре зависит от разрядности запоминаемого числа. Кроме триггеров в схемы регистров входят комбинационные элементы с помощью которых обеспечивается выполнение различных операций над двоичными словами:

· запись слова в регистр или выдача слова из регистра;

· сдвиг вправо или влево;

· преобразование последовательного кода в параллельный и наоборот;

· сброс.

Чаще всего для построения регистров используются D-триггеры.

Занесение новой информации в регистр из внешнего устройства называют записью, вывод информации из регистра во внешнее устройство – считыванием.

Регистры классифицируются:

· по способу записи/считывания информации;

· по функциональному признаку.

По способу записи/считывания информации различают:

· параллельные регистры, в которых запись и считывание выполняются в параллельном коде;

· последовательные регистры, в которых запись и считывание выполняются в последовательном коде. В процессе записи данные заносятся последовательно во времени бит за битом, при считывании также бит за битом выводятся из регистра;

· параллельно-последовательные регистры, в которых при записи все биты поступают в регистр одновременно (в параллельном коде), а при считывании покидают регистр бит за битом (в последовательном коде). Такие регистры являются преобразователями параллельного кода в последовательный;

· последовательно-параллельные регистры, в которых запись выполняется в последовательном коде, а считывание – в параллельном. Такие регистры служат для преобразования последовательного кода в параллельный.

По функциональному признаку регистры разделяют на две большие группы:

· регистры хранения, выполняющие только одну, основную, функцию;

· регистры сдвига, выполняющие помимо хранения сдвиг информации вдоль регистра. Среди регистров этой группы выделяют реверсивные регистры, позволяющие сдвигать информацию в обе стороны.

Регистры памяти

Студент должен

Знать:

· Назначение параллельных регистров;

· Принцип работы параллельных регистров;

· Параметры параллельных регистров.

Уметь:

· Выбирать микросхемы регистров по справочнику, исходя из заданных параметров и условий использования.

В параллельных регистрах запись двоичного числа (слова) осуществляется параллельным кодом, т.е. во все разряды одновременно. Их функция сводится только к приему, хранению и передачи параллельным кодом двоичной информации, поэтому такие регистры часто называют регистрами памяти.

Рассмотрим параллельный 3-разрядный регистр состоящий из 3-триггеров RS типа, каждый из которых хранит один разряд двоичного числа, его схема показана на рисунке 5.29.

В начале работы все триггеры устанавливаются в нулевое состояние подачей импульса низкого уровня по входу «Сброс».

Конъюнктуры D1.1- D1.3 пропускают двоичную информацию на входы D триггеров только при наличии импульса высокого уровня на входе «Ввод данных».

Запись поступившей на входы триггеров D2.1- D2.3 информации происходит параллельным кодом при поступлении на вход «Синхронизация» импульса высокого уровня.

По окончании операции записи информация, записанная в регистр, сохраняется, не смотря на то, что входная информация может изменяться.

Для считывания информации подают импульс по входу «Вывод данных». На выходные шины регистра через конъюнктуры D3.1- D3.3 передаётся код числа, записанный в разрядах триггеров. При этом число, записанное в регистр, не разрушается и его можно многократно считывать.

Режим хранения обеспечивается прекращением поступления импульсов синхронизации.

Рисунок 5.29

Условное обозначение параллельного трёхразрядного регистра показано на рисунке 5.30.

Рисунок 5.30

Регистр параллельного действия используется как элемент оперативной ОЗУ, а также в качестве элементов автоматики в устройствах на основе вычислительной техники.

Промышленность выпускает регистры с количеством разрядов от 4, 6, 8, 12. Если требуется большая разрядность, то данные регистры можно соединить параллельно.

В качестве регистра хранения могут быть использованы микросхемы содержащие несколько самостоятельных триггеров – К155ТМ8, К155ТМ5, К155ТМ7, 564ТМ,555ТМ8 и другие.

В качестве самостоятельных регистров выпускаются ИМС, например К155ИР15.

В качестве примера рассмотрим микросхему регистра К155ИР15. Приведем условное обозначение и таблицы внутренних выходных состояний регистра К155ИР15 (рисунок 5.31).

Рисунок 5. 31

Микросхема К155ИР15 представляет собой четырехразрядный параллельный регистр памяти с тремя выходными состояниями.

Микросхема имеет следующие выводы:

· D1-D4 -информационные входы;

· Q1-Q4 -выходы регистра;

· С – вход синхронизации;

· R – вход сброса триггеров регистра;

· Е1 и Е2 – входы для управления режимом режимами работы регистра;

· Ez1 и Ez2 – входы для перевода выходов регистра в высокоимпендансное состояние.

При подаче 1 на вход R осуществляется сброс триггеров регистра.

При Е1=Е2=0 осуществляется параллельный ввод информации со входов D1-D4 при воздействии положительного перепада на входе синхронизации С.

Хранение информации осуществляется, если хотя бы на одном из входов Е1 или Е2 действует логическая 1.

Если хотя бы на одном из входов Ez1 и Ez2 действует логическая 1, то все выходы отключены, т.е. они переведены в высокоимпендансное (третье) состояние.

|

|

|