|

Цифровые счетчики импульсов

|

|

|

|

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

Определение последовательностного цифрового устройства

Цифровое устройство называется последовательностным (ПЦУ); если его выходные сигналы Y зависят не только от значений входных сигналов Хв данный момент времени, но и от значений входных сигналов, поступивших в предшествующие моменты времени. Иными словами, ПЦУ должно отслеживать последовательность поступления входных сигналов для формирования результата на своем выходе. Отсюда очевиден термин «последовательностный». В ПЦУ предыстория поступления входных сигналов обязательно фиксируется с помощью специальных запоминающих элементов. Поэтому говорят, что ПЦУ обладают памятью. Элемент памяти помимо входных и выходных сигналов характеризуется состоянием, которое может изменяться в дискретные моменты времени под воздействием сигналов на его входе. Простейший элемент памяти может принимать одно из двух состояний — логическую единицу или логический нуль. Это состояние может сохраняться сколь угодно долго до тех пор, пока не будет заменено на новое. ПЦУ называются

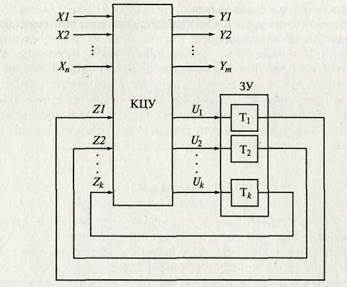

Рис. 1

еще цифровыми автоматами, конечными автоматами или автоматами с памятью. Структура ПЦУ представлена на рис. 1.

ПЦУ состоит из комбинационного цифрового устройства (КЦУ) и запоминающего устройства (ЗУ), представляющее собой совокупность простейших элементов памяти Т1 Т2,..., Тk., на которые воздействуют сигналы U= {U1, U2,..., Uk). Под воздействием сигнала Ui, элемент Тi,- может перейти в одно из двух состояний: логического нуля или логической единицы. Состояние элемента Тi, отображается сигналом Zi,. Совокупность сигналов Z= {Z1, Z2,..., Zk} отображает состояние ПЦУ. Если в ПЦУ содержится k простейших элементов памяти, то общее число состояний ПЦУ равно 2k.

|

|

|

Комбинационное цифровое устройство, входящее в состав ПЦУ, представляет собой устройство, работа которого описывается логическими функциями Y=F(X, Z) и U=H(X, Z). ПЦУ работает под воздействием входных сигналов X, которые поступают в различные моменты времени t. В момент времени t = 0 ПЦУ находится в начальном состоянии. При этом Z(t) = {Z1(t), Z2(t),..., Zk(t)} принимает некоторое начальное значение. При поступлении в моменты времени сигналов Xi(t) в ПЦУ формируются выходные сигналы Yi(t) и сигналы Ui(t), воздействующие на запоминающие элементы. В результате ПЦУ переходит в некоторое состояние Z(t) и тем самым фиксируется воздействие входных сигналов X(t) в момент времени t. Совокупность правил, определяющих последовательность переключения состояний Z(t) и последовательность выходных сигналов Y(t) в зависимости от последовательности входных сигналов X(t), принято называть законом функционирования ПЦУ.

Роль элемента памяти в ПЦУ выполняет триггер, способный фиксировать и хранить значение логического нуля или единицы. Примером простейшего триггера может служить, например, компаратор на базе операционного усилителя. Он формирует на выходе два устойчивых состояния в виде отрицательных и положительных напряжений насыщения в зависимости от того, больше или меньше входное напряжение некоторого заданного порогового уровня. В цифровой технике большее применение нашли триггеры, реализованные на базе логических элементов.

Триггеры

Триггер представляет собой устройство с двумя устойчивыми состояниями. Устойчивым называется состояние, в котором устройство в отсутствии внешних воздействий может прибывать сколько угодно долго. В общем случае триггер имеет два выхода: прямой и инверсный. Состояние триггера принято определять по значению потенциала на прямом выходе. Если на прямом выходе триггера имеется потенциал, равный логической единице, то триггер находится в единичном состоянии (при этом потенциал инверсного выхода равен логическому нулю). В противном случае триггер на-ходится в нулевом состоянии. В основу классификации потенциальных триггеров, в которых имеется связь по постоянному току между входами и выходами, положены два основных признака: функциональный и способ записи информации в триггер.

|

|

|

Функциональная классификация является наиболее общей и представляет собой классификацию триггеров по виду логического уравнения, характеризующего состояния входов и выходов триггера в момент времени до его срабатывания tn и после tn+1. В соответствии с функциональной классификацией различают RS-, D-, T - и JК -триггеры.

Классификация по способу записи информации характеризует временную диаграмму работы триггера, т.е определяет ход процесса записи информации в триггер. По этой классификации триггеры подразделяются на асинхронные и тактируемые. Отличительной особенностью асинхронных триггеров является то, что запись информации в них осуществляется статическим способом, т.е. непосредственно с поступлением информационного сигнала на его вход. Запись информации в тактируемый триггер, имеющий информационные и тактовые входы, осу- ществляется только при подаче разрешающего или тактирующего импульса.

Среди тактируемых триггеров различают триггеры, срабатывающие по уровню (в момент прихода тактирующего сигнала или, что одно и то же, по его переднему фронту), и триггеры с внутренней задержкой, срабатывающие после окончания тактирующего сигнала (по заднему фронту). Такое управление тактируемыми триггерами называется динамическим. Кроме того, тактируемые триггеры подразделяются на однотактные и многотактные в зависимости от числа тактирующих сигналов, необходимых для перевода триггера из одного состояния в другое.

При проектировании устройств с применением триггеров кроме значения функции, выполняемой триггером, необходимо знать его основные схемотехнические параметры:

• минимальная длительность входного сигнала — определяет минимально допустимую длительность входного сигнала, при которой еще происходит переключение триггера из одного состояния в другое;

|

|

|

• максимальная частота переключения триггера определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности.

Закон функционирования триггера удобно отображать с помощью так называемых таблиц переходов, в которых даются состояния входов и выходов триггера до его срабатывания tn и после tn+1, при этом выходное состояние может обозначаться следующим образом:

0 — триггер находится в состоянии Q = 0;

1 — триггер находится в состоянии Q = 1;

Q — состояние триггера не изменяется при изменении информации на входе;

`Q — состояние триггера изменяется на противоположное при изменении информации на входе;

X — неопределенное состояние триггера характеризуется тем, что в процессе действия информационного сигнала на входе логические

уровни выходов триггера одинаковы (Q = `Q = 1 или Q = `Q = 0), а после окончания действия информационного сигнала триггер может оказаться в состояние Q= 1 или Q = 0 с равной вероятностью.

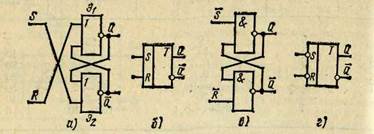

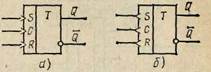

Состояния устойчивого равновесия характеризуются тем, что после слабого внешнего воздействия устройство возвращается в исходное состояние, т. е. токи и напряжения принимают исходные значения в отличие от состояния неустойчивого равновесия, при котором любое слабое внешнее воздействие нарушает это состояние. Для перехода триггера из одного устойчивого состояния в другое необходимо, чтобы входной сигнал превысил пороговое значение. В современной электронике триггеры выполняются, как правило, в виде микросхем, построенных на основе логических элементов. На рис. 2, а, в приведены схемы триггеров на логических элементах ИЛИ —НЕ, И —НЕ, а на рис. 2, б, г показаны их условные обозначения. Допустим, что на входах R и S сигналы равны «0» (R=0, S=0), а на прямом выходе Q сигнал равен «1» (Q=1).Тогда на инверсном выходе `Q сигнал равен «0», так как на одном из вхо-

дов (соединенном с Q) логического элемента ИЛИ — НЕ сигнал равен «1». На обоих входах элемента Э1 сигнал «0», поэтому Q = 1. Очевидно, при R =0, S=0 возможно и второе устойчивое состояние при котором Q=0, `Q=1. Нетоудно видеть, что при S = 1, R=0

|

|

|

Рис. 2

триггер оказывается в первом устойчивом состоянии (Q =l, `Q= 0), а при S=0, R= 1— во втором устойчивом состоянии (Q =0, `Q =1) Комбинация S = l, R = lнедопустима.

Рассмотренный триггер называют RS-триггером. Вход S называется установочным (от англ. set — устанавливать), а вход R входом сброса (от англ. reset — вновь устанавливать). При S=1

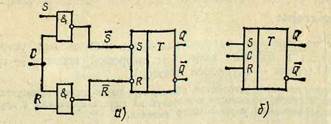

Рис. 3

триггер устанавливается в состояние «1» (Q=l, `Q=0), при R = l

сбрасывается в состояние «0» (Q= 0, `Q= l).

Аналогично работает RS-триггер на элементах И — НЕ (рис. 2, в) с той разницей, что он должен иметь инверсные входы т. е. устанавливаться в состояние «1» При S= 0 и сбрасываться в состояние «0» при R=0. Запрещенная комбинация входных сигнал для этой схемы — «0», «0».

Триггеры можно классифицировать по функциональному признаку и по способу управления. Рассмотренный RS-триггер относится к асинхронным, так как переход его из одного состояния в другое происходит в темпе поступления сигналов на информационные (R, S) входы и не связан с тактовыми сигналами; в синхронных триггерах помимо информационных имеется вход тактовых (синхронизирующих) сигналов и переключения триггера происходят только при наличии тактового сигнала. Синхронный

Рис.4

режим является основным в компьютере, на нем основан принцип действия ряда узлов: D- JK-триггеров, регистров и т.д. На Рис.3 а,б приведены схема и условное обозначение синхронного RS-триггера на элементах И-НЕ, эта схема отличается от схемы асинхронного триггера (см. рис. 2, в) наличием двух дополнительных элементов И —НЕ, благодаря которым управляющие сигналы проходят на входы `R и `Sтолько при «действии на синхронизирующий вход сигнала «1» (С= 1). Для приема информации по одному входу используются D-тиггеры (от англ. delay — задержка). На рис. 4, а, б приведена схема и условное обозначение D-триггера на элементах И — НЕ. D-триггер переходит в состояние «1» (Q= l), если в момент прихода синхронизирующего сигнала (С=1) на его информационный входе сигнал «1» (D = l). В этом состоянии триггер остается и после окончания сигнала на входе D до прихода очередного синхронизирующего Сигнала, возвращающего триггер в состояние «0». Таким образом, D -триггер «задерживает» поступившую на его вход информацию на время, равное периоду синхронизирующих сигналов.

Действительно, при D= l, C= I на выходе `S элемента Э1 сигнал «О» (`S=0), а выходе Э2 — «1» (`R = 1) [так как на его входах «1» и «0»; рис. 4, а].Так как RS-триггер имеет инверсные входы, то при `S=0, `R == 1 он переходит в состояние (Q= l, `Q=0) и остается в этом состоянии до тех пор, пока при D=0 не получится С=1. В этом случае `S==l, `R=0 и триггер возвращается в состояние «0» (Q=0, `Q=l). При D=0, `S=l и независимо от С¾ Q=0.

|

|

|

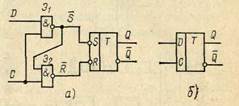

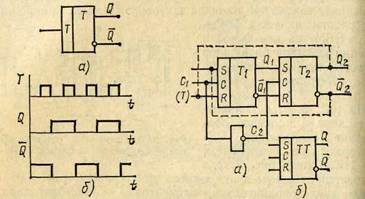

T-триггер (от англ. tumble—-опрокидываться, кувыркаться), или счетный триггер, имеет один информационный вход и переходит в противоположное состояние в результате воздействия на его вход каждого очередного сигнала. Название «счетный» (или «со счетным запуском») связано с широким применением Т-триггеров в счетчиках импульсов. На рис. 5, а, б приведены условное обозначение и временные диаграммы Т-триггера.

Т-триггеры выполняют на основе двух последовательно соединенных.RS-триггеров (MS-схема), первый из которых называют

ведущим (от англ. master — хозяин), а другой— ведомым (от англ.

slave_ раб). На рис. 6, а, б приведены схемы и условное обо-

значение MS-триггера (двухступенчатого триггера), в которое, триггер Т1— ведущий, а триггер Т2— ведомый. При поступлении

Рис. 5 Рис. 6

сигналов на информационные входы Rили S триггера Т1 он принимает соответствующее состояние («0» или «1») в момент, когда с Ci=l. Сигналы с выходов Q1; `Q1ведущего триггера не проходят

Рис. 7

в ведомый, поскольку С2=0. Информация пройдет в ведомый триггер только по окончании синхронизирующего сигнала (C1=0, С2 = 1) и будет отображена на выходах Q2, `Q2.

Для получения двухступенчатого Т-триггера достаточно ввести обратные связи (на рис. 6, а показаны пунктиром) и использовать вход С1как информационный (Т). Тогда при Т = 1 триггер Т1 устанавливается в состояние, противоположное состоянию триггера Т 2 (например, при Q2=0, `Q2 = l — в состояние Q1=l, `Q1==0). а, при Т=0 триггер Т2 переходит в состояние, совпадающее с состоянием триггера Т1(Q2 = l, `Q2=0). Таким образом, на выходах Q2, `Q2 сигнал изменяется на противоположный по окончании каждого очередного импульса Т, что соответствует диаграмме рис. 5, б

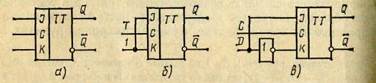

Универсальный триггер, или J К-триггер, имеет информационные входы J и К и синхронизирующий вход С (рис. 7, a). JK- триггер получают из двухступенчатого Т-триггера путем использования трехвходовых элементов И — НЕ во входных цепях ведущего триггера подобно тому, как используют двухвходовые элементы И— НЕ в схеме рис. 3, а. Использование третьих входов элементов И — НЕ позволяет реализовать два дополнительных ин-

Рис. 8

формационных входа: J и K. (Рис.7а) При J=K=1 триггер изменяет свое состояние на противоположное в момент окончания синхронизирующего сигнала. Таким образом, соединяя входы JK – триггера по схеме рис.7 б Получают Т-триггер. Используя вход J как вход S, а К— как R, реализуют синхронный RS-триггер, особенность которого состоит в том, что при комбинации S=R = l,запрещенной для обычного RS-триггера, он переключается на каждый синхронизирующий сигнал. Добавлением инвертора на входе JK-триггера получают D-триггер (рис. 7, в).

Все типы триггеров, реализуемые на основе JK-триггера, дают задержку в появлении выходных сигналов, равную длительности синхронизирующего сигнала.

Рассмотренные триггеры относятся к статическим триггерам, реагирующим на уровни входных сигналов. Существуют также динамические триггеры, которые реагируют на перепады уровней сигналов. На рис. 8, а приведено условное обозначение синхронного RS-триггера, реагирующего на перепад уровня сигнала от «0» к «1», а на рис. 8, б — то же, для триггера, реагирующего на перепад от «1» к «0». В первом случае входы называют прямыми динамическими, во втором — инверсными динамическими.

Наибольшее распространение получили статические JK - и D-триггеры, выполняемые в виде интегральных микросхем, например К155ТМ5 (4 D-триггера), К176ТВ1 (2 JK-триггера).

Цифровые счетчики импульсов

Цифровым счетчиком импульсов называют устройство, реализующее счет числа входных импульсов и фиксирующее это число в каком-либо коде. Обычно счетчики строят на основе триггеров, поэтому счет импульсов ведется в двоичной системе счисления.

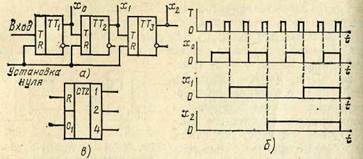

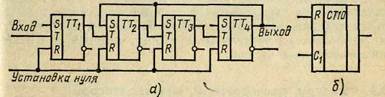

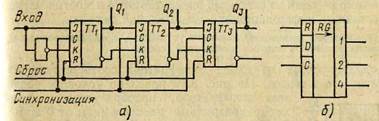

Функциональная схема простейшего двоичного трехразрядного цифрового счетчика импульсов приведена на рис. 9, а. Счетчик состоит из трех последовательно соединенных Т-триггеров, имеющих вход R для установки в состояние «0».

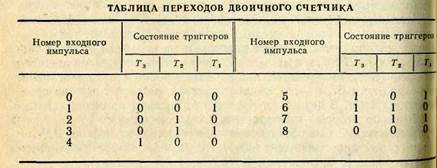

На рис. 9, б показаны временные диаграммы счетчика. Табл. 1

иллюстрирует состояние триггеров. Если в исходном положении

все триггеры были в состоянии «0», то по окончании первого вход-

ного импульса триггер Т1 перейдет в состояние «1» (хо=1). по

Рис. 9. Схема (а), временные диаграммы (б) к условное обозначение (в) двоичного трехразрядного счетчика

окончании второго входного импульса триггер Ti переходит в состояние «0» (хо=0). По окончании импульса х0 триггер Т2 переходит в состояние «1» (х1=1) и т. д. После восьмого входного импульса все триггеры переходят в состояние «0» и счет повторяется.

Табл. 1

Из табл. 1 видно, что состояние триггеров отражает число поступивших на вход счетчика импульсов в двоичной системе счисления (двоичном коде). Общее число возможных состояний (модуль) N счетчика определяют числом триггеров п: N=2n. В нашем случае N=8.

Условное обозначение счетчика по схеме рис. 9, а приведина рис. 9, в: СТ2 означает двоичный счетчик; выходы 1, 2, 4обозначения двоичных разрядов (20 = 1, 21=2, 22=4), соответствующих выходам х0, х1, х2 схемы рис. 9, a; С1 — счетный вход; R- установка нуля.

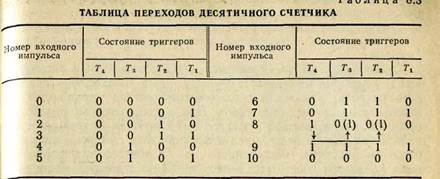

Табл. 2

Для получения счетчика, работающего в другом коде, например десятичном, применяют обратные связи. На рис. 10, а приведена функциональная схема десятичного (декадного) счетчика импульсов на четырех триггерах, а на рис. 10, б — его условное обозначение.

Для получения счетчика, работающего в другом коде, например десятичном, применяют обратные связи. На рис. 10, а приведена функциональная схема десятичного (декадного) счетчика импульсов на четырех триггерах, а на рис. 10, б — его условное обозначение.

Рис. 10. Схема (а) и условное обозначение (б) десятичного счетчика

С выхода триггера Т4 сигналы обратной связи поступают на входы триггеров Т2, Т3. Благодаря этому после поступления на вход счетчика восьмого импульса на выходе триггера Т4 появляется сигнал «1», который переводит триггеры Т3, Т2 из состояния «0» в состояние «1» (табл. 2).

Девятый импульс переводит триггер T1 в состояние «1», и все

триггеры оказываются в состоянии «1». Десятый импульс переводит все триггеры в состояние «0», и счет начинается снова. Используя обратные связи, можно построить счетчик, работающий в системе счисления с любым основанием.

Рассмотренные счетчики выполняют операцию суммирования Числа импульсов, поступивших на вход, поэтому их называют суммирующими. Для построения вычитающего счетчика можно соединять последовательно не прямые (как в схеме рис. 9, а), а инверсные выходы триггеров. Такой счетчик работает следующим образом.

Вначале все триггеры устанавливают в состояние «1» (при трех триггерах это соответствует двоичному числу 111). Поступивший на вход счетчика импульс переводит триггер Т1 в состояние «0», а состояние остальных триггеров не изменяется. Следовательно, в счет-

чике будет записано двоичное число 110. Следующий входной импульс уменьшает число еще на одну единицу и т. д.

Счетчики, выполняющие операции сложения и вычитания, называют реверсивными. Обычно они имеют два входа: сложения и вычитания.

Описанные счетчики относятся к последовательным (асинхронным), у которых импульсы поступают только на вход триггера первого разряда, а каждый. последующий триггер управляется входным сигналом предыдущего. Для повышения быстродействия применяют параллельные (синхронные) счетчики, в которых входной сигнал воздействует параллельно на входы синхронизации всех разрядов счетчика, построенного на JK-триггерах. Использованием JK-входов добиваются необходимой последовательности переключения триггеров.

Счетчики выполняют в виде интегральных микросхем, например К176ИЕ1 (шестиразрядный двоичный счетчик), К176ИЕ2 (пятиразрядный счетчик), К.155ИЕ4 (счетчик-делитель на 12).

Цифровые счетчики импульсов применяют для счета числа импульсов либо для деления числа импульсов. Счет числа импульсов, поступающих на вход с высокой частотой, необходим в вычислительной технике, автоматике, информационно-измерительной технике (цифровые измерительные приборы), ядерной физике (счетчики элементарных частиц).

Регистры

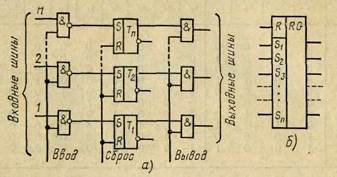

Регистром * называют устройство, предназначенное для записи и хранения дискретного «слова» — двоичного числа или другой кодовой комбинации. ( * От англ. register — журнал записей.)

Основные элементы регистра — двоичные ячейки, в качестве которых применяются триггеры. Число двоичных ячеек определяется числом двоичных разрядов «слова» (длиной слова), на которое рассчитан регистр.

На рис. 11, а, б приведены схема и условное обозначение n- разрядного регистра на RS-триггерах. Информация в ячейки регистра записывается по команде «Ввод» («1» на входе «Ввод»). Тогда сигналы п входов установят в соответствующие состояния триггеры T1 — Тп. На выходе регистра информация появится по команде «Вывод», в ее отсутствие на выходах — нули. При считывании информация, записанная в регистре, сохраняется.

Описанный регистр может запоминать и выдавать информацию только в параллельных кодах, когда каждому разряду соответствует отдельная линия. Более экономична передача информации в последовательных кодах, когда используется одна линия дляпоследовательной (во времени) передачи комбинации нулей и единиц. Для записи и хранения информации в последовательных кодах применяют сдвигающие (сдвиговые) регистры. На рис. 12, а,б приведены схема и условное обозначение сдвигающего регистра на JK-триггерах ( MS- типa ). Здесь информация, поступившая на

Рис. 11. Схема (а) и условное обозначение (б) регистра

информационный вход, по окончании каждого синхронизирующего импульса передается («продвигается») из предыдущего триггера в последующий.

Рис. 12. Схема (а) и условное обозначение (б) сдвигающего регистра с последовательным вводом информации

Рассмотрим работу регистра по схеме рис. 12, а. Пусть требуется записать в регистр трехразрядное двоичное слово D= 101, имеющее разряды D1=1, D2=0, D3=l (D=D1|D2|D3|).При С=1 в триггер T1 вводятся J1=D1=lи K1=D1=0. Поскольку.JK-триггер с раздельными входами работает как синхронный RS-триггер, по окончании синхронизирующего (тактового) импульса (при переходе от С=1к С=0) на выходе триггера Т2появляется Q1=1.Следовательно, по окончании первого тактового импульса Ql=D1=l, `Q1=`D1=0.

Затем на информационный вход регистра поступает второй разряд D2=0 слова D. При воздействии второго тактового импульса триггер Т2воспримет информацию с выхода первого триггера: J2=Q1=1, `Q2=`D1=0- По окончании второго тактового импульса Q2=D2=1 `Q2 = `D1=0, а первый триггер воспримет входную информацию регистра и на его выходе Q1=D2=0, `Q1=`D1= 1. Таким образом, произошел сдвиг информации из первого разряда регистра во второй; точно так же по окончании третьего тактового импульса Q3=D1=1, Q2=D2=0 Q1=D1=lи все слово записано в регистр.

Считывать информацию из сдвигающего регистра можно либо в последовательном коде с выхода Q3, продвигая информацию через все разряды регистра к выходу, либо в параллельном коде одновременно с выходов Q1, Q2, Q3.

Заметим, что существуют регистры сдвига с параллельным вводом информации.

Регистр — один из основных элементов компьютера и многих устройств автоматики и информационно-измерительной техники.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1 Что такое ПЦУ?

2 Как классифицируются триггеры?

3 Сколько разрядов имеет десятичный счетчик?

4 Что такое регистр?

5 Как на базе суммирующего счетчика реализовать вычитающий?

|

|

|