|

Пространство памяти ввода/вывода

|

|

|

|

В процессорах Blackfin не определено отдельное пространство ввода/вывода. Все ресурсы отображены в 32-разрядномадресном пространстве. Регистры управления внутренних устройств ввода/вывода отображены в карте памяти по адресам, расположенным в верхней части4-гигабайтного адресного пространства. Они разделены на два блока меньшего размера: один из блоков содержит регистры управления всеми функциями ядра, а другой содержит регистры, необходимые для настройки и управления, внутренними периферийными устройствами, располагающимися вне ядра. Регистры, отображённые в карте памяти доступны только в режиме Супервизора. Они представляют собой выделенное пространство внутренних периферийных устройств.

Периферийные устройства

Периферийные устройства системы процессора включают:

•Параллельный периферийный интерфейс (PPI)

•Последовательные порты (SPORT)

•Последовательный периферийный интерфейс (SPI)

•Таймеры общего назначения

•Универсальный асинхронный приёмник-передатчик(UART)

•Часы реального времени (RTC)

•Сторожевой таймер

•Порт ввода/вывода общего назначения (программируемые флаги)

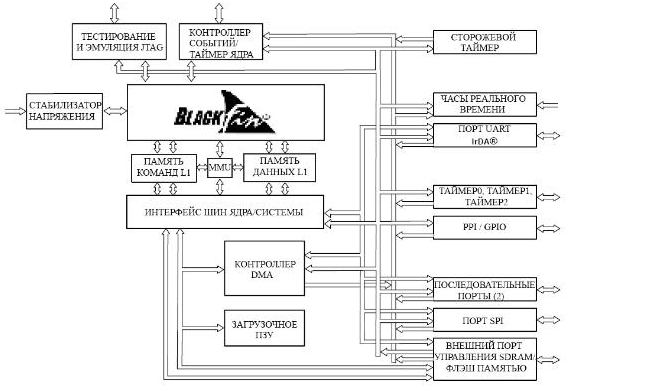

Эти периферийные устройства соединены с ядром несколькими шинами с высокой пропускной способностью, как показано на рис.3

.

Рис. 3.Блок-схемапроцессора

Периферийные устройства, за исключением порта ввода/вывода общего назначения, часов реального времени и таймеров, поддерживаются гибкой структурой прямого доступа к памяти (DMA). Также в процессоре имеются два отдельных канала DMA типа “память-память”,предназначенные для осуществления передач между пространствами памяти процессора, включая внешнюю SDRAM и асинхронную память. Набор внутренних шин обеспечивает пропускную способность, достаточную для поддержания работы ядра процессора, даже если задействованы все внутренние и внешние периферийные устройства.

|

|

|

Процессоры Blackfin поддерживают модифицированную Гарвардскую архитектуру с иерархической структурой памяти. Память уровня 1 (L1) обычно работает с полной скоростью процессора с небольшой задержкой или без задержки. Память команд на уровне L1 содержит только команды. Две памяти данных содержат данные, а выделенная сверхоперативная (блокнотная) память хранит информацию стека и локальные переменные.

Процессор имеет несколько блоков памяти L1, которые могут быть сконфигурированы как смешанный набор SRAM и кэша. Устройство управления памятью (MMU, Memory Management Unit) обеспечивает защиту памяти при выполнении ядром индивидуальных задач и может осуществлять защиту системных регистров от непреднамеренного доступа.

Архитектура процессора обеспечивает три режима работы: Пользовательский режим, режим Супервизора и режим Эмуляции. В Пользовательском режиме доступ к поднабору ресурсов системы ограничен, что обеспечивает организацию защищённой программной среды. В режимах Супервизора и Эмуляции доступ к ресурсам ядра и системы неограничен.

Набор команд процессора ADSP-BF53xBlackfin оптимизирован таким образом, что наиболее часто используемые команды представлены16-разряднымикодами. Комплексные команды цифровой обработки сигналов (ЦОС) кодируются 32разрядными кодами как многофункциональные команды. В продуктах семейства Blackfin реализована ограниченная поддержка многозадачности, которая заключается в возможности параллельного вызова32-разряднойкоманды и двух 16-разрядныхкоманд. Это позволяет программисту использовать многие ресурсы ядра в одном командном цикле.

В языке ассемблера процессора ADSP-BF53xBlackfin используется алгебраический синтаксис. Архитектура оптимизирована для использования совместно с компилятором языка С.

|

|

|

SRAM команд L1

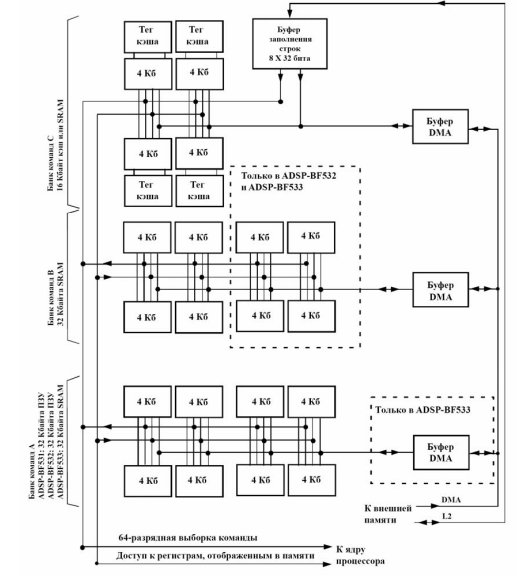

Ядро процессора производит чтение памяти команд по 64-разрядной шине выборки команд. Все адреса на этой шине выровнены по границе 64-х разрядов. В каждой выборке может возвращаться любая комбинация 16-, 32- или 64- разрядных команд (например, четыре 16-разрядные команды, две 16-разрядные и одна 32-разрядная команда или одна 64-разрядная команда). Прямое обращение генераторов адреса данных, описываемых в главе 5, к памяти команд L1 невозможно. Обращение DAG к пространству памяти команд SRAM генерирует исключение (см. раздел «Исключения» в главе 4). Доступы записи к памяти команд SRAM L1 должны выполняться с помощью 64- разрядного порта DMA системы. Так как SRAM реализована как набор однопортовых подуровней банка памяти, в действительности память команд работает как двухпортовая память.

В таблице 6-2 перечислены начальные адреса подуровней банков памяти команд L1.

Архитектура банка памяти команд L1 представлена на рис. 6-3. Как показано на рисунке, каждый 16 Кбайтный банк состоит из четырех подуровней, объёмом по 4 Кбайта.

Кэш команд L1

Информацию о терминологии, касающейся кэша, см. в разделе «Терминология». Память команд L1 также может быть сконфигурирована таким образом, чтобы содержать 4-входовый наборно-ассоциативный кэш объёмом 16 Кбайт. Каждый вход или строка кэша может независимо запираться, что позволяет улучшить среднее время задержки обращения для частей программы, критичных ко времени. Когда память сконфигурирована как кэш, прямое обращение к ней невозможно. Когда кэш разрешен, возможно кэширование только тех страниц памяти, которые определяются как кэшируемые в CPLB. Когда разрешено использование CPLB, любой ячейке памяти, к которой выполняется обращение, должно соответствовать определение атрибутов в CPLB, в противном случае генерируется исключение CPLB. CPLB описывается в разделе «Свойства и защита памяти».

На рис. 6-3 показана общая организация кэша команд процессора Blackfin.

Рис. 6-3. Архитектура банка памяти команд L1

СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

http://www.studfiles.ru/

http://microsin.net/programming/dsp/blackfin-booting-process.html

http://www.kit-e.ru/

https://en.wikipedia.org

|

|

|