|

Современные и перспективные ИС со сложными программируемыми структурами

|

|

|

|

Размеры плат микро-PC составляют всего 114×124 мм, поэтому для создания крупных систем нужно использовать микросхемы высокой степени интеграции и стараться разметить всю схему в минимальное число корпусов элементов.

Наряду со стандартными, в системе накопления, как и в любой другой системе, присутствуют и нестандартные части, специфичные для данной разработки. Это могут быть различные схемы управления, схемы реализации заданного алгоритма и т.п. Процесс реализации нестандартной части устройства, как правило, связан применением микросхем малой и средней степени интеграции. Применение малых и средних ИС неизбежно приводит к росту числа корпусов ИС, усложнением монтажа и отладки, снижением быстродействия и надёжности схем. Заказать для системы специализированные ИС высокого уровня интеграции затруднительно, т.к. это связано с большими затратами средств и времени. Существующее противоречие может быть разрешено путём применения современных программируемых логических интегральных схем [7].

Первыми представителями программируемых ИС явились программируемые логические матрицы ПЛМ, программируемая матричная логика ПМЛ и базовые матричные кристаллы БМК, называемые также вентильными матрицами. ПМЛ и ПЛМ в английской терминологии часто объединяются термином PLD, Programmable logic Devices.

Развитие БИС/СБИС с программируемой и репрограммируемой логикой оказалось настолько перспективным направлением, что привело к созданию новых эффективных средств разработки цифровых систем, таких

как CPLD (Complex PLD), FPGA (Field Programmable Gate Array) и SPGA (System Programmable Gate Array).

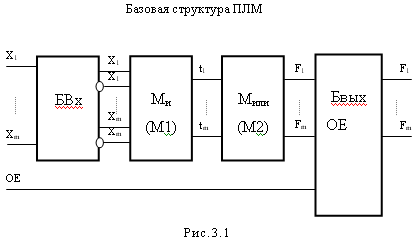

Основой программируемых логических матриц служит последовательность элементов И и ИЛИ. В структуру также входят блоки входных и выходных буферных каскадов (рис. 3.1)

|

|

|

Входные буферы, как правило, предназначены для преобразования однофазных входных сигналов в парафазные и формирования сигналов необходимой мощности для питания матрицы элементов И.

Выходные буферы обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают выход ПЛМ на внешние шины с помощью сигнала OE, а иногда выполняют и более сложные действия.

Переменные x1…xm подаются через входные буферные каскады на входы элементов И, и в матрице И образуют L термов. Терм – это конъюнкция, связывающая входные переменные, представленные в прямой или инверсной форме. Число формируемых термов равно числу выходов матрицы И.

Термы подаются далее на входы матрицы ИЛИ, т.е. на входы дизъюнкторов формирующих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций N. Воспроизводимые функции являются комбинациями из любого числа термов, формируемых матрицей И. Какие именно термы будут выработаны и какие комбинации этих термов составят входные функции, определяется программированием. Таким образом, ПЛМ способна реализовать систему N логических функций от M аргументов, содержащую не более L термов.

Принцип программирования основан на том, что в матрицах имеются системы горизонтальных и вертикальных связей, в узлах которых при программировании создаются или ликвидируются связи. В качестве узлов связей используются диоды. До программирования все перемычки целы и диоды связи размещены во всех узлах координатной сетки. При программировании в схеме остаются только необходимые элементы связи, а ненужные устраняются пережиганием перемычек.

Логическая мощность ПЛМ зачастую используется не полностью. Это проявляется, в частности, при воспроизведении типичных функций, не имеющих больших пересечений друг с другом по одинаковым термам. В таких случаях возможность использования выходов любых конъюнкторов любыми дизъюнкторами становится излишним усложнением. Отказ от этой возможности означает использование не программируемой, а заданной матрицы ИЛИ. Структура в которой выходы матрицы И жёстко распределены между элементами ИЛИ получила название ПМЛ. В сравнении с ПЛМ схемы ПМЛ имеют меньшую гибкость, т.к. матрица ИЛИ фиксирована, но их изготовление дешевле и использование проще.

|

|

|

Отдельной ветвью в развитии программируемых интегральных схем являются базовые матричные кристаллы (вентильные матрицы с масочным программированием). Основа первых БМК – совокупность регулярно расположенных на кристалле базовых ячеек (БЯ), между которыми имеются свободные зоны (каналы) для создания соединений. БЯ занимают внутреннюю область БМК, в которой они расположены по столбцам, и содержат группы нескоммутированных элементов (транзисторов, резисторов и др.). В периферийной области размещены ячейки ввода-вывода. Потребитель может реализовать на основе БМК некоторое множество устройств определённого класса, задав тот или иной вариант рисунка межсоединений компонентов. Основной характеристикой БМК помимо числа эквивалентных вентилей является трассировочная способность, которая определяется площадью отводимой для межэлементных связей в ортогональных направлениях. Недостаточная трассировочная способность приводит к уменьшению числа задействованных при построении базовых ячеек. Избыточная трассировочная способность ведёт к нерациональному использованию кристалла, что понижает уровень интеграции БМК и повышает его стоимость. Для решения подобных проблем строятся многослойные БМК, при этом число слоёв межсоединений может составлять от 2 до 6 и более.

Ранее перечисленные архитектуры ПЛИС, содержащие небольшое количество ячеек, к настоящему времени морально устарели и применяются для реализации относительно простых устройств, для которых не существует готовых ИС средней степени интеграции [8]. Для реализации крупных проектов они не пригодны.

Развитие технологий, опыт использования программируемых интегральных логических схем (ПЛИС) приводит к выводу, что это максимально удобная в освоении и применении элементная база, альтернативы которой зачастую не найти. Последние годы характеризуются резким ростом плотности упаковки элементов на кристалле, многие ведущие производители либо начали серийное производство, либо анонсировали ПЛИС с эквивалентной ёмкостью более одного миллиона эквивалентных вентилей на кристалл.

|

|

|

Современные ПЛИС классифицируются по конструктивно-технологическому типу программируемых элементов. Число программируемых двухполюсников (программируемых точек связи ПТС) в ПЛИС зависит от сложности и может доходить до нескольких миллионов. Наиболее характерны следующие виды программируемых ключей:

- перемычки типа antifuse

- ЛИЗМОП транзисторы с двойным затвором

- ключевые транзисторы, управляемые триггерами памяти конфигурации (теневым ЗУ) [7].

Программирование с помощью перемычек antifuse является однократными. Высококачественные перемычки фирмы Actel компактны, имеют очень малые токи в первоначальном (непроводящем) состоянии (порядка10-15А). Перемычка образована трёхслойным диэлектриком с чередованием слоёв оксид-нитрид-оксид. Программирующий импульс напряжения пробивает перемычку и создаёт проводящий канал из поликремния между электродами. Величина тока, создаваемого импульсом программирования, влияет на диаметр проводящего канала (например ток 5 мА создаёт перемычку с сопротивление 600 Ом, ток 15мА – 100 Ом) [7].

Элементы EPROM и EEPROM на ЛИЗМОП (МОП-структуры с лавинной инжекцией заряда) транзисторах с плавающих затвором используются в ПЛИС, где с помощью программируемой памяти задаётся конфигурация схемы. Стирание старой конфигурации в ПЛИС на основе EPROM требует длительного (около 1 часа) облучения УФ-излучением. Такие микросхемы имеют ограничение количества циклов перепрограммирования из-за деградации свойств полупроводниковых материалов под воздействием ультрафиолета. Технология EEPROM, для обновления не требует извлечения микросхемы, допускает достаточно большое число циклов стирания (104…106). Процесс стирания и обновления конфигурации занимает время порядка миллисекунд. В последнее время схемотехника EEPROM совершенствуется и всё больше вытесняет схемотехнику EPROM. Технология программируемой памяти применяется в ПЛИС типа CPLD.

|

|

|

В качестве программируемого элемента связи в ПЛИС FPGA используется транзисторный ключ, управляемый триггером, показанный на рис.3.2

В качестве программируемого элемента связи в ПЛИС FPGA используется транзисторный ключ, управляемый триггером, показанный на рис.3.2

Ключевой транзистор Т2 замыкает или размыкает участок АВ в зависимости от состояния триггера. При программировании на линию выборки подаётся высокий потенциал, и транзистор Т1 включается. С линии записи-чтения подаётся сигнал, устанавливающий триггер в состояние «1» и «0».

Загрузка соответствующих данных в память конфигурации программирует ПЛИС. Быстрый процесс оперативного программирования может производиться неограниченное число раз. При выключении питания конфигурация теряется. Каждый раз при включении питания необходим процесс инициализации (конфигурирования) схемы - загрузка данных из энергонезависимой памяти [1].

ИС класса ПЛМ и ПМЛ имеющие структуру весьма удобную для построения цифровых автоматов положили начало развития архитектуры программируемых коммутируемых матричных блоков (ПКМБ), которые представляют собой ПЛИС содержащую несколько матричных логических блоков, объединённых коммутационной матрицей. ПЛИС типа ПКМБ, как правило, имеют высокую степень интеграции (до 10 тыс. эквивалентных вентилей). К этому классу относятся ПЛИС семейства MAX5000, MAX7000 фирмы Altera, схемы XC7000, XC9500 фирмы Xilinx и др. ПЛИС класса ПКМБ в зарубежной литературе получили название CPLD (Complex PLD).

Архитектурно CPLD состоят из центральной коммутационной матрицы, множества функциональных блоков ФБ (макроячеек) и блоков ввода-вывода на периферии кристалла. Система коммутации построена на основе непрерывных связей, что даёт хорошую предсказуемость задержек сигналов в связях. Программируемая матрица соединений (PIA) позволяет соединить выход любого ЛБ с входами других и обеспечить связи с вертикальными и горизонтальными линиями. Как и во всех ПЛИС, логические операции производятся в ЛБ, которые соединяются в единую систему с помощью ПМС. Каждый ЛБ содержит 16 макроячеек. Классическим представителем CPLD являются микросхемы семейства MAX7000, фирмы Altera, имеющими память конфигурации типа EEPROM. В настоящее время выпускаются ПЛИС MAX7000, MAX7000A, MAX7000B, MAX7000E, MAX7000S. Семейства MAX7000A и MAX7000B рассчитаны на работу в системах с напряжением питания 3,3 и 2,5В соответственно, ПЛИС MAX7000S является дальнейшим развитием 5-вольтового MAX7000, с возможностью программирования в системе (ISP, In-system programmability) и периферийного сканирования в соответствии со стандартом IEEE Std. 1194.1 JTAG. Фрагмент структуры CPLD MAX7000S дающий достаточно полное представление о ней изображён на рисунке 3.3а.

|

|

|

В отличие от архитектуры MAX7000 ПЛИС MAX7000S имеют дополнительную возможность использования двух глобальных тактовых сигналов GCLK1 и GCLK2 и сброса GCLR, а также сигналы разрешения выходов ОЕ.

Логический блок обеспечивает построение как комбинационных цепей, так и схем с элементами памяти. Одна из макроячеек логического блока изображена на рисунке 3.3б.

При недостатке собственных термов внутри макроячейки, можно воспользоваться дополнительными ресурсами двух типов логических расширителей общего (разделяемого) и параллельного.

Блок ввода-вывода даёт возможность гибкого управления разрешением выходного буфера. ПМС формирует глобальные сигналы разрешения выходов ОЕ, допуская возможность перевода выходов ПЛИС в третье состояние. ПЛИС MAX7000S поддерживают аппаратную эмуляцию выходов с открытым коллектором, кроме того, может программироваться и скорость изменения выходов сигналов с целью предупреждения возможных паразитных колебаний при переключении.

Продолжением линии БМК стали программируемые пользователем вентильные матрицы ППВМ (FPGA). Логические блоки таких ПЛИС состоят из одного или нескольких относительно простых логических элементов (коммутируемых логических блоков КЛБ), в основе которых лежит таблица перекодировки, программируемый мультиплексор, D-триггер и цепи управления. Таких простых элементов может быть достаточно большое количество (у современных ПЛИС ёмкостью до 1 миллиона вентилей число логических элементов достигает нескольких десятков тысяч). Таким образом, архитектуру ППВМ можно представить в виде структуры БМК, где вместо базовых ячеек находятся КЛБ. В английской терминологии данный класс микросхем называется FPGA (Field Programmable Gate Array). К наиболее известным FPGA относятся ПЛИС семейства XC2000, XC3000, XC4000, XC5000 и Spartan, Virtex фирмы Xilinx, ACT1,ACT2 фирмы Actel, а также семейства FLEX8000 фирмы Altera, некоторые ПЛИС Atmel и Vantis [8].

В качестве КЛБ могут использоваться:

- транзисторные пары, простые логические вентили и т.п.

- логические модули на основе мультиплексоров

- логические модули на основе программируемых ПЗУ

Наиболее важные характеристики КЛБ отражаются двумя параметрами зернистость и функциональность.

Первое свойство связано с тем, какие минимальные единицы логики (транзистор, вентиль, логический модуль) можно применить для составления нужной схемы. Второе свойство показывает насколько велики логические возможности КЛБ. Т.о. оба параметра взаимопротивоположны. Мелкозернистые ЛБ фирмы Crosspoint Solution содержат цепочки транзисторов. Между цепочками транзисторов имеются трассировочные каналы, в которых могут быть реализованы необходимые межсоединения. Крупнозернистый блок в микросхемах XC4000E фирмы Xilinx в качестве основы имеет три функциональных логических преобразователя, ряд программируемых мультиплексоров и два триггера. Такой блок способен реализовать более сложные функции, что ведёт к упрощению программируемой части межсоединений. Иными словами, меняя зернистость можно выиграть в одном и проиграть в другом.

Системы межсоединений, как и логические блоки, реализуются в широком диапазоне архитектурных и технологических решений. Линии связи в FPGA как правило сегментированы, т.е. составлены из сегментов различной длины, соединённых программируемыми связями.

Короткие сегменты затрудняют реализацию длинных связей, длинные – коротких. Поэтому применяют иерархическую систему связей с несколькими типами межсоединений для передачи на разные расстояния, такое решение позволяет строить системы с максимальной коммутируемостью КЛБ при минимальном количестве ключей и задержки сигналов, а также предсказуемость последних, что облегчает программирование [7].

Критерий трассировочной способности системы межсоединений отображает возможность создания в FPGA множества схем типового применения (только с помощью программируемых перемычек).

Объединение достоинств FPGA и CPLD привело к созданию ПЛИС смешанной архитектуры (общего названия для этого типа ПЛИС пока не придумано, фирма Altera пользуется термином Field Programmable Gate Arrays FLEX). Микросхемы FLEX содержат реконфигурируемые модули памяти РМП. Впервые такая встроенная память появилась в семействе FLEX

10K [7] (рис.3.4).

Логические элементы (ЛЭ) объединяются в группы – логические блоки. Внутри логических блоков ЛЭ соединяются посредством глобальной программируемой матрицы соединений. Локальная и глобальная матрицы соединений имеют непрерывную структуру – для каждого соединения выделяется непрерывный канал.

Дальнейшее развитие архитектур идёт по пути создания комбинированных архитектур, сочетающих удобство реализации оперативно реконфигурируемых систем, характерных для FPGA структур и многоуровневых ПЛИС с удобством реализации цифровых автоматов на CPLD архитектурах. В продукции наиболее известных производителей ПЛИС можно выделить микросхемы APEX 20K/KE (рис.3.5) фирмы Altera и Virtex фирмы Xilinx. Стоит отметить, что при всех своих достоинствах такие ПЛИС пока мало популярны из-за высокой стоимости [7].

В таких микросхемах уровень интеграции доведён до нескольких миллионов эквивалентных вентилей, а быстродействие до тактовых частот 500…600 МГц. На таких кристаллах можно поместить целую систему (в зарубежной литературе принят термин System-On-Chip, SOC), включающую процессорную часть, память, интерфейсные схемы и др.

Компоненты этих систем разрабатываются отдельно и хранятся в виде файлов параметризованных модулей. На базе таких виртуальных компонентов с помощью систем автоматизированного проектирования электронных устройств EDA (Electronic Design Automation) создаётся окончательная структура SOC-микросхем.

|

|

|