|

Прототипные платы схем программируемой логики с интерфейсом PCI

|

|

|

|

Прототипные платы программируемой логики с интерфейсом PCI позволяют отлаживать широкий круг пользовательских проектов, ориентированных на БИС PLD FLEX10K.

Рис.3 Прототипные платы

| Семейство в своей основе содержит: · три схемы программируемой логики; · четыре БИС сверхоперативной памяти (цикл обращения не более 15 нсек). По функциональному назначению схемы PLD распределяются: · интерфейсная БИС типа FLEX10K - EPX10K30QC240-3; · системная БИС типа FLEX10K - EPX10K30ATC144-4, · управляющая БИС типа MAX7000S - EPM128STC100-6. |

Особенности реализации:

· допустимость отладки больших и сложных пользовательских проектов до 60 тысяч вентилей;

· возможность использования в проектах встроенных сверхоперативных блоков ОЗУ;

· возможность использования в проектах блоков ОЗУ большой емкости (до 128K 32-разрядных слов);

· обеспечение простоты и легкости смены пользовательских проектов, загружаемых в системную БИС через интерфейсную БИС;

· отсутствие ограничений на количество циклов реконфигурирования;

· обеспечение загрузки конфигурации интерфейсной БИС из схемы постоянной загрузочной памяти;

· возможность закрытия битом секретности доступа к содержимому внутреннего ОЗУ платы.

Платы разработчика для схем программируемой логики с интерфейсом PCI

Платы разработчика для схем программируемой логики с интерфейсом PCI позволяют отлаживать широкий круг пользовательских проектов, ориентированных на БИС PLD ACEX.

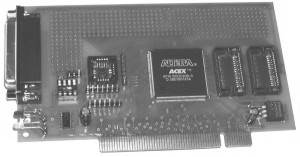

Рис. 3 Плата программируемой логики с интерфейсом PCI

Семейство в своей основе содержит:

· схему программируемой логики;

· две БИС сверхоперативной памяти (цикл обращения не более 15 нсек).

Особенности реализации:

|

|

|

· допустимость отладки больших и сложных пользовательских проектов до 100 тысяч вентилей;

· возможность использования в проектах встроенных сверхоперативных блоков ОЗУ;

· возможность использования в проектах блоков ОЗУ большой емкости (до 128K 16-разрядных слов);

· обеспечение простоты и легкости смены пользовательских проектов, загружаемых в БИС;

· наличие монтажной зоны для размещения ИС пользователя;

· возможность использования дополнительных плат по мезонинной технологии;

· обеспечение загрузки конфигурации БИС из схемы постоянной загрузочной памяти.

Оборудование для контроля и отладки проектных плат

Оборудование для контроля и отладки проектных плат с интерфейсом по стандарту ISA или PCI представляют собой платы-удлинители для соответствующих интерфейсных плат, у которых каждая линия интерфейса имеет соединение с контролирующей БИС PLD.

Рис. 4 Оборудование для контроля и отладки проектных плат

Если ИС проектируемой платы поддерживают граничное сканирование (BST) через JTAG интерфейс, то разработанное на кафедре ПО позволит с помощью платы отладчика до установки разрабатываемой платы в ПК найти ошибки как в межсоединениях этих ИС между собой, так и в их соединениях с разъемом компьютера. Та же плата отладчика с другим вариантом ПО позволяет имитировать поведение любой мыслимой и немыслимой комбинации управляющих сигналов интерфейсной шины.

Плата отладчика может оказать существенную помощь разработчику аппаратуры и в тех случаях, когда штатная работа платы расширения нарушается трудно обнаруживаемыми сбоями. Встраивание в схемы PLD фрагментов таких отладочных средств, как следовые ОЗУ, логические анализаторы, разнообразные аппаратные ловушки позволяет разработчику облегчить задачу нахождения причины возникающих сбоев или перемежающихся.

2.6 Комплекс средств тестирования методом граничного сканирования JTools

|

|

|

Функциональные возможности комплекса базируются на интерфейсе JTAG и технологии граничного сканирования (Boundary Scan Testing), которые широко поддерживаются ведущими производителями БИС (Intel, Motorola, Altera, Xilinx, Atmel, TI, и другими).

Функциональные возможности комплекса базируются на интерфейсе JTAG и технологии граничного сканирования (Boundary Scan Testing), которые широко поддерживаются ведущими производителями БИС (Intel, Motorola, Altera, Xilinx, Atmel, TI, и другими).

Состав комплекса:

· универсальный загрузочный кабель;

· резидентная программа управления кабелем BitMaster;

· программа тестирования и отладки JTools.

· CD, содержащий базу BSD-файлов, документацию и учебно-методи-ческие материалы, связанные с JTAG интерфейсом и методом граничного сканирования.

|

|

|