|

Блок параллельного интерфейса / таймера

|

|

|

|

Задание

микропроцессор память блок шина

1. Разработать микропроцессорную систему на базе процессора MC68000.

2. Разработать и нарисовать структурную и принципиальную схему МПС. Произвести подключение шины адреса, данных и управления к соответствующим блокам на схеме. Сформировать блок устройства памяти (ОЗУ и ПЗУ) и подключить его к шинам блока центрального процессора на принципиальной схеме. ОЗУ должно обеспечивать выбор байта, слова и двойного слова.

3. Количество ОЗУ, ПЗУ, таймеров, параллельных и последовательных интерфейсов выбирается согласно варианту из таблицы.

Исходные данные

| ОЗУ, Кб | ПЗУ, Кб | Последовательные каналы (ввод/ вывод) | Параллельные каналы (ввод/ вывод) | Таймеры |

| 110 | 165 | 4 | 6 | 3 |

Разработка структурной схемы МПС

Для построения структурной схемы МПС необходимо рассчитать количество микросхем ОЗУ, ПЗУ, а также периферийных микросхем: DUART (Dual Asynchronous Receiver/Transmitter - двойной асинхронный приёмопередатчик) и PI/T - программируемый параллельный интерфейс-таймер.

Так как объем ОЗУ равен 110 Кб, а ПЗУ - 165 Кб, то необходимо использовать два слоя для ОЗУ и три слоя для ПЗУ. Каждый слой состоит из 4-х микросхем памяти ёмкостью 64Кх8 бит каждая, что позволяет производить обработку операндов различной размерности - байт, слово и длинное слово.

Для обеспечения заданного исходными данными 4 последовательных каналов передачи и 4 каналов приема необходимо 2 микросхемы DUART (по два канала передачи и приема в каждой).

Для обеспечения заданного исходными данными 6 параллельных каналов ввода и 6 параллельных каналов вывода необходимо 6 микросхем PI/T, т.к. для передачи или приема могут используются порты А и В, а порт С может использоваться для управления таймером и прерываниями.

|

|

|

Выбор необходимых слоев ОЗУ, ПЗУ, микросхем последовательного или параллельного интерфейсов, а также микросхем таймеров, производится с помощью дешифраторов.

Структурная схема МПС MC68000 состоит из элементов:

– CPU - микропроцессор MC68000;

– ГТИ - генератор тактовых импульсов;

– RAM - Оперативное запоминающее устройство (ОЗУ);

– ROM - Постоянное запоминающее устройство (ПЗУ);

– DUART - двойной асинхронный приемопередатчик;

– PI/T - программируемый параллельный интерфейс-таймер.

– FPGA - программируемая логическая схема.

Структурная схема любого МП комплекта сводится к отображению функционально законченных узлов в виде прямоугольников и отображению их соединений между собой только основными сигналами.

Разработка принципиальной схемы МПС

Блок микропроцессора

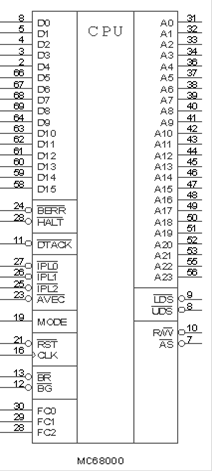

В качестве центрального процессора в данной курсовой работе используется процессор фирмы Motorola MC68000. Он имеет 16 - разрядную шину данных и 24-разрядную шину адреса. На рис. 2.1 приведена схема подключения микропроцессора к шинам проектируемой МПС.

Рис. 2.1 - Схема микропроцессора

Системные сигналы. CLK - тактовый сигнал синхронизации, период которого определяет продолжительность такта машинного цикла. CLK согласовывает во времени функционирование узлов и блоков МП и сопровождает обмен в МПС.

Внешний сигнал системного сброса  = 0 вызовет системное прерывание выполнения текущей программы, а содержимое регистров адреса и данных обнуляется. В регистре признаков SR устанавливается значения флажка S = 1 (режим супервизора), а другие флажки приобретают значение 0. Внешний сигнал

= 0 вызовет системное прерывание выполнения текущей программы, а содержимое регистров адреса и данных обнуляется. В регистре признаков SR устанавливается значения флажка S = 1 (режим супервизора), а другие флажки приобретают значение 0. Внешний сигнал  обычно формируется во время включения питания или при нажатия клавиши сброса. Сигнал

обычно формируется во время включения питания или при нажатия клавиши сброса. Сигнал  = 0 формируется также при выполнении привилегированной команды RESET, которая переводит к начальному состоянию другие устройства МПС. Входной сигнал

= 0 формируется также при выполнении привилегированной команды RESET, которая переводит к начальному состоянию другие устройства МПС. Входной сигнал  = 0 останавливает выполнение текущей программы, переводит выводы А23…А1, D15…D0 в высокоимпедансное состояние (третье состояние), а выходы управляющих сигналов - к неактивному состоянию. С аналогичной реакцией МП формирует исходный сигнал

= 0 останавливает выполнение текущей программы, переводит выводы А23…А1, D15…D0 в высокоимпедансное состояние (третье состояние), а выходы управляющих сигналов - к неактивному состоянию. С аналогичной реакцией МП формирует исходный сигнал  =0 при двойной ошибки шины (двукратное поступление сигнала

=0 при двойной ошибки шины (двукратное поступление сигнала  = 0), выход из состояния остановки происходит при поступлении внешнего сигнала

= 0), выход из состояния остановки происходит при поступлении внешнего сигнала  = 0 или прерывания. Сигнал ошибки обращения к шине

= 0 или прерывания. Сигнал ошибки обращения к шине  = 0 формируется контролером шины.

= 0 формируется контролером шины.

|

|

|

Сигналы управления обменом.  - адресный строб, который своим активным уровнем

- адресный строб, который своим активным уровнем  = 0 в тактах S0 и S1 в цикле обмена сопровождает адрес на ША.

= 0 в тактах S0 и S1 в цикле обмена сопровождает адрес на ША.  - сигнал, который определяет направление обмена по ШД: ввод в МП (чтение) - при

- сигнал, который определяет направление обмена по ШД: ввод в МП (чтение) - при  = 1; вывод из МП (запись), если

= 1; вывод из МП (запись), если  = 0.

= 0.  (передача старшего байта),

(передача старшего байта),  (передача младшего байта) - сигналы, которые определяют размер данных на ШД.

(передача младшего байта) - сигналы, которые определяют размер данных на ШД.  = 0,

= 0,  = 0 определяют передачу слова. Младший байт передается, если

= 0 определяют передачу слова. Младший байт передается, если  = 1 и

= 1 и  = 0, старший -

= 0, старший -  = 0,

= 0,  = 1. Входной сигнал готовности к обмену

= 1. Входной сигнал готовности к обмену  = 0 поступает, если периферийное устройство или память - объекты обращения - готовы к обмену. Иначе -

= 0 поступает, если периферийное устройство или память - объекты обращения - готовы к обмену. Иначе -  = 1.

= 1.

Сигналы управления захватом шины. Эти сигналы определяют порядок использования системной шины устройствами системы. В режиме захвата шины МП отсоединяется от шины, а управление обменом осуществляет другое устройство. Чаще всего - это режим прямого доступа к памяти (ПДП), когда осуществляется обмен между основной памятью (ОП) и каким-нибудь внешним устройством без участия МП.  - входной сигнал запроса от внешнего устройства на захватывание шины. Если

- входной сигнал запроса от внешнего устройства на захватывание шины. Если  = 0, МП завершает текущий цикл обмена, приостанавливает выполнения команды и переводит выводы А23…А1, D15…D0 в высокоимпедансное состояние, а выходы управляющих сигналов - к неактивному состоянию.

= 0, МП завершает текущий цикл обмена, приостанавливает выполнения команды и переводит выводы А23…А1, D15…D0 в высокоимпедансное состояние, а выходы управляющих сигналов - к неактивному состоянию.  - исходный сигнал разрешения захватывания шины, который приобретает значение

- исходный сигнал разрешения захватывания шины, который приобретает значение  = 0 после разъединения МП с шиной.

= 0 после разъединения МП с шиной.  - входной сигнал подтверждения захватывания шины. После получения

- входной сигнал подтверждения захватывания шины. После получения  = 0 устройство, которое требовало разрешения на захватывание шины, присылает к МП сигналы

= 0 устройство, которое требовало разрешения на захватывание шины, присылает к МП сигналы  = 0, отменяет запрос на захватывание (

= 0, отменяет запрос на захватывание ( = 1) и переходит к управлению шиной. После завершения обмена указанное устройство присылает сигнал

= 1) и переходит к управлению шиной. После завершения обмена указанное устройство присылает сигнал  = 1. Затем МП переходит к выполнению прерванной команды.

= 1. Затем МП переходит к выполнению прерванной команды.

|

|

|

Сигналы FC2…FC0. Трехразрядный код FC2…FC0 определяет тип выполняемого цикла. Соответствующие комбинации битов указанного кода используются для распределения банков данных между супервизором и пользователем, формирования сигнала подтверждения прерывания  .

.

Поскольку выводы шины данных процессора обладают низкой нагрузочной способностью, то при большом количестве периферийных внешних устройств возможны сбои в работе процессора и возможен перегрев с последующим выходом из строя. Для исключения этой ситуации шину необходимо буферизировать (усиливать). В качестве буферных устройств можно использовать микросхемы 74F245. На рисунке 2.2 приведена схема буферизации шины данных.

Рисунок 2.2 - Схема буферизации шины данных

Блок памяти

В качестве микросхемы для ОЗУ в курсовой работе используется микросхема статического ОЗУ AMC21С512. Она представляет собой маломощное запоминающее устройство емкостью 64Кх8, выполненное по CMOS технологии и полностью совместима с уровнями ТТЛ. Принципиальное обозначение показано на рис. 2.3. Она имеет вход выборки микросхемы СЕ и вход разрешения выдачи данных ОЕ. Также имеется вход запись / чтение R/W. Работу микросхемы поясняет таблица 2.1.

Рисунок 2.3 - Банк ОЗУ на микросхеме AMC21С512

Таблица 2.1 - Таблица работы микросхемы ОЗУ AMC21С512

| Режим | R/W | СЕ | ОE | Операция ввода / вывода |

| Не выбрана | X | 1 | X | Высокоимпедансное состояние |

| Запрет выхода | X | 0 | 1 | Высокоимпедансное состояние |

| Чтение | 1 | 0 | 0 | Считывание |

| Запись | 0 | 0 | X | Запись |

X - любой сигнал (0 или 1)

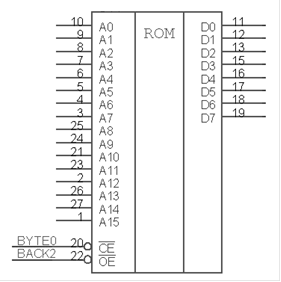

В качестве микросхемы для ПЗУ в курсовой работе используется микросхема AMC27C512. Она представляет собой маломощное запоминающее устройство емкостью 64Кх8 и полностью совместима с уровнями ТТЛ. Условное графическое обозначение показано на рис. 2.4. Она имеет вход выборки микросхемы CS и один вход разрешения выдачи данных ОЕ. Работу микросхемы поясняет таблица 2.2.

Рисунок 2.4 - Блок ПЗУ AMC27C512

Таблица 2.2 - Таблица работы микросхемы ПЗУ AMC27C512

|

|

|

| Режим | СЕ | ОЕ | D0-D7 |

| Не выбрана | 1 | X | Высокоимпедансное состояние |

| Запрет выхода | 0 | 1 | Высокоимпедансное состояние |

| Чтение | 0 | 0 | Считывание |

Поскольку шина данных микропроцессора 16-ти разрядная, то запись длинного слова производится за два цикла шины. Выбор нужного числа разрядов осуществляется соответствующей обработкой сигналов UDS# и LDS#. Управляющий сигнал R/W подаётся на блок ОЗУ, и определяет производится запись или чтение.

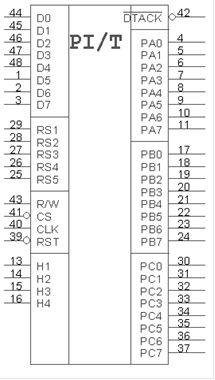

Блок параллельного интерфейса / таймера

Согласно исходным данным к разработанной микропроцессорной системе необходимо подключить периферийные устройства - последовательные порты ввода-вывода (DUART) и параллельные порты ввода-вывода (PI). Для этого используются имеющиеся в микропроцессорном комплекте микросхемы сдвоенного универсального асинхронного последовательного приёмопередатчика МС68681 и параллельный интерфейс / таймер МС68230. Микросхема МС 68230 включает в себя:

– 3 многофункциональных восьмиразрядных порта;

– многофункциональный 24-разрядный таймер с возможностью использования пяти разрядного предделителя;

– устройство управления режимами работы;

– логику прямого доступа к памяти;

– логику управления прерываниями.

Функциональное обозначение МС68230 представлено на рис. 2.5, назначение выводов в табл. 2.3.

Таблица 2.3 - Назначение выводов микросхемы МС 68230

| Наименование вывода | Функциональное назначение вывода | Примечание |

| D7 - D0 | Шина данных. | - |

| DTACK | Подтверждение передачи данных. | - |

| R/W | Чтение / Запись. | - |

| CS | Выбор микросхемы. | - |

| RESET | Сброс. | - |

| RS5-RS1 | Выбор внутреннего регистра, порта или команды | - |

| CLK | Тактовая частота микросхемы | - |

| H4-H1 | Линии квитирования | Могут быть использованы как линии ввода / вывода (H1 и Н3 - только ввод) или импульсные входы запросов на обслуживание внешних прерываний |

| PA7 - РА0 | Порт А | - |

| РВ7 - РВ0 | Порт В | - |

| РС7 - РС0 | Порт С | Линии РС7 + РС2 имеют альтернативные функции. |

Рисунок 2.5 - Функционально-принципиальная схема PI/T

Структура микросхемы PI/T типа МС68230 включает блоки, обеспечивающие связь с микропроцессором и блоки, обслуживающие внешние устройства. Выводы РС7-2 порта С могут программироваться для передачи сигналов таймера, прерывания, запроса прямого доступа.

Связь PI/T с микропроцессором MC68000 реализуется путём обмена данными по линиям D7-0 в цикле чтения или записи. При этом от микропроцессора поступает соответствующий сигнал R/W#, a PI/T выдаёт сигнал подтверждения готовности DTACK#. Данные считываются или записываются в один из регистров таймера, порта А, В, С или блока управления обменом. Выбор регистра определяется адресным кодом, поступающим на входы RS5-1. Все регистры, кроме CNT, СРТ, имеют 8 разрядов, поэтому адресуются как байт. Регистры таймера CNT, СРТ, имеющие 24 разряда, адресуются как три отдельные 8-ми разрядные регистры. В адресном пространстве PI/T занимает 32 байтовых ячейки, из которых 23 ячейки заняты регистрами, остальные остаются неиспользуемыми. При обращении к PI/T на входы RS5-1 поступают соответствующие разряды формируемого микропроцессором адреса. На вход CLK поступают тактовые сигналы от генератора тактовых импульсов. На вход RESET# подаётся общий для всей системы сигнал сброса.

|

|

|

Программирование портов А, В, С и таймера на выполнение различных режимов обслуживания внешних устройств производится путём записи управляющих кодов в регистры управления соответствующих блоков PI/T.

Порты А и В обеспечивают параллельный обмен данными между микропроцессором и внешними устройствами.

Таймер реализован на базе 24-х разрядного вычитающего счётчика (CNT), начальное состояние которого устанавливается при инициализации, путём записи содержимого в регистр предварительной установки CPR. Запуск таймера происходит при записи в регистр управления TCR соответствующего управляющего кода, который определяет также режим его функционирования. При этом уменьшение содержимого CNT может производиться при поступлении тактовых импульсов CLK или внешних сигналов на вход TIN#. В режиме генерации (счёт импульсов CLK) таймер через интервалы времени, определяемые содержимым CPR, формирует сигналы на выходе TOUT#. В режиме счёта событий текущее содержимое CNT указывает число поступивших сигналов. Можно запрограммировать деление частоты считаемых импульсов на 32. При работе таймера на выходе TOUT# формируются прямоугольные импульсы, которые могут служить для управления внешними устройствами (периодическое включение-выключение, синхронизация и т.п.). Сигнал TOUT# может подаваться также на вход приоритетного шифратора в качестве запроса прерывания для микропроцессора. При этом сигнал подтверждения прерывания должен поступать на вход ТIАСК#. Для считывания вектора прерывания микропроцессор должен обратиться к регистру TIVR, в который значение этого вектора вводится в процессе инициализации таймера. Таким образом, использование таймера позволяет запускать требуемую программу в заданные моменты.

|

|

|