|

Структурная нотация и архитектура ВС Raspberry Pi

|

|

|

|

System (BCM2835) = [  ,

,  (

( ), E (TrustZone), U (IEM), U1 (reset controller)][1];

), E (TrustZone), U (IEM), U1 (reset controller)][1];

=

=  [

[  –

–  –

–  ] – M

] – M

M  = {

= {  ,

,  –

–  ,

,  } – L1MS{

} – L1MS{  } –

} –  –

–  };

};

E (TrustZone) = {U (Protection Controller H (APB3)),  ,

,  , U2(CAI)};

, U2(CAI)};

U (IEM) = {H (APB3) <–> U1(IEC), U2(DVC), U3(HPM), U4(reset controller)}.

• I – устройство обработки потока команд

• B – целочисленные устройства исполнения

• Rg – регистры

• Core - ядро процессора;

• CshI – кэш инструкций;

• CshD – кэш данных;

• Csh1, 2, 3 – кэш данных 1, 2, 3 уровня;

• IO – интерфейс устройства ввода-вывода;

• E - исполнительное устройство;

• U – неспециализированное устройство (здесь большинство означает “контроллер”);

• F - устройство исполнения операций с плавающей точкой;

• TrustZone – набор инструкций процессора, позволяющих реализовывать защитный функционал, потоковую передачу и пр.;

• TrustZone System Protection Controller APB3 peripheral;

• L1MS – Level 1 Memory System;

• IEM - Intelligent Energy Management;

• IEC – Intelligent Energy Controller;

• DVC – Dynamic Voltage Controller;

• HPM – Hardware Performance Monitor.

При описании нотаций использовались блок схемы процессоров и модулей ВС (приведены далее по тексту), а также документация-руководство данных элементов[1]. Каждый указанный элемент имеет свою структуру, требующую описания, но не описывается в используемых руководствах.

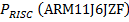

Рисунок 1. Схема блочного устройства процессора ARM1176JZF-S

В архитектуру микропроцессора класса Raspberry входят следующие элементы:

· ARM11J6JZF-S (ARM11 Family)

· ARMv6 Architecture

· Single Core

· 32-Bit RISC

· 700 MHz Clock Rate

· BCM2835 256MB RAM

· 8 Pipeline Stages

· Branch Prediction

Основу микропроцессора составляет процессор ARM1176,процессор приложений, развернут в устройствах, начиная от смартфонов до цифрового телевидения, предоставляя средства чтения, представленияданных, защиты вычислительной среды, а также производительность до 1 ГГц в условиях низкой стоимости конструкций. Процессор ARM1176JZ-S поддерживает технологию ARMTrustZone® для защиты приложений и технологий ARMJazelle® для эффективного встроенного исполнения Java. Необязательные тесно связанные воспоминания упрощают миграцию процессора ARM9 ™ и дизайн в режиме реального времени, в то время как AMBA® 3 AXITM интерфейсы повышения производительности шины памяти. Поддержка DVFS позволяет номинально оптимизировать статическую и динамическую мощности архитектуры ARM11TM процессора [3].

|

|

|

Рисунок 2. Внутреннее строение процессораARM 1176

Raspberry основан на архитектуре RISC. RISC (компьютер с сокращённым набором команд) — архитектура процессора, в котором быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Первые RISC-процессоры даже не имели инструкций умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками). Основной идеей всех RISC (Reduced Instruction Set Computer), является увеличение быстродействия за счет сокращения количества операций обмена с памятью программ. Для этого каждую команду стремятся уместить в одну ячейку памяти. При ограниченной разрядности ячейки памяти это неизбежно приводит к сокращению набора команд микропроцессора.

Рисунок 3. Схема функционального устройства процессора ARM1176JZF-S

Все выполняемые команды микропроцессора связаны с соответствующими регистрами, позволяющими выполнять те или иные функции.

Таймер/счетчик событий – внутренний таймер, предназначенный длязапуска программы обработки прерывания при определенных условиях счета, в том числе и внешних событий.

Сторожевой таймер предназначен для защиты микроконтроллера отсбоев в процессе работы. При срабатывании сторожевого таймера происходит внутренний перезапуск работы микроконтроллера.

|

|

|

Порты ввода/вывода AVR имеют от 5 до 32 независимых линий ввода/вывода, причем каждый разряд любого порта может быть запрограммирован на ввод или на вывод.

Аналого-цифровой преобразователь – это 10-разрядный АЦП с устройством выборки/хранения и входным аналоговым мультиплексором.

Аналоговый компаратор предназначен для сравнения непрерывно изменяющихся сигналов. Входные аналоговые сигналы компаратора Uвх – анализируемый сигнал и Uоп – опорный сигнал сравнения, а выходной Uвых – дискретный или логический сигнал, содержащий 1 бит информацииn таймер/счетчик – дополнительные таймера/счетчики. Кроме того, можетсодержать широтно-импульсный модулятор (ШИМ), предназначенный дляформирования сигналов заданной длительности при определенных условиях.

Скоростной последовательный интерфейс SPI – последовательныйсинхронный интерфейс ввода/вывода, используется для передачи данных попротоколу SPI.

Асинхронный, дуплексный последовательный порт UART – последовательный порт ввода/вывода информации.[2]

Высокая производительность до 1Гг (в последних версиях ещё выше до 1.4Гг) обеспечивается тактовым генератором процессора BCM2835. В дополнение к MMU от ARM (memory management unit – блок управления памятью), BCM2835 также обладает вторым уровнем MMU для отображения ARM физических адресов на системной шины адреса. На рисунке 4 показаны основные адресные пространства, представляющие контроль. Это позволяет реализовать много эффективную систему управления памятью, при этом не расширяя схему микропроцессора в целом.

Addresses in ARM Linux are: • issued as virtual addresses by the ARM core, then • mapped into a physical address by the ARM MMU, then • mapped into a bus address by the ARM mapping MMU, and finally • used to select the appropriate peripheral or location in RAM.

Реализованные адреса, на основе ARMLinux,следуют следующему пути[5]:

· определение в качестве виртуальных адресов ядром ARM, затем

· отображение в физический адрес на ARM MMU, затем

· отображение в адрес шины отображением ARM MMU, и, наконец,

· распределение по модулям соответствующего периферийного устройства или определённому местоположению в оперативной памяти.

В обычной практике, стандарт BCM2835 Linux ядра обеспечивает непрерывное отображение по всей доступной оперативной памяти в верхней части памяти. Ядро конфигурируется для 1GB / 3GB разделена между ядром и пользовательского пространства памяти.

|

|

|

Виртуальные адреса в режиме ядра будет колебаться между 0xC0000000 и 0xEFFFFFFF.

Виртуальные адреса в пользовательском режиме (т.е. видели процессами, работающими в ARM Linux) будет варьироваться между 0x00000000 и 0xbfffffff.

Периферия (по физическому адресу 0x20000000) отображается в пространство виртуального адресаядра, начиная с адреса 0xF2000000. Таким образом, периферия представлена здесь на адресе шины0x7Ennnnnn и доступен в ARM канал по виртуальному адресу 0xF2nnnnnn.

Рисунок 4. Периферия BCM2835

Программное обеспечение периферии прямого доступа переводит эти адреса в физические или виртуальные. Программное обеспечение, представляющее доступ периферии, использующей технологию DMA,используетшины адреса. Программное обеспечение непосредственного доступа к ОЗУ используют физические адреса (начиная с 0x00000000). Программное обеспечение доступа к оперативной памяти с использованием технологии DMA используют шины адреса (начиная с 0xC0000000).

Большинство аппаратных конвейеров и периферия BCM2835 bus мастера, позволяют им эффективно удовлетворять свои собственные потребности в данных. Это уменьшает требования контроллера DMA к типу перевода памяти блок-к-блоку и поддерживает некоторыеиз более простых периферийных устройств. Кроме того, контроллер DMA обеспечивает предвыборку режима “только для чтения”, чтобы данные, которые будут введены в L2 кэш в ожидании его дальнейшего использования.

Контроллер DMA BCM2835 обеспечивает в общей сложности 16 каналов DMA. Каждый канал работает независимо от других и внутренне присуждает одной из 3-х системных шин. Это даёт возможность управлять шириной пропускной способности канала DMA при помощи настройки арбитра.

Более подробно, структура процессора включает также такие элементы как: вычислительное ядро (Core), модуль загрузки (LoadStoreUnit), предварительный модуль (PrefetchUnit), блок управления памятью(MMU), блок памяти 1 и 2 уровней, блок прерывания (InterruptHanding), AMBA интерфейс, блок кэш памяти, блок TCM, блок отладки (Debug), сопроцессор векторной плавающей точкой(VectorFloatingPoint), интерфейс сопроцессора (рис. 5).

|

|

|

Рисунок 5. Структурная модель процессора[5]

|

|

|