|

Каскадирование дешифраторов

|

|

|

|

Тема 10. Дешифраторы.

Устройство и принцип действия

Еще один элемент, без которого не обойтись при изучении микропроцессорной техники, — это дешифратор цифровых сигналов. Существует много разных типов дешифраторов. В общем случае дешифратор — это устройство, преобразующее цифровой сигнал, представленный в какой-либо одной из кодировок, в другую, незакодированную форму. Нас в данном случае будет интересовать классический линейный дешифратор. Схемное обозначение одного из вариантов такого дешифратора приведено на рис. 1.25. Описываемый дешифратор имеет три входа данных D0, D1 и D2, вход выбора микросхемы CS, а также восемь выходов, обозначенных цифрами от 0 до 7.

Логика работы микросхемы такова: на входы данных микросхемы подается цифровой код. В данном случае — это любое трехразрядное двоичное число. Смысл работы такого дешифратора — выдать

Логика работы микросхемы такова: на входы данных микросхемы подается цифровой код. В данном случае — это любое трехразрядное двоичное число. Смысл работы такого дешифратора — выдать

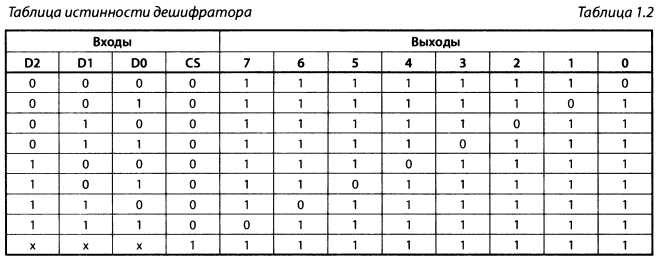

активный сигнал только на одном из своих выходов. На том выходе, номер которого соответствует двоичному коду, присутствующему на его входах D0—D2. В большинстве современных дешифраторов активным сигналом на выходе считается логический уровень. Это значит, что при поступле нии на входы D0—D1 сигнала 0002, на выходе «0» будет логический ноль, а на всех остальных выходах — единица. Состояние выходов дешифратора при других значениях входного сигнала приведено в табл. 1.2.

Табл. 1.2 — это таблица истинности данного дешифратора. Важное значение имеет вход выбора микросхемы  . Этот вход позволяет включить или выключить всю микросхему. Микросхема работает только в том случае, если на вход

. Этот вход позволяет включить или выключить всю микросхему. Микросхема работает только в том случае, если на вход  дешифратора подан разрешающий нулевой сигнал. В противном случае микросхема выключается и на всех ее выходах устанавливается сигнал логической единицы.

дешифратора подан разрешающий нулевой сигнал. В противном случае микросхема выключается и на всех ее выходах устанавливается сигнал логической единицы.

|

|

|

Главное назначение линейного дешифратора — функция выбора одного из нескольких электронных устройств. Например, выбор одной из нескольких микросхем памяти. Каждая такая микросхема должна иметь свой собственный вход  . К каждому выходу дешифратора подключается одна такая микросхема. Вернее, подключается ее вход

. К каждому выходу дешифратора подключается одна такая микросхема. Вернее, подключается ее вход  .

.

Теперь, если на входы D0—D2 дешифратора подать номер выбираемой микросхемы, она включится, а остальные семь микросхем отключатся. При выключении самого дешифратора отключаются и все подключенные к нему микросхемы.

Селектор памяти ячеек ОЗУ

Хороший пример использования дешифратора — селектор ячеек памяти ОЗУ. Схема простейшего модуля ОЗУ, состоящего всего из четырех ячеек, приведена на рис. 1.26. В качестве ячеек памяти в схеме используются параллельные регистры с возможностью перевода в высокоимпедансное состояние.

Рассмотрим внимательно схему на рис. 1.26.

Линии LD0-LD7 — это восьмиразрядная шина данных. Она используется как для записи чисел в память, так и для чтения из нее.

Входы LA0, LA1 — это так называемые входы адреса.

Вход UPR — вход выбора для всего устройства.

Входы WRITE и READ, соответственно, — вход команды записи и вход команды чтения.

Входы UPR, WRITE и READ — инверсные. То есть в отсутствии сигнала на каждом из них должен присутствовать высокий логический уровень. Активным сигналом для этих входов является логический ноль.

Для того, чтобы записать число в одну из ячеек такого ОЗУ, нужно сначала на вход UPR подать нулевой сигнал (выбрать устройство). Затем на лини LD0—LD7 от внешнего источника цифрового сигнала подать восьмиразрядное двоичное число, предназначенное для записи. Затем на линии LAO, LA1 подается число, соответствующее номеру нужной ячейки памяти (адрес ячейки). Номер выбранной ячейки поступает на дешифратор DDL

Предположим, что мы хотим выбрать нулевую ячейку памяти. Для этого мы подадим на входы LAO, LA1 сигнал 002. В результате на выходе Q0 дешифратора появляется нулевой сигнал, а на всех остальных его выходах — единичный. С выхода Q0 дешифратора нулевой сигнал поступает на вход  параллельного регистра DD2 и включает его. Все остальные регистры остаются отключенными. Теперь для того, чтобы записать число в выбранную ячейку памяти, нужно подать короткий нулевой импульс на вход WRITE. Он поступит на входы С всех регистров. Но число запишется только в регистр DD2.

параллельного регистра DD2 и включает его. Все остальные регистры остаются отключенными. Теперь для того, чтобы записать число в выбранную ячейку памяти, нужно подать короткий нулевой импульс на вход WRITE. Он поступит на входы С всех регистров. Но число запишется только в регистр DD2.

|

|

|

Как видно из схемы на рис. 1.26, лини D0—D7 объединяют в себе не только входы регистров, но и их выходы. Однако такая схема включения не мешает работе устройства. Это достигается благодаря тому, что все регистры имеют выходы с тремя состояниями. К двум обычным состояниям (ноль и единица) добавлено третье — высокоимпендансное. Это состояние включается при подаче на вход ОЕ любого регистра логической единицы.

В режиме чтения информации лини LD0—LD7 используются как выходы. Для того, чтобы прочитать число из любой ячейки памяти, нужно сначала подать адрес ячейки на входы LA0, LA1. Это приводит к тому, что нужный нам регистр включается. Включается точно так же, как это происходило при записи.

Теперь для того, чтобы прочитать число из выбранной ячейки, достаточно подать на вход READ сигнал логического нуля. В результате выходы выбранного регистра перейдут из высокоимендансного в рабочее состояние. На них появится записанное в регистр число, которое поступит на выход всей схемы. Все остальные регистры останутся отключенными и не будут мешать процессу чтения.

Каскадирование дешифраторов

Прежде,чем покончить с дешифраторамихочурассмотреть вопрос их каскадирования. Благодаря наличию входа  , несколько дешифраторов можно объединять вместе, образуя составной дешифратор, имеющий большее число входов и выходов. Пока мы имели дело с двумя видами дешифраторов. Первый дешифратор (рис. 1.25) имел три входа и восемь выходов. Дешифратор, который мы использовали в примере схемы ОЗУ (рис. 1.26), имел всего два входа и четыре выхода. Логика работы любого такого дешифратора одна и та же. Различие состоит лишь в количестве входных и выходных разрядов.

, несколько дешифраторов можно объединять вместе, образуя составной дешифратор, имеющий большее число входов и выходов. Пока мы имели дело с двумя видами дешифраторов. Первый дешифратор (рис. 1.25) имел три входа и восемь выходов. Дешифратор, который мы использовали в примере схемы ОЗУ (рис. 1.26), имел всего два входа и четыре выхода. Логика работы любого такого дешифратора одна и та же. Различие состоит лишь в количестве входных и выходных разрядов.

|

|

|

Для того, чтобы в краткой форме обозначить характеристики конкретного дешифратора, иногда применяют следующее обозначение: «Дешифратор 2X4» или «Дешифратор 3X8». На рис. 1.27 показан способ, как при помощи каскадного соединения нескольких дешифраторов создать новый дешифратор с формулой «5X32». Первый каскад состоит из одного дешифратора (DD1). Этот дешифратор управляет четырьмя другими дешифраторами (DD2—DD5), которые составляют второй каскад.

Все дешифраторы, рассмотренные нами до сих пор, относятся к разряду полных дешифраторов. Поясню, что это такое. Если дешифратор имеет пять входов, то максимальное число значений, которые могут принимать эти входы, равно 32. Если при этом дешифратор имеет 32 выхода, то при подаче на его входы любого возможного числа, на одном из выходов обязательно появится активный уровень сигнала. В некоторых случаях наличие всех возможных выходов не обязательно.

Все дешифраторы, рассмотренные нами до сих пор, относятся к разряду полных дешифраторов. Поясню, что это такое. Если дешифратор имеет пять входов, то максимальное число значений, которые могут принимать эти входы, равно 32. Если при этом дешифратор имеет 32 выхода, то при подаче на его входы любого возможного числа, на одном из выходов обязательно появится активный уровень сигнала. В некоторых случаях наличие всех возможных выходов не обязательно.

Пример.

Дешифратор для работы с так называемыми двоично-десятичными числами. Двоично-десятичное число — это число, записанное в двоичной форме, но принимающее значение от 0 (00002) до 10 (10102). При работе с такими числами используют неполный дешифратор 4X10. Такой дешифратор имеет четыре входа и всего десять выходов. При подаче на входы такого дешифратора двоичных чисел в диапазоне от 00002 до 10102 активизируются выходы «0» — «9». При этом подразумевается, что числа выше чем 10102, на входы дешифратора подаваться не будут. Однако ничего не мешает подать на входы дешифратора эти числа. Как будет вести себя неполный дешифратор в таком случае, определяется его разработчиком. Чаще всего в этом случае все выходы дешифратора остаются неактивными. Промышленность выпускает несколько видов неполных дешифраторов. Например, К555ИД1, К555ИД6, К555ИД10.

|

|

|