|

Асинхронные и синхронные триггеры

|

|

|

|

Кафедра «Мехатронные системы»

Ю.Р. Никитин

Методические указания к лабораторной работе № 6

"Триггеры и регистры. S-R триггер, D-триггер, T-триггер, J-K триггер. Параллельная и последовательная запись данных в регистры. Параллельное и последовательное чтение данных из регистров "

по дисциплине

«ЭУМиРТС»

Ижевск 2016

Теоретические сведения

Триггеры представляют собой простейшие последовательные устройства (автоматы). Они широко используются в узлах электронной аппаратуры в виде самостоятельных элементов или в качестве базовых элементов для построения других, более сложных приборов (счетчиков, регистров, запоминающих устройств).

К триггерам относят большой класс устройств, общим свойством которых является способность длительно оставаться в одном из двух (или нескольких) возможных устойчивых состояний и скачком чередовать их под воздействием внешних сигналов. Значения выходных сигналов зависят не только от значений входных сигналов, но и от последовательности их изменений. Каждое состояние легко распознается по значению выходных напряжений и триггеров – запоминание информации. Под памятью триггера подразумевается способность оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Приняв одно из состояний за 1, а другое – за 0, можно считать, что триггер хранит (помнит) один разряд числа в двоичном коде.

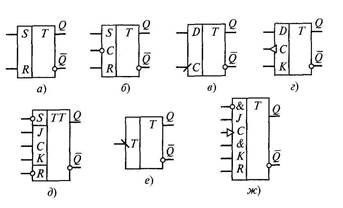

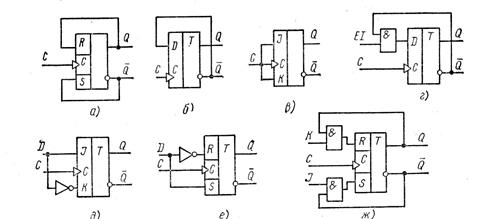

Рисунок 1 – Условные обозначения триггеров: асинхронный RS-триггер (а);

синхронный RS-триггер (б); D-триггер (в); JK-триггер (г);

двухступенчатый JK-триггер (д); Т-триггер, срабатывающий по срезу (е);

JK-триггер с логическими элементами & на входах J и K (ж)

|

|

|

Понятие «триггер» охватывает много видов устройств, которые существенно различаются между собой по выполняемым функциям, схемному исполнению, способам управления, электрическим и конструктивным параметрам.

Для рассмотрения последовательных схем требуется введение в явном виде времени для описания изменений потенциальных сигналов. Аналитически это можно сделать с помощью операторов переходов d и  .

.

Потенциальные (асинхронные) и импульсные сигналы. Сигналы называются потенциальными, если интервалы времени Тi между соседними изменениями сигналов значительно больше времени реакции схемы τP, в которой они используются, т.е. сигнал x(t) будет потенциальным, если min (T1, T2, T3) >> τP. Сигнал называется импульсным, если его длительность того же порядка, что и время реакции схемы (схема должна отреагировать на воздействие импульсного сигнала, а импульсный сигнал должен закончиться сразу же после окончания переходного процесса). При аналитическом описании схем, на которые воздействуют импульсные сигналы, используется понятие абстрактного импульсного сигнала, длительность которого бесконечно мала. Такие сигналы (dx,  , ∆x) порождаются изменениями сигнала x с 1 на 0 и с 0 на 1. Реальные импульсные сигналы всегда имеют конечную длительность, которая определяется временем реакции схемы и может изменяться в широких пределах в зависимости от быстродействия ЛЭ, на которых она построена. Понятие абстрактного импульсного сигнала позволяет абстрагироваться от физических параметров схемы.

, ∆x) порождаются изменениями сигнала x с 1 на 0 и с 0 на 1. Реальные импульсные сигналы всегда имеют конечную длительность, которая определяется временем реакции схемы и может изменяться в широких пределах в зависимости от быстродействия ЛЭ, на которых она построена. Понятие абстрактного импульсного сигнала позволяет абстрагироваться от физических параметров схемы.

Оператор перехода d определяется соотношением

dx =  ·x(t –∆t),

·x(t –∆t),

где dx – импульсный сигнал, порождаемый изменениями потенциального сигнала с 1 на 0; x(t) – значение потенциального сигнала в данный момент времени; x(t – ∆t) – значение потенциального сигнала в предыдущий момент времени. Очевидно, dx = 1 только при изменении потенциального сигнала x с 1 на 0.

|

|

|

Ценность соотношения заключается в том, что оно учитывает в явном виде время и может использоваться не только для потенциальных сигналов, но и для переключательных функций от потенциальных сигналов.

Асинхронные потенциальные триггеры (триггерные ячейки)

В простейшем исполнении триггер представляет собой симметричную структуру из двух логических элементов: ИЛИ – НЕ либо И – НЕ, охваченных перекрестной положительной связью. Такие триггеры называются симметричными. Схема симметричного триггера на основе логических элементов «И – НЕ» дана на рис. 2, а. Этот триггер (бистабильная ячейка, ячейка памяти, асинхронный RS-триггер) обладает двумя устойчивыми состояниями, которые обеспечиваются за счет связи выхода каждого элемента с одним из входов другого. Свободные входы служат для управления и называются информационными или логическими.

Симметрия схемы не означает симметрии электрических режимов обоих каскадов. За счет перекрестного соединения входов создаются условия, при которых при отсутствии входных сигналов один из логических элементов будет заперт, а другой – открыт.

Одному из выходов триггера присваивают наименование прямого (в силу симметрии схемы им может быть любой) и обозначают символом Q, а другому – наименование инверсного и обозначают  , что в логическом смысле означает, что сигнал на этом выходе противоположен первому. Состояние триггера отождествляют с сигналом на прямом выходе, т.е. триггер находится в единичном состоянии, когда Q = 1, а

, что в логическом смысле означает, что сигнал на этом выходе противоположен первому. Состояние триггера отождествляют с сигналом на прямом выходе, т.е. триггер находится в единичном состоянии, когда Q = 1, а  = 0, и в нулевом, когда

= 0, и в нулевом, когда  Q = 0, а

Q = 0, а  = 1.

= 1.

Смена состояний триггера производится внешними сигналами. Название этого процесса имеет много синонимов: переключение, опрокидывание, переброс, запись информации. Начало опрокидывания происходит с приходом отрицательного перепада напряжения – (0) на вход закрытого элемента. Вход, по которому триггер устанавливается в единичное состояние (Q = 1,  = 0), называют входом S (от англ. set – установка), а в нулевое (Q = 0,

= 0), называют входом S (от англ. set – установка), а в нулевое (Q = 0,  = 1) – вход R (reset – возврат).

= 1) – вход R (reset – возврат).

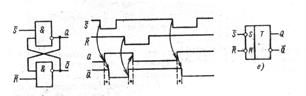

а) б) в)

Рисунок 2 – Схема RS-триггера на ЛЭ «И – НЕ» (а);

диаграмма переключений (б); условное обозначение (в)

Карта Карно (рис. 3), отображающая функции состояний входов и выхода RS – триггера «И – НЕ». Ф – фиктивное, запрещенное состояние, характеризующее свойство триггера, имеющего только два устойчивых состояния, способных хранить 1 бит информации (данных).

|

|

|

Рисунок 3 – Карта Карно

Таблица 1 – Функциональное назначение входов триггеров

| Условное обозначение | Наименование |

| Информационные входы | |

| S | Вход раздельной установки триггера в состояние 1 |

| R | Вход раздельной установки триггера в состояние 0 |

| J | Вход установки JK-триггера в состояние 1 |

| K | Вход установки JK-триггера в состояние 0 |

| T | Вход счетного триггера (счетный вход) |

| D | Вход установки D-триггера в состояние 1 |

| Управляющие входы | |

| V | Подготовительный вход разрешения приема информации |

| C | Исполнительный вход приема информации, вход синхронизации (тактовый вход) |

Асинхронные и синхронные триггеры

Независимо от способа организации логических связей триггеры различаются по способу ввода информации и по этому признаку могут быть асинхронными и синхронными.

У асинхронных триггеров имеются только информационные (логические) входы. Асинхронные триггеры отличает свойство срабатывать непосредственно за изменением сигналов на входах, не считая времени задержки в элементах, образующих триггер.

Синхронные триггеры кроме информационных входов имеют также вход подачи тактового сигнала «С». Синхронный триггер состоит из КС (комбинационных схем) и ЭП (элементов памяти), в качестве которых используются синхронные элементы задержки D информационных сигналов Q+ на один период тактового сигнала «С». Из этого следует, что различие синхронных и асинхронных потенциальных триггеров заключается лишь в использовании в различных по функциям ЭП. В синхронных ЭП тактовый сигнал оказывает на них импульсное воздействие в моменты изменения с 0 на 1 (или с 1 на 0), а изменения информационных сигналов Q  не воздействуют на ЭП. Выходной сигнал Qr синхронного элемента задержки принимает значение входного сигнала Q

не воздействуют на ЭП. Выходной сигнал Qr синхронного элемента задержки принимает значение входного сигнала Q  в момент импульсного воздействия тактового сигнала С. Тактовый сигнал С задает дискретное время tД = 1, 2, 3… На этом основании функционирование триггера может рассматриваться только в эти дискретные моменты при соблюдении следующих условий: входные сигналы xn не должны изменяться в моменты времени, когда dC = 1; переходный процесс, возникший в предыдущем дискретном моменте времени tД, должен заканчиваться к следующему дискретному моменту времени tД + 1.

в момент импульсного воздействия тактового сигнала С. Тактовый сигнал С задает дискретное время tД = 1, 2, 3… На этом основании функционирование триггера может рассматриваться только в эти дискретные моменты при соблюдении следующих условий: входные сигналы xn не должны изменяться в моменты времени, когда dC = 1; переходный процесс, возникший в предыдущем дискретном моменте времени tД, должен заканчиваться к следующему дискретному моменту времени tД + 1.

|

|

|

Таким образом, воздействие тактового сигнала позволяет полностью исключить из рассмотрения переходные процессы в синхронном триггере, что нельзя сделать в асинхронном потенциальном триггере, в котором изменение выходных сигналов ЭП Qr вызывается изменением входных сигналов Q+r.

Тактовый сигнал С выполняет функцию временного селектирования информационных сигналов ЭП Q+r в моменты времени tД, поэтому требуется, чтобы значения информационных сигналов были истинными в эти моменты времени.

У синхронных триггеров смены сигналов на входах еще не достаточно для срабатывания. Необходим дополнительный командный импульс, который подается на синхронный, или так называемый тактирующий вход.

Основной недостаток асинхронных триггеров, ограничивающий их использование в быстродействующих схемах, – незащищенность перед опасными состязаниями сигналов. Явление состязаний или, как его еще называют, гонок, состоит в том, что сигналы, поступают на разные информационные входы триггера, пройдя различное число элементов. Вследствие задержек распространения между сигналами возможны временные сдвиги. Состязания сигналов могут оказаться причиной ложных срабатываний триггеров. Тактированием этот недостаток можно устранить.

Синхронные триггеры по сравнению с асинхронными обладают более высокой помехоустойчивостью. Опрокидывание синхронных триггеров происходит только при участии тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входные сигналы, ровно как и помехи различного происхождения, триггер не реагирует. В асинхронном же управлении опрокидывание может произойти как от полезного сигнала, так и от помехи.

Асинхронный триггер по большей части используют в качестве ключей, прерывателей, делителей частоты. В вычислительной и цифровой технике, связанной с обработкой информации, везде используют синхронные системы.

Способы управления триггерами

В зависимости от того, какой параметр входных сигналов используют для записи информации, триггеры подразделяются на три категории: со статическим управлением (управление по уровню входного сигнала), динамическим управлением (управление по фронту или срезу) и двухступенчатые триггеры. Для асинхронных триггеров в качестве управляющих служат сигналы на информационных входах. Применительно к синхронным триггерам управляющим сигналом служит тактовый импульс, так как считается, что к его приходу смена сигналов на информационных входах уже завершилась.

|

|

|

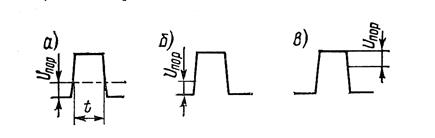

а) б) в)

Рисунок 4 – Момент срабатывания триггеров с разными способами управления: а) статическим; б) прямым динамическим (по фронту 0,1); в) инверсным динамическим (по срезу 1,0);

t – время, в течение которого может происходить обратный переброс

Специфика синхронных триггеров со статическим управлением такова, что в продолжение времени действия тактового сигнала смена сигналов на информационных входах вызовет новое срабатывание. Другими словами, синхронные триггеры со статическим управлением при активном состоянии тактового входа ведут себя подобно асинхронным.

От этого свободны триггеры с динамическим двухступенчатым управлением.

Из структурной схемы двухступенчатого триггера следует, что переключение ведущей ступени (ТМ) происходит с задержкой tЗД.ТМ = 3tЗАД.СР. Такой же должна быть минимальная длительность тактового сигнала,  τB ≥ 3tЗАД.СР. Задержка переключения ведомой ступени (TS) складывается из задержки распространения сигнала в инверторе DD1/1 и в триггере, т.е. tЗД.ТМ = 4tЗД.Р.СР. Таким образом, разрешающее время

τB ≥ 3tЗАД.СР. Задержка переключения ведомой ступени (TS) складывается из задержки распространения сигнала в инверторе DD1/1 и в триггере, т.е. tЗД.ТМ = 4tЗД.Р.СР. Таким образом, разрешающее время

tР ≥ tЗД.ТМ + tЗД.TS = 7tЗД.Р.СР,

максимальная входная частота

fМАК = 1/(7tЗД.Р.СР).

JK-триггеры

Этот тип триггеров (рис. 5) не имеет неопределенных состояний. Функциональная особенность JK-триггера состоит в том, что при всех входных комбинациях, кроме одной Jn = Kn = 1, они действуют подобно RS-триггеру, причем вход J играет роль входа S, а К-вход соответствует R-входу. При входной комбинации Jn = Kn = 1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение.

JK-триггеры относятся к универсальным устройствам. Их универсальность имеет двойственный характер. Во-первых, эти триггеры могут быть применены в регистрах, счетчиках, делителях частоты и других узлах, и, во-вторых, путем определенного соединения выводов они обращаются в триггеры других типов.

Рисунок 5 – JK-триггер

При входных сигналах J = H(0) и K = H(0) состояние выходов не меняется, оно сохраняется таким, каким было в момент установки. Напряжение низкого уровня (Н) на одном входе элемента ТТЛ отменяет прохождение от других его входов и удерживает выходной сигнал на высоком уровне. Когда через входы

J и K в момент времени установлены противоположные уровни, то в последующий момент выходы JK-триггера устанавливаются в такие же состояния, как и RS-триггер.

При подаче на входы J и K одновременно напряжений высокого уровня (входы можно просто соединить) триггер перебрасывается, переходит в состояние, противоположное предыдущему. Если было Qn = B(1),  n = H(0), то станет Qn + 1 = H(0) и

n = H(0), то станет Qn + 1 = H(0) и  n + 1 = B(1).

n + 1 = B(1).

Для надежной работы триггерных ячеек в многоразрядных устройствах управления (счетчиках, регистрах) предназначены двухступенчатые триггеры (master – slave).

С учетом тактового сигнала С функция перехода JK-триггера описывается выражением

Q+ =  JdC

JdC  Q

Q  ,

,

где импульсный сигнал dC срабатывает по срезу с 1 на 0. Из этого следует, что при dC = 0 Q+ = Qr, т. е. изменения информации сигналов J и K, возникающие при переходном процессе, не могут изменить состояние триггеров. Информационные сигналы J и K не должны изменяться только в дискретные моменты времени при dC = 1. Длительность сигналов С = 1 и С = 0 не регламентируется.

Рисунок 6 – Карта Карно для функции перехода JK-триггера

D-триггеры

D-триггеры (рис. 7) в отличие от JK имеют для установки в состояние

0 и 1 один информационный вход (вход D – data). Функциональная особенность триггеров типа D состоит в том, что сигнал на выходе Q в такте n + 1 повторяет входной сигнал Dn в предыдущем такте n и сохраняет (запоминает) это состояние до следующего тактового импульса. Другими словами, D-триггер задерживает на один такт информацию, существующую на входе D. Основание метки D – это первая буква английского слова delay – затяжка, задержка. D-триггеры так и называют – триггерами задержки. Закон функционирования D-триггера очень прост: Q+ = Dn.

Рисунок 7 – D-триггер

Для D-триггера требуется всего четыре внешних вывода: вход данных D, тактовый вход С и два выхода Q и  . Дополнительными входами могут быть асинхронные входы установки S и R, они также являются приоритетными по отношению к входам D и С.

. Дополнительными входами могут быть асинхронные входы установки S и R, они также являются приоритетными по отношению к входам D и С.

На вход D подается напряжение уровнем «1» или «0». Если в последующий момент времени придет положительный перепад тактового импульса состояния, на выходах Qn + 1 и  n + 1 показана диаграмма записи в D-триггер напряжений высокого и низкого входных уровней и их считывание. Непременное условие правильной работы D-триггера – это наличие защитного интервала времени запускающего импульса UD (наличие уровня на D) перед тактовым UC (перепад времени tn + 1 – tn оговаривается справочными данными на D-триггер datachit).

n + 1 показана диаграмма записи в D-триггер напряжений высокого и низкого входных уровней и их считывание. Непременное условие правильной работы D-триггера – это наличие защитного интервала времени запускающего импульса UD (наличие уровня на D) перед тактовым UC (перепад времени tn + 1 – tn оговаривается справочными данными на D-триггер datachit).

В заключение рассмотрим схемы взаимного преобразования триггеров. На рис. 8, а – в показаны схемы делителей частоты на RST-, D- и JK-триггерах соответственно. Триггер D возможно преобразовать в Т (делитель на 2), снабдив делитель дополнительным входом разрешения ЕI (рис. 8, г). В режиме

D-триггера можно использовать JK- и RST-триггеры (рис. 8, е). Из RST-триггера можно получить JK-триггер по схеме (рис. 8, ж).

Рисунок 8 – Схемы взаимного преобразования триггеров

Контрольные вопросы

Триггеры

Асинхронный RS-триггер

Синхронный RS-триггер

D-триггер

JK-триггер

Двухступенчатый JK-триггер

Т-триггер, срабатывающий по срезу

Способы управления триггерами

Триггеры с динамическим двухступенчатым управлением

Литература

а) основная литература

1. Афанасьева Н.А., Булат Л.П. Электротехника и электроника: Учебное пособие [Электронный ресурс]. - 2-е изд., перераб. и дополн. - СПб.: СПбГУНиПТ, 2009. - 181 с. ISBN/ISSN:5-89565-117-8 // Единое окно доступа к информационным ресурсам. URL: http://window.edu.ru/resource/926/77926 (дата обращения: 11.09.2013).

2. Глинкин Е.И. Схемотехника аналоговых интегральных схем: учебное пособие [Электронный ресурс]. / Е.И. Глинкин. - 2-е изд., доп. - Тамбов: Изд-во ФГБОУ ВПО "ТГТУ", 2012. - 152 с. ISBN/ISSN:978-5-8265-1072-8 // Единое окно доступа к информационным ресурсам. URL: http://window.edu.ru/resource/453/76453 (дата обращения: 11.09.2013).

3. Кузнецов Б.Ф. Электронные промышленные устройства: Учебное пособие [Электронный ресурс]. - Изд-во: Ангарской государственной технической академии, 2010. - 151 с. ISBN/ISSN:978-5-89864-072-9 // Единое окно доступа к информационным ресурсам. URL:http://window.edu.ru/resource/335/73335 (дата обращения: 11.09.2013).

4. Кулик В.Д. Силовая электроника. Автономные инверторы, активные преобразователи: Учебное пособие [Электронный ресурс]. - СПб.: СПбГТУРП, 2010. - 90 с. // Единое окно доступа к информационным ресурсам. URL: http://window.edu.ru/resource/330/76330 (дата обращения: 11.09.2013).

5. Муромцев Д.Ю. Основы проектирования электронных средств: учебное пособие [Электронный ресурс] / Д.Ю. Муромцев, И.В. Тюрин. - Тамбов: Изд-во ГОУ ВПО ТГТУ, 2011. - Ч. 1. - 80 с. ISBN/ISSN:978-5-8265-0980-7 // Единое окно доступа к информационным ресурсам. URL:http://window.edu.ru/resource/512/76512 (дата обращения: 11.09.2013).

б) дополнительная литература

1. Гаврилов С. А. Искусство схемотехники. Просто о сложном. – СПб.: Наука и Техника, 2011. – 352 с.

2. Горошков Б. И. Электронная техника: учеб. пособие / Б. И. Горошков, А. Б. Горошков. – 2-е изд., стер. – М.: Издательский центр «Академия», 2008. – 320 с.

3. Ефимов И.Е. Козырь И.Я. Основы микроэлектроники: Учеб. пособие. – М.: Лань, 2011. – 384 с.

4. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. – М.: Мир, 2001. – 379 с.

5. Новожилов О.П. Электротехника и электроника: Учебник. – М.: Изд-во Юрайт, 2012. – 653 с.

6. Схемотехника электронных средств: учеб. пособие для студ. высш. учеб. заведений / Б.Ф.Лаврентьев. – М.: Издательский центр «Академия», 2010. – 336 с.

7. Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том I: Пер. с нем. – М.: ДМК Пресс, 2008. – 832 с.

8. Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том II: Пер. с нем. – М.: ДМК Пресс, 2007. – 942 с.

9. Топильский В. Б. Схемотехника измерительных устройств / В. Б. Топильский. – М.: БИНОМ. Лаборатория знаний, 2010. – 232 с.

10. Майер Р.В. Основы электроники. Курс лекций: Учебно-методическое пособие. – Глазов: ГГПИ, 2011. – 80 с.

Приложение А

(справочное)

Данные по микросхемам

К561ТР2

Микросхема К561ТР2 содержит четыре RS-триггера, что удобно для накапливания 4-разрядных двоичных слов. Выходы каждой защелки имеют третье Z-состояние. Сигнал разрешения — общий для четверки триггеров подается на вход EI. Если на этом входе нулевой уровень, то выходы размыкаются (переходят в Z-состояние).

Каждый триггер состоит из RS-защелки (два инвертора ИЛИ),инвертора и ключа коммутации КК, который управляется от шин Е и Е, объединяющих все четыре канала. Триггер имеет два входа данных R и S. Все состояния триггерного канала сведены в таблицу. Низкие уровни на входах S и R не меняют состояние выхода Q. Если S = l и R = l, триггер эту информацию не защелкивает, но на выходе Q транслируется сигнал S = l (пока он присутствует). Время перехода к состоянию Z не более 100 нс.

Зарубежным аналогом микросхемы К561ТР2 является микросхема CD4043A.

К561ТВ1

2-х ступенчатый JK-триггер

К561ТМ2

Состоит из двух D-триггеров. Его работа от обычного RS-триггера отличается тем, что имеется еще 2 дополнительных входа D и С. Вход С является тактовым (синхронизирующим), а вход D информационным. При этом входа S и R имеют приоритет. При принудительной установке триггера по входам SR, сигналы, присутствующие на D и C не влияют на его состояние.

По входам D и C триггер работает следующим образом: при появлении лог.1 на входе С, на прямом выходе Q появляется уровень сигнала соответствующий сигналу присутствующему на входе D, т.е. происходит перенос состояния со входа D на выход Q. После исчезания лог. 1 на входе С триггер останется в этом же состоянии независимо от того что присутствует на входе D. Но если на D изменить предшествующее состояние на противоположное и при удержании этого уровня на вход С снова подать синхроимпульс, то состояние триггера изменится уже в соответствии с состоянием сигнала на входе D в данный момент, т.е. произойдет переключение выхода.

Такой триггер используется для сохранения в памяти двоичного сигнала, или еще по-другому он называется триггер задержки (памяти).

Нумерация выводов начинается от ключа на корпусе против часовой стрелки. По уровню сигналов на входах и выходах совместима с импортными микросхемами серии 40хх.

Аналоги К561ТМ2 – CD4013, HEF4013.

К561ТМ3

4 одноступенчатых D-триггера с общими входами синхронизации, прямыми и инверсными выходами

|

|

|