|

Разработка принципиальной схемы памяти FIFO , LIFO

|

|

|

|

Целью данного дипломного проекта является разработка РЗУ типа очередь (РЗУ типа FIFO) и стекового РЗУ (РЗУ типа LIFO)

Разработка принципиальная схема памяти типа FIFO.

Исходя из структурной схемы памяти типа FIFO представленной на рисунке 3.1, принципиальная схема должна состоять из следующих элементов:

двух восьми разрядных универсальных регистра сдвига с последовательном портом ввода и параллельным портом ввода - вывода. Для данной схемы подходит регистр на микросхеме КР1533ИР24, режимы работы регистра приведены в таблице 4.1

четырех разрядного двоичный счетчика. Для данной схемы подходит четырех разрядный двоичный реверсивный счетчик, на микросхеме КР1533ИЕ7 режим работы счетчика приведен в таблице 4.2,

синхронный D - триггер. Для данной схемы подходит D - триггер на микросхеме КР1533ТМ2.

Таблица 4.1 Режимы работы регистра К1533ИР24

| Режим | Вход | Вход/выход | Выход | ||||||||||||||||||||||||||||||||||||

| R | S0 | S1 | EZ1 | EZ2 | C | DS7 | DS0 | ZD1 | ZD2 | ZD3 | ZD4 | ZD5 | ZD6 | ZD7 | ZD8 | D1 | D8 | ||||||||||||||||||||||

| Установка «Логический 0» | L | L | X | L | L | X | X | X | L | L | L | L | L | L | L | L | L | L | |||||||||||||||||||||

| L | X | L | L | L | X | X | X | L | L | L | L | L | L | L | L | L | L | ||||||||||||||||||||||

|

| L | H | H | X | X | X | X | X | X | X | X | X | X | X | X | X | L | L | |||||||||||||||||||||

| Удержание | H | L | L | L | L | X | X | X | D10 | D20 | D30 | D40 | D50 | D60 | D70 | D80 | D10 | D80 | |||||||||||||||||||||

| H | X | X | L | L | L | X | X | D10 | D20 | D30 | D40 | D50 | D60 | D70 | D80 | D10 | D80 | ||||||||||||||||||||||

| Сдвиг вправо | H | H | L | L | L |

| X | H | H | D1n | D2n | D3n | D4n | D5n | D6n | D7n | H | D7n | |||||||||||||||||||||

| H | H | L | L | L |

| X | L | L | D1n | D2n | D3n | D4n | D5n | D6n | D7n | L | D7n | ||||||||||||||||||||||

| Сдвиг влево | H | L | H | L | L |

| H | X | D2n | D3n | D4n | D5n | D6n | D7n | D8n | H | D2n | H | |||||||||||||||||||||

| H | L | H | L | L |

| L | X | D2n | D3n | D4n | D5n | D6n | D7n | D8n | L | D2n | L | ||||||||||||||||||||||

| Загрузка | H | H | H | X | X |

| X | X | d1 | d2 | d3

| d4 | d5 | d6 | d7 | d8 | d1 | d8 | |||||||||||||||||||||

Таблица 4.2 Режим работы счетчика КР1533ИЕ7

| Режим работы | Вход | |||

| R | C | «+1» | «-1» | |

| Установка в состояние «логический 0» Запись информации Неактивное состояние Счет прямой Счет обратный | H L L L L | X L H H H | X X H H | X X H H |

Динамические и статические характеристики регистра КР1533ИР24 и счетчика КР1533ИЕ7 приведены в Приложении А.

Синтез комбинационной схемы.

Принимая во внимание то, что режимами работы регистров будет управлять комбинационная схем необходимо произвести ее синтез в следующем порядке:

). Составление таблицы истинности, которые будут отражать зависимость выходных сигналов подаваемых на входы регистров (Е01, Е02 - входы разрешения состояния высокого импеданса, S0 - вход выбора режима, С - тактовый вход) от входных сигналов (сигнала записи WR, синхросигнала 1С, стробирующего сигнала 2С и сигнала с выхода счетчика Q8 - выход четвертого разряда).

Таблица 4.3 Таблица истинности выходных сигналов Е01, Е02 первого регистра от входных 2C, Q8 и WR

| E01 | E02 | 2C | Q8 | WR |

| 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 |

Таблица 4.4 Таблица истинности выходных сигналов Е01, Е02 второго регистра от входных 2C, Q8 и RD

| E01 | E02 | 2C | Q8 | WR |

| 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

Таблица 4.5 Таблица истинности выходного сигнал С первого регистра от входных 2C, Q8, WR и 1С

| С | 1С | 2C | Q8 | WR |

| 1 | 1 | 0 | 1 0 | 0 |

| 0 | 0 | 0 | 1 0 | 0 |

| 0 | 1 | 1 | 0 1 | 0 |

Таблица 4.6 Таблица истинности выходного сигнал С второго регистра от входных 2C, Q8, WR и 1С

| С | 1С | 2C | Q8 | WR |

| 1 | 1 | 0 | 0 1 | 0 |

| 0 | 0 | 0 | 0 1 | 0 |

| 0 | 1 | 1 | 1 0 | 0 |

Таблица 4.7 Таблица истинности выходного сигнал S0 первого регистра от входных Q8, WR

| S0 | Q8 | WR |

| 0 | 1 | 0 |

| 0 | 0 | 0 |

Таблица истинности выходного сигнал S0 второго регистра от входных Q8, WR точно такая же как и для первого.

|

|

|

). Составление функциональных зависимостей исходя из таблиц.

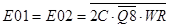

Исходя из таблицы истинности 4.3 составляются функциональные зависимости:

Исходя из таблицы истинности 4.4 составляются функциональные зависимости:

Исходя из таблицы истинности 4.5 составляются функциональные зависимости:

Исходя из таблицы истинности 4.6 составляются функциональные зависимости:

Исходя из таблицы истинности 4.7 составляются функциональные зависимости:

На основе записанных выражений составим комбинационную схему (рисунок 4.1).

Полная принципиальная схема РЗУ типа FIFO показана на рисунке 4.2.

Данная схема работает в режиме последовательного ввода и параллельного вывода информации и хранит одно 8 - битное слово.

Разработка принципиальная схема памяти типа LIFO.

Схема стекового РЗУ (РЗУ типа LIFO) должна содержать следующие элементы:

четыре восьми - разрядных регистра сдвига, которые должны выполнять алгоритм LIFO. Для данной схемы подходит регистр на микросхеме КР1533ИР13, режимы работы регистра приведены в таблице 4.8.

Таблица 4.8 Режимы работы регистра К1533ИР13

| Входы | Выходы Q0 Q1…Q6 Q7 | ||||||

| Сброс R | Выбор режима | Такто-вый С | Сдвиг | Данных А0-А7 | |||

| М1 | М0 | влево | вправо | ||||

| L H H H H H H H | X X H L L H H L | X X H H H L L L | X L | X X X X X H L X | X X X H L X X X | X X a…h X X X X X | L L L L Q00 Q10 Q60 Q70 a b g h H Q0n Q5n Q6n L Q0n Q5n Q6n Q1n Q2n Q7n H Q1n Q2n Q7n L Q00 Q10 Q60 Q70 |

- счетчика для установки флага. Для данной схемы подходит четырех разрядный двоичный реверсивный счетчик, на микросхеме КР1533ИЕ7 режим работы счетчика приведен в таблице 4.2.

На рисунке 4.3 показана принципиальная схема стекового РЗУ (РЗУ типа LIFO).

Данная схема может хранить восемь, четырех разрядных слова. Запись четырех разрядных слов через шину ввода DI производится при наличии сигнала на входах регистров М0 = 1 и М1 = 0 и при подачи синхросигнала С. После ввода восьмого слова на выходе Q4 счетчика появляется сигнал флага AN, который служит сигналом для передатчика свидетельствующего о том что стек заполнен и необходимо прекратить подачу четырех разрядных слов и сигналов записи, для того чтобы избежать переполнения стека и соответственно потере ранее записанных данных. После этого на входы М0 и М1 регистров подается сигнал низкого уровня по которому в регистрах хранится записанная информация до тех пор пока приемник принимающий записанную в стеке информацию не подаст сигнал чтения. При подачи сигнала чтения на входы М0 = 0 М1 = 1 регистров и по положительному фронту синхросигнала С приемник считывает информацию в порядке обратном записи. После того как приемник считал последнее слово на выходе Q4 счетчика формируется сигнал флага AN, которая служит сигналом для передатчика о том что регистры пустые и можно вводить следующие восемь четырех разрядные слова.

|

|

|

Рисунок 4.1 Комбинационная схема

Рисунок 4.3 Принципиальная схема стекового РЗУ (РЗУ типа LIFO)

Рисунок 4.2 Полная принципиальная схема РЗУ типа FIFO показана на рисунке 4.2

|

|

|