|

Микросхемы, содержащие элементы памяти

|

|

|

|

Микросхема К155ТМ2 (рис. 5.27, табл. 5.18). Эта микросхема содержит два D-трштера. Поясним работу D-триггеров микросхемы К155ТМ2, пользуясь табл. 5.18. Каждый D-триггер этой микросхемы имеет вход предустановки S и сброса R. Из таблицы видно, что при подаче низкого уровня на вход S на прямом выходе триггера Q появится высокий уровень, а на инверсном выходе Q - низкий Уровень. Низкий уровень на входе R устанавливает выходы триггера в противоположные состояния. Если низкий уровень присутствует хотя бы на одном из входов S или R, то сигналы на входах С и D никак не влияют на состояние триггера. Если сигнал низкого уровня подавать одновременно на входы S и R, то на обоих выходах (прямом и инверсном) установится высокий уровень; если эти сигналы одновременно снять, то триггер может установиться в любое состояние, поэтому такой ситуации необходимо избегать.

Рис. 5.27. Микросхема К155ТМ2

| Таблица 5.18 | |||||

| Входы | Выходы | ||||

| S | R | С | D | Q | Q |

| L | Н | X | X | Н | L |

| Н | L | X | X | L | H |

| L | L | X | X | Н | H |

| Н | Н | L | X | Qs | Qs |

| Н | Н | Н | X | Qs | Qs |

| Н | Н | X | Qs | Qs | |

| Н | Н | t | Н | Н | L |

| Н | Н | t | L | L | H |

Рис. 5.28. Временная диаграмма работы микросхемы К155ТМ2

Буквой Qs в табл. 5.18 обозначено состояние триггера, которое было до подачи указанных управляющих сигналов. Из табл. 5.18 видно, что низкий уровень, высокий уровень, а также переход от высокого к низкому уровню на входе С никак не влияют на состояние триггера. Только переход от низкого уровня к высокому устанавливает на выходе триггера тот уровень, который в данный момент присутствует на входе D, а на инверсном выходе устанавливает инверсный уровень. На рис. 5.28 приведена временная диаграмма, иллюстрирующая работу D-триггера микросхемы К155ТМ2.

|

|

|

Таблица 5.19

| Входы | Выходы | ||

| С | D | Q | |

| L | X | qs | Qs |

| Н | Н | Н | L |

| Н | L | L | Н |

Рис. 5.29. Микросхема К155ТМ7

Рис. 5.30. Временная диаграмма работы микросхемы К155ТМ7

Микросхема К155ТМ7 (рис. 5.29, табл. 5.19). Эта микросхема содержит четыре D-триггера.

Каждый триггер имеет вход D, выходы Q и Q и управляющий вход С, но управляющие входы всех триггеров не подключены к отдельным выводам микросхемы, а соединены попарно и подключены к выводам 4 и 13. Поэтому триггерами этой микросхемы нельзя управлять по отдельности. Из табл. 5.19 видно, что если на управляющем входе С низкий уровень, то уровень сигнала на выходе триггера Q остается неизменным, а если высокий уровень, то уровень сигнала на выходе триггера повторяет уровень на входе D. Временная диаграмма, поясняющая работу триггера, приведена на рис. 5.30. Триггер такого типа часто называют "защелкой", так как с его помощью можно в любой момент зафиксировать уровень какого-либо сигнала.

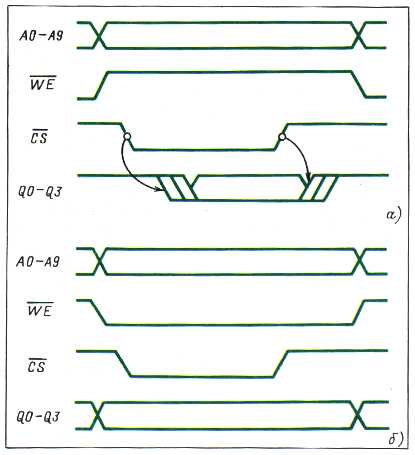

Микросхема КР541РУ2 (рис. 5.31). Эта микросхема является оперативным запоминающим устройством емкостью 4 Кбит с организацией 1024x4 бита. Это значит, что внутри микросхемы содержится 1024 запоминающие ячейки, каждая из которых состоит из четырех двоичных разрядов. Для адресации ячеек памяти внутри микросхемы имеется 10 адресных входов АО — А9. Каждой комбинации сигналов на этих входах соответствует одна ячейка. Для передачи информации в ячейки памяти при записи и из ячеек памяти при считывании имеются выводы QO — Q3. При записи информации эти выводы работают как входы, а при считывании — как выходы с открытым коллектором. Вход WE управляет режимом записи и считывания: при высоком уровне на этом входе микросхема работает в режиме считывания, при низком — в режиме записи. Вход CS управляет работой выводов QO — Q3. При высоком уровне на этом входе информация не может быть считана или записана. В режиме считывания низкий уровень на входе CS разрешает работу выводов QO — Q3 как выходов, а в режиме записи — как входов. Временные диаграммы работы микросхемы в режиме записи считывания приведены на рис. 5.32.

|

|

|

Микросхема КР556РТ4 (рис. 5.33). Эта микросхема является постоянным запоминающим устройством емкостью 1 Кбит с организацией 256x4 бита, т. е. внутри микросхемы содержится 256 ячеек памяти, каждая из которых состоит из четырех разрядов. Информация, записанная в ПЗУ, не стирается при выключении напряжения питания. Для записи информации в ПЗУ используется специальное устройство, называемое программатором. Схема программатора для микросхемы К556РЕ4 (старое название микросхемы КР556РТ4) и режим записи информации не приводятся в этой книге.

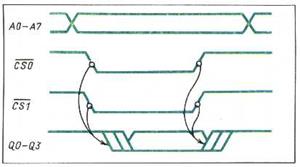

Микросхема КР556РТ4 имеет восемь входов АО-А7 для адресации ячеек памяти, четыре выхода с открытым коллектором QO — Q3 для считывания содержимого ячейки и два управляющих входа CSO и CS1. Считывание информации может происходить только тогда, когда на обоих входах CSO и CS1 низкий уровень (рис. 5.34).

Рис. 5.31. Микросхема КР541РУ2

Рис. 5.33. Микросхема КР556РТ4

Рис. 5.32. Временная диаграмма работы микросхемы КР541РУ2

Рис. 5.34. Временная диаграмма работы микросхемы КР556РТ4 при считывании

СТРУКТУРА

И ФУНКЦИОНИРОВАНИЕ МИКРОПРОЦЕССОРНОГО БЛОКА

МИКРОПРОЦЕССОР КР580ИК80А

В предыдущих главах уже приводились некоторые данные о микропроцессоре КР580ИК80А. В этой главе будет продолжено описание этого микропроцессора в основном с точки зрения электронных или, как говорят, аппаратурных особенностей его устройства и работы. Микропроцессор КР580ИК80А представляет собой центральный процессорный элемент, выполненный по и-МОП технологии в виде одной микросхемы. Микросхема упакована в прямоугольный пластмассовый корпус с двухрядным расположением выводов. Серия КР580 является развитием серии К580 и содержит несколько больших интегральных схем, на базе которых можно эффективно реализовывать различные микропроцессорные системы. Микросхема КР580ИК80А содержит 5000 транзисторов и имеет 40 выводов.

Приведем некоторые типовые характеристики микропроцессора.

Диапазон рабочих температур, °С............... От -10 до+70

|

|

|

Максимальная тактовая частота, МГц............. 2,5

Напряжение источников питания, В:

U1.......-......................... +12±0,6

U2............................... +5 ±0,25

Uз................................ -5 ±0,25

Потребляемая мощность, мВт................. 1500

Быстродействие (количество операций типа регистр-регистр в секунду)......................... 625 000

Рис. 6.1. Микропроцессор КР580ИК80А

Рис. 6.1. Микропроцессор КР580ИК80А

Каждый выход микропроцессора обеспечивает I0вых не более 1,8 мА и I1вых не более 0,1 мА, т. е. может быть нагружен одним стандартным ТТЛ-входом серии К155. Напряжения питания необходимо подавать или одновременно, или в последовательности U1, U2, U з и снимать в обратной последовательности. Микропроцессор КР580ИК80А относится к универсальным микропроцессорам, он имеет возможность работать в самых разнообразных режимах. Тот или иной режим может не использоваться в каждой конкретной конструкции микро-ЭВМ. Условное графическое изображение микропроцессора приводится на рис. 6.1, а функции выводов — в табл. 6.1.

Таблица 6.1

| Обозначение вывода | Функциональное назначение вывода | |

| АО-А15 DO-D7 | Выходы, линии шины адреса Двунаправленные линии шины данных | |

| Сигналы управления шинами | ||

| DBIN | Выход, признак того, что шина данных находится в состоянии приема информации | |

| WR HOLD | Выход, признак того, что шина данных находится в состоянии передачи информации Вход, переводит шины данных и адреса в состояние высокого сопротивления | |

| HLDA | Выход, признак того, что шины данных и адреса находятся в состоянии высокого сопротивления | |

| READY | Вход, переводит микропроцессор в состояние ожидания | |

| WAIT | Выход, признак того, что микропроцессор находится в состоянии ожидания | |

| Обозначение вывода | Функциональное назначение вывода | |

| SYNC | Выход, признак того, что по шине данных передается управляющее слово микропроцессор | |

| INTERRUPT INTE | Сигналы управления прерываниями Вход, запрос прерывания работы микропроцессора Выход, соответствует состоянию внутреннего триггера, управляющего прерыванием микропроцессора | |

| Ф1,Ф2 | Сигналы синхронизации Входы для тактовых импульсов | |

| RESET | Сигнал начального запуска Вход, вызывает запись в программный счетчик адреса нулевой ячейки памяти | |

СИНХРОНИЗАЦИЯ

|

|

|

Как уже известно из § 4.3, каждая команда выполняется микропроцессором не мгновенно, а как последовательность машинных циклов. Микропроцессор КР580ИК80А имеет 10 типов машинных циклов (табл. 6.2), и все его команды состоят из комбинаций только этих циклов.

В состав команды может входить от одного до пяти циклов. Каждый машинный цикл также не является неделимой операцией, а состоит из машинных тактов. В состав машинного цикла микропроцессора КР580ИК80А может входить от трех до пяти машинных тактов. Машинный такт не является таким же законченным процессом, как машинный цикл, большинство сигналов микропроцессора вырабатываются в одном такте и снимаются в другом. Поэтому для машинных тактов нельзя привести такую же классификацию, как для машинных циклов. Как и в гл. 4, в тексте и на рисунках будем обозначать такты одного цикла Tl, T2,... и т. д., циклы одной команды С1,С2,... и т. д.

Для того чтобы сформировать интервал времени, соответствующий одному машинному такту, на входы микропроцессора Ф1 и Ф2 подаются тактовые импульсы (синхроимпульсы). Длительность машинного такта равняется одному периоду синхроимпульсов. Все внутренние операции микропроцессора и формирование внешних сигналов происходят в моменты времени, определяемые синхроимпульсами.

Рис. 6.2. Тактовые импульсы Таблица 6.2

| Управляющее слово, состоящее из разрядов шины данных DO — D7 | ||||||||

| Тип цикла | DO | Dl | D2 | D3 | D4 | D5 | D6 | D7 |

| ВЫБОРКА КОМАНДЫ | L | H | L | L | L | H | L | H |

| ЧТЕНИЕ ИЗ ПАМЯТИ | L | H | L | L | L | L | L | H |

| ЗАПИСЬ В ПАМЯТЬ | L | L | L | L | L | L | L | L |

| ЧТЕНИЕ ИЗ СТЕКА | L | H | H | L | L | L | L | H |

| ЗАПИСЬ В СТЕК | L | L | H | L | L | L | L | L |

| ВВОД С ВНЕШНЕГО УСТРОЙСТВА | L | H | L | L | L | L | H | L |

| ВЫВОД НА ВНЕШНЕЕ УСТРОЙСТВО | L | L | L | L | H | L | L | L |

| ПРЕРЫВАНИЕ | H | H | L | L | L | H | L | L |

| ОСТАНОВ | L | H | L | H | L | L | L | H |

| ПРЕРЫВАНИЕ ВО ВРЕМЯ ОСТАНОВА | H | H | L | H | L | H | L | L |

К уровням напряжения, частоте, фронтам и фазе синхроимпульсов предъявляются особые требования (рис. 6.2). Входы Ф1 и Ф2 не являются ТТЛ-входами. Это единственное исключение для микропроцессора КР580ИК80А. Для Ф1 и Ф2 напряжение сигнала низкого уровня должно быть в пределах от -0,3 до 0,8 В, а напряжение сигнала высокого уровня - в пределах от 10 до 12 В. Частота синхроимпульсов должна быть не более 2,5 МГц, переход с одного уровня напряжения на другой должен иметь длительность 20-30 не. На рис. 6.2,я приводится временная диаграмма сигналов Ф1 и Ф2, которая может быть получена с помощью микросхемы тактового генератора КР580ГФ24, который выпускается специально для микропроцессора КР580ИК80А (см. § 6.4). Из этой диаграммы видно, что если условно разбить период синхроимпульсов на девять интервалов, то сигнал Ф1 будет иметь высокий уровень в первых двух интервалах и низкий уровень во всех остальных, а сигнал Ф2 будет иметь высокий уровень в интервалах с третьего по седьмой и низкий уровень во всех остальных.

|

|

|

Сигналы Ф1 и Ф2 могут иметь и более простую временную диаграмму (рис. 6.2,6). Если не пользоваться для их генерации микросхемой КР580ГФ24, то получить такую диаграмму проще, чем стандартную. Требования к уровням, фронтам и частоте остаются такими же, как и для стандартной временной диаграммы.

|

|

|