|

Расчет буферного запоминающего устройства

|

|

|

|

Хранит коды символов, которые будут отображаться на экране.

Коды символов в буферном запоминающем устройстве (БЗУ) располагаются в том порядке, в каком они будут выводиться.

Исходные данные для расчета:

число текстовых строк Nтс=9,6;

число знаков в текстовой строке Nзтс=65,5;

основание кода алфавита Nа=30;

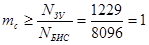

Находим требуемую разрядность БЗУ

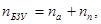

где  – разрядность обеспечения алфавита;

– разрядность обеспечения алфавита;

– разрядность обеспечения признаков.

– разрядность обеспечения признаков.

По заданию

,

,  .

.

Выбираем требуемое число адресных разрядов

Адресация двух координатная:

младшие разряды адреса поступают от счетчика знаков маркера (регенерации);

старшие разряды адреса поступают от счетчика текстовых строк маркера (регенерации).

– количество младших разрядов адреса

– количество младших разрядов адреса

– количество старших разрядов адреса.

– количество старших разрядов адреса.

минимальное число адресных разрядов К=12.

Расчет числа ячеек памяти БЗУ

Количество ячеек памяти определяется по следующей формуле:

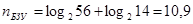

Следовательно:

бит

бит

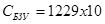

Определим требуемое быстродействие БИС ОЗУ относительно адреса:

.

.

Выбираем БИC ОЗУ:

По быстродействию, информационной ёмкости, и организации подходит микросхема ОЗУ КР537РУ16А, имеющая информационную емкость СБИС = 8к´8, NБИС=8k, nБИС=8. Такая организация обеспечивает минимальное число интегральных схем в модуле при минимальной избыточности. Особенностью этой микросхемы является двунаправленный вход-выход с тремя устойчивыми состояниями

| Справочные данные микросхемы: | |

| Входной ток логического нуля IIDL | не менее 0,4 мА |

| Входной ток логической единицы IIDH | не более 0,04 мА |

| Входная емкость по информационному входу БИС CID | не более 4 пФ |

| Время выборки адреса tBA | не более 60 нс |

| Потребляемая мощность | 880 мВт |

|

|

|

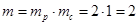

Рассчитываем число БИС ОЗУ в ряду матрицы, необходимое для получения двенадцати разрядного информационного слова:

.

.

Определим число рядов матрицы:

.

.

Общее число БИС ОЗУ:

.

.

Такое количество БИС ОЗУ обеспечивает объем памяти

СБЗУ=8к x 16 бит.

Полученная избыточность определяется тем, что NЗУ в данном случае не кратно NБИС.

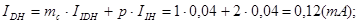

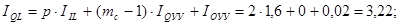

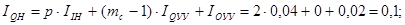

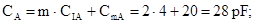

Определяем токовую IDL и IDH и емкостные Cd нагрузки для схем ввода информации в ОЗУ по формулам (mc = 1– число рядов матрицы, p = 2 – общее число микросхем):

Определим токи нагрузки и величину емкостной нагрузки на информационные выходы БИС ОЗУ по формулам:

Где IQУT = 20μА – ток утечки невыбранного выхода;

IОУT = 20мкА – ток утечки схем ввода информации;

CQO=10 pF – выходная емкость одного информационного выхода БИС ОЗУ.

CmQ=10 pF – монтажная емкость цепи информационного

CОQ=20 pF – выходная емкость схем ввода информации.

Полученные значения токов и емкостей нагрузки удовлетворяют соответствующим требованиям для ИС серии КР537.

Определяем токи нагрузки и емкостную нагрузку по адресным цепям БИС ОЗУ по формулам:

Для схем серии КР537 указанная нагрузка допустима.

Рассчитаем потребляемую мощность БЗУ.

Потребляемая мощность БИС КМ132РУ13А 880mW.

Поэтому потребляемая мощность ОЗУ:

РБЗУ=2∙0,880= 1760 (W).

Рисунок 2 – Принципиальная электрическая схема БЗУ

4 Выбор мультиплексора

Мультиплексор – устройство, осуществляющее коммутацию цифровых сигналов с n информационных входов на один выход. В нашем случае n =3 (необходимо коммутировать на адресную шину БЗУ содержимое счетчиков маркера или счетчиков регенерации).

В нашем случае необходимо коммутировать 12 цифровых (бинарных) сигналов.

В качестве мультиплексора применим микросхему К555КП11, содержащую в одном корпусе 4 мультиплексора из двух направлений в одно. В связи с тем, что нам необходимо коммутировать 12 цифровых сигналов, используем 3 микросхемы К555КП11.

|

|

|

Микросхема К555КП11 имеет следующие параметры:

–Мин. вых. напряжение высокого уровня,В 2,5

–Макс. вых. напряжение низкого уровня,мВ 480

–Макс. вх. ток высокого уровня,мкА 20

–Макс. вх. ток низкого уровня,мкА 760

–Макс. ток потребления,мА 9,7

–Напряжение источника питания,В 5

–Временная задержка распред. сигнала, нс 21

Рисунок 3 – Принципиальная электрическая схема мультиплексора

|

|

|

12 |