|

Структура тактируемых триггеров

|

|

|

|

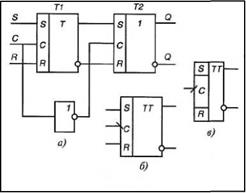

Тактируемый RS - триггер (рис.2,а). Схема такого триггера (собранного на элементах ИЛИ-НЕ) содержит асинхронный RS-триггер T1 и два конъюнктура входной логики. Последние передают переключающую логическую 1 с информационного S- или R-входа на соответствующие входы Т1 только при наличии на синхронизирующем входе С логической 1. При С=0 информация с S- и R-входов на триггер Т1 не передается.

Рассматриваемый триггер может быть выполнен и на запоминающей ячейке, реализованной на элементах И-НЕ.

Условное изображение тактируемого триггера приведено на рис. 2,б. В тексте тактируемый RS-триггер сокращенно обозначают как RSC-триггер.

Синхронизирующие входы триггера могут быть статическими и динамическими. Статический вход не теряет своего управляющего действия, пока на нем присутствует тактовый (синхро) импульс. Такие входы имеет триггер, изображенный на рис.2,а. В присутствии тактового импульса эти триггеры будут менять свое состояние при каждой смене комбинаций логических потенциалов на входах S и R. Динамический синхровход воздействует на состояние выходов триггера в момент своего появления (передним фронтом) или окончания (задним фронтом).

| Рис. 2 |

Двухступенчатый тактируемый RS-триггер (рис.3,а). Каждая ступень такого триггера представляет собой тактируемый RS - триггер. При появлении на входе С логической 1 триггер Т1 воспринимает информацию на входах S и R, определяющую его состояние. В это время на С-входе триггера Т2 за счет инвертора — логический 0, и информация с выходов Т1 не воздействует на Т2. В момент окончания действия логической 1 на входе С (С=0) на выходе инвертора появляется логическая 1, разрешающая перезапись в Т2 информации из Т1. Таким образом, в первую ступень информация с входов S и R записывается с поступлением тактового импульса, т. е. по его переднему фронту; состояние первой ступени передается второй с окончанием тактового импульса, т. е. по его срезу. По этому внешнему проявлению тактирующего импульса C-вход описанного триггера можно рассматривать как динамический.

|

|

|

Условное изображение двухступенчатого RS-триггера, в котором переключение выходов второй ступени триггера происходит перепадом входного сигнала из 1 в 0 (перепадом 1 / 0), приведено на рис.3,б. Условное изображение триггера с C-входом, переключающим триггер перепадом 0/1, приведено на рис. 3, в.

Условное изображение двухступенчатого RS-триггера, в котором переключение выходов второй ступени триггера происходит перепадом входного сигнала из 1 в 0 (перепадом 1 / 0), приведено на рис.3,б. Условное изображение триггера с C-входом, переключающим триггер перепадом 0/1, приведено на рис. 3, в.

| Рис. 3 |

Тактируемый (синхронный) триггер обычно имеет дополнительные асинхронные входы, но которым он вне зависимости от сигнала на тактовом входе переключается в состояние 1 (по входу S) или в 0 (по входу R). Такие входы называют не тактируемыми или асинхронными. Логические потенциалы на них воздействуют на запоминающие ячейки триггера непосредственно (для чего эти ячейки триггера выполнены на трехвходовых элементах), минуя входную логику.

Условное изображение двухступенчатого триггера с инверсными асинхронными входами приведено на рис. 4.

| Рис. 4 |

D - триггер (триггер задержки) – рис.5. D-триггер имеет один информационный D-вход и тактовый С-вход. Он состоит из синхронного RSC-триггера, дополненного инвертором. При С=1 потенциал D-входа передается на S-вход триггера T1 (S=D), а на входе R устанавливается потенциал R=  : сигналы на входах оказываются взаимно инвертированными. Это приводит к тому, что любой сигнал на входе D создает на S- и R-входах комбинацию (S=1, R=0 или S=0, R=1), способную переключить триггер в состояние Q=S=D. Таким образом, при С=1 D-триггер является повторителем: на выходе Q повторяется потенциал входа D. Однако это повторение начинается только с поступлением тактового импульса на вход С, т. е. с задержкой относительно сменившегося потенциала на D-входе. При С=0 триггер Т1 и D-вход разобщены, поэтому S=0 и триггер хранит информацию, поступившую с D-входа при С = 1. Так как в D - триггере информация поступает по одной линии – на D-вход, то явление гонок не проявляется. Поэтому в быстродействующих цифровых устройствах используют D-триггеры.

: сигналы на входах оказываются взаимно инвертированными. Это приводит к тому, что любой сигнал на входе D создает на S- и R-входах комбинацию (S=1, R=0 или S=0, R=1), способную переключить триггер в состояние Q=S=D. Таким образом, при С=1 D-триггер является повторителем: на выходе Q повторяется потенциал входа D. Однако это повторение начинается только с поступлением тактового импульса на вход С, т. е. с задержкой относительно сменившегося потенциала на D-входе. При С=0 триггер Т1 и D-вход разобщены, поэтому S=0 и триггер хранит информацию, поступившую с D-входа при С = 1. Так как в D - триггере информация поступает по одной линии – на D-вход, то явление гонок не проявляется. Поэтому в быстродействующих цифровых устройствах используют D-триггеры.

|

|

|

| Рис. 5 |

JK - триггер. Такой триггер имеет информационные входы J и К, которые по своему влиянию аналогичны входам S и R тактируемого RSС-триггера: при J=1, K=0 триггер по тактовому импульсу устанавливается в состояние Q=1; при J= 0, К=1– переключается в состояние Q=0, а при J = K= 0 – хранит ранее принятую информацию. Но в отличие от RSС-триггера одновременное присутствие логических 1 на информационных входах не является для JK-триггера запрещенной комбинацией.

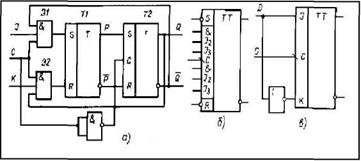

На рис.6,а изображена одна из функциональных схем JK-триггера. Ее отличительной особенностью являются перекрестные связи выходов триггера с входами конъюнкторов входной логики. Благодаря им на эти входы после каждого переключения триггера передаются потенциалы, обратные тем, какие были перед предыдущим переключением, и которые поэтому в состоянии обеспечить новое переключение триггера в противоположное состояние.

Для создания информационных входов J и K элементы Э1 и Э2 входной логики первой ступени выбраны трехвходовыми. Переключение выходов второй ступени триггера происходит перепадом 1/0 на C-входе.

При J=K=0 на входах элементов Э1 и Э2 устанавливаются логические 0, которые для триггеров с прямыми входами являются пассивными сигналами - триггер Т1 и, следовательно, JK-триггер в целом сохраняют прежнее состояние. Чтобы на выходе элемента Э1 появилась логическая 1 (которой триггер Т1 может переключаться в состояние Р= 1), на его входах необходимо присутствие сигналов J =1, С=1, а также логической 1 с выхода  . Аналогично, логическая 1 будет на выходе элемента Э2, когда K=1, С=1 и Q=1. Таким образом, комбинация J=1, К=0 обеспечивает по тактовому импульсу переключение JK-триггера в целом в состояние Q=1, а комбинация J=0, K=1— в состояние Q=0.

. Аналогично, логическая 1 будет на выходе элемента Э2, когда K=1, С=1 и Q=1. Таким образом, комбинация J=1, К=0 обеспечивает по тактовому импульсу переключение JK-триггера в целом в состояние Q=1, а комбинация J=0, K=1— в состояние Q=0.

На рис.6,б приведено изображение JK- триггера с тремя объединенными конъюнкцией входами J, с тремя объединенными конъюнкцией входами K и с входами S и R асинхронной установки. На рис. 11,в показана реализация D-триггера на базе JK-триггера.

|

|

|

| Рис. 6 |

4. Счетные триггеры

Счетный триггер (Т-триггер) отличается тем, что он переключается с поступлением каждого импульса на тактовом входе, называемом в таком триггере счетным. Счетный триггер можно реализовать на базе JK-триггера. Логическая 1 на одном из входов элемента И не определяет потенциал на его выходе, поэтому сочетание J=K=1 не влияет на входную логику первой ступени триггера. Теперь она получает информацию только с выходов триггера (рис.6,а), которая устанавливает ее в положение, когда с приходом счетного импульса начнется очередное переключение - JK-триггер работает в счетном режиме. Реализация счетного режима на JK- триггере приведена на рис 7,а.

Счетный триггер просто реализуется и на D-триггере (рис. 12, б). Если после каждого переключения обеспечить автоматическую смену уровня потенциала на D-входе, то с каждым импульсом на C-входе триггер будет менять свое состояние. Указанная смена потенциала будет осуществляться, если D-вход соединить с выходом  . Вторая перекрестная связь (аналогичная связи в JK- триггере) обеспечивается за счет соединения D-входа с R-входом запоминающей ячейки триггера через инвертор (см.рис.5).

. Вторая перекрестная связь (аналогичная связи в JK- триггере) обеспечивается за счет соединения D-входа с R-входом запоминающей ячейки триггера через инвертор (см.рис.5).

| Рис. 7 |

Счётчики

Счётчики – узлы ЭВМ, которые осуществляют счёт и хранение кода числа подсчитанных сигналов. Они представляют собой цифровые автоматы, в которых новое состояние счётчика определяется его предыдущим состоянием и состоянием логической переменной на входе.

Внутреннее состояние счётчиков характеризуется коэффициентом пересчёта K, определяющим число его устойчивых состояний. Основными параметрами являются разрешающая способность или максимальное быстродействие и информационная ёмкость. Обозначение и назначение выводов реверсивного счётчика показано на рисунке ниже.

Количество разрядов счетчика определяется наибольшим числом, которое должно быть получено в каждом конкретном случае. Для подсчета и выдачи результата счетчики имеют один вход и n выходов, где n-количество разрядов. В общем случае счетчик имеет 2ⁿ устойчивых состояния, включая и 0-е. Количество устойчивых состояний называется коэффициентом пересчета счетчика (М= 2ⁿ). По назначению счетчики подразделяются на: простые и реверсивные.

|

|

|

Простые счетчики- счетчики, работающие только на сложение или вычитание. Суммирующий счетчик предназначен для выполнения счета в прямом направление, т.е. с приходом очередного сигнала показатель счетчика увеличивается на 1. Вычитающий счетчик предназначен для счета в обратном направлении, т.е. с приходом нового сигнала счетчик уменьшается на 1.

Реверсивный счетчик может работать и на сложение и на вычитание.

По способу организации счета счетчики бывают: асинхронные или синхронные.

По способу организации цепей переноса между разрядами счетчика счетчики бывают: последовательные, параллельные и частичнопараллельные.

Двоичный счетчик с параллельным переносом.

| Рис. 8 |

Для повышения быстродействия в счетчике организован параллельный перенос. Параллельный перенос можно сделать в счетчике из 4-х разрядов, т.к. внутренняя схема "И" JK-триггера имеет три входа. Поэтому, при количестве разрядов счетчика больше 4, счетчик разбивается на группы, группа имеет четыре разряда и параллельный перенос, а между группами последовательный перенос. Время срабатывания этого счетчика определяется временем срабатывания JK-триггера.

| Рис. 9. Десятичный счётчик |

Асинхронный счетчик с последовательным переносом, работающий в режиме обратного счета (Рис. 10).

| Рис. 10 |

Регистры

|

|

|