|

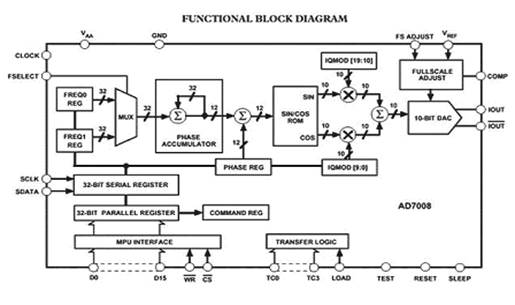

DDS: цифрововй синтезатор AD7008

|

|

|

|

1) 32 разрядный аккумулятор фазы

2) встроенная таблица отсчетов SIN и COS

3) встроенный 10 разрядный ЦАП

4) токовый выход

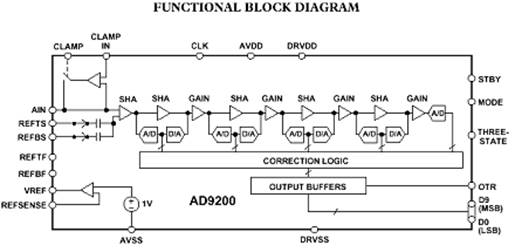

ADC: аналогово-цифровой преобразователь AD9200

1. 10 разрядный КМОП АЦП

2. 20 MSPS

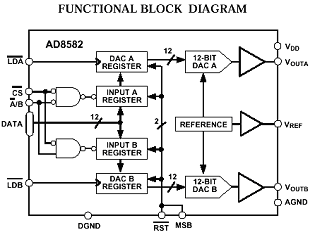

DAC: цифро-аналоговый преобразователь AD8582

Описание взаимодействия микроконтроллера и DDS

Частотная модуляция в DDS осуществляется посредством сложения двух квадратурных составляющих с соответствующими весовыми коэффициентами, задача контроллера получить от РС через последовательный порт (интерфейс RS-232C) байт информации (звуковые данные), рассчитать для него соответствующие весовые коэффициенты квадратурных составляющих и отослать их в DDS.

Во время работы с DDS (PD5 = 0), биты (ЦАП:  ,

,  ,

,  = (not PD5) = 1) и (АЦП:

= (not PD5) = 1) и (АЦП:  = PD6 = 1), т.е. ЦАП и АЦП (Тракт контроля за КСВ) находятся в третьем состоянии и наоборот при работе с ЦАП и АЦП DDS в третьем состоянии.

= PD6 = 1), т.е. ЦАП и АЦП (Тракт контроля за КСВ) находятся в третьем состоянии и наоборот при работе с ЦАП и АЦП DDS в третьем состоянии.

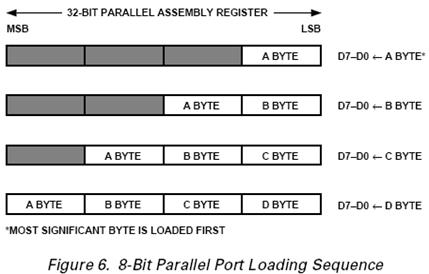

Данные в DDS могут вводиться 8-ми и 16-ти-битными (8- и 16-bit DataBus) словами (MPU Interface D15…D0), после ввода записываются в 32-битный регистр (32-BIT PARALLEL ASSEMBLY REGISTRY).

При использовании микроконтроллера AT90S23 информацию будем вводить побайтно (порт D контроллера – служебный, порт B - информационный).

Таблица битов взаимодействия

| PD6 |

| PD3…PD0 | TC3…TC0 |

| PD6 |

| PB7…PB0 | D7…D8 |

| PD4 | LOAD |

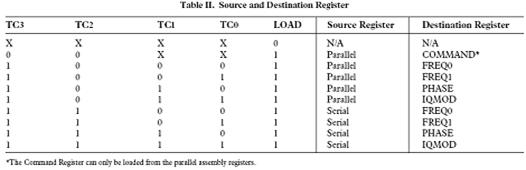

Биты ТС3…ТС0 задают направление записи (в какой из регистров будет записана информация из 32-байтного регистра).

При инициализации DDS контроллер должен выполнить следующее (PD5 =  = 0):

= 0):

1) На вход RESET высокий уровень, происходит обнуление всех регистров DDS (аппаратно).

2) настроить режим работы DDS, для этого в командный регистр отсылаются байты:

| CR0 | 0 | 8-bit DataBus | ||

| CR1 | 0 | Normal Operation | ||

| CR2 | 1 | IQ регистры задействованы

| ||

| CR3 | 0 | синхронизация включена |

3) в регистр частоты FREQ0 REG отсылается 32-разрядное слово, которое является кодом несущей частоты передатчика.

Для этого, в течение четырех циклов записи во входной 32-разрядный регистр (32-BIT PARALLEL ASSEMBLY REGISTRY) побайтно (из порта B контроллера) записывается код. После каждого цикла записи  = 0.

= 0.

Далее через порт D контроллера выставляются биты ТС3…ТС0 задающие направление перевода.

Для регистра FREQ0 REG TC3 = 1; TC2, TC1, TC0 = 0. После этого на входе LOAD = PD4 выставляется высокий уровень и происходит запись содержимого 32-BIT PARALLEL ASSEMBLY REGISTRY в FREQ0 REG. Запись в другие регистры производится аналогично.

На этом инициализация закончена.

При ЧМ весовые коэффициенты квадратурных составляющих должны быть отосланы в регистры IQmod[0,9], IQmod[10,19].

Ниже приведен формат слова отсылаемого в 32-BIT PARALLEL ASSEMBLY REGISTRY.

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | D18 | D19 | D20 | … | D31 | |

| DB0 |

| DB9 | DB10 |

| DB19 |

|

|

| |||||||||||||

| I | Q | X | X | X | |||||||||||||||||

О выборе несущей частоты DDS.

Несущая частота выбирается из двух соображений:

1) В схеме передатчика использованы два преобразования частоты (вверх) (см. структурную схему), если выбрать несущую частоту малой, то зеркальный канал будет находиться слишком близко и для его подавления потребуется ФНЧ высокого порядка. Который к тому же значительно ослабит выходной сигнал DDS.

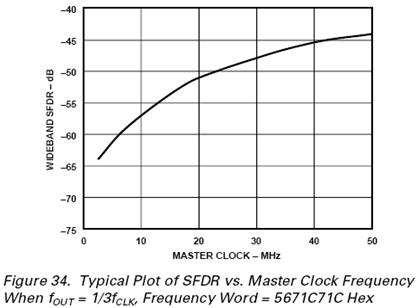

2) С другой стороны если выбрать несущую большой то уменьшится SFDR.

Исходя из этих соображений, а также пользуясь типовой зависимостью SFDR(fCLK)

Выберем значение fOUTmax = 6MHz и fOUTmin = 2MHz при fCLK = 18 MHz.

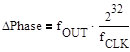

Для определенного значения несущей частоты DDS рассчитывается соответствующее 32-разрядное слово, которое является кодом частоты для DDS и засылается в регистр FREQ0 REG.

- код частоты

- код частоты

|

|

|

| fCLK,MHz | fOUT,MHz | DPhase | DPhaseHex |

| 18. 0 | 2.0 | 0.477219e9 | 1C71C8B8 |

| 2.25 | 0.536871e9 | 20000058 | |

| 2.5 | 0.596523e9 | 238E37F8 | |

| ,,, | ,,, | ,,, | |

| 6.0 | 1.431656e9 | 55555640 |

|

|

|