|

Группа :ВТ-192.2. Руководитель:Мусалимова Н.Қ. СОДЕРЖАНИЕ. Тема 1. Моделирование цифровых узлов комбинационного и последовательного типа

|

|

|

|

Қ азақ стан Республикасының білім жә не ғ ылым министірлігі

Тү ркістан облысының білім басқ армасы

«Мирас»Колледжі мекемесі

Отчет

По учебной практике

Дисциплина: «Микропроцессорные технологии. »

Специальность: 1304000 «Вычислительная техника и ПО »

Подготовил: Гусев О, Д,

Группа: ВТ-192. 2

Руководитель: Мусалимова Н. Қ

Шымкент 2022

|

|

|

СОДЕРЖАНИЕ

1 Моделирование цифровых узлов комбинационного и последовательного типа

2 Цифровые устройства комбинационного типа

3 Сумматоры и их виды

4 Арифметико-логические устройства

5 Шифраторы Дешифраторы

6 Преобразователи кодов

7 Интегральные триггеры

8 Коммутаторы цифровых сигналов

9 Устройства сравнения кодов. Цифровые компараторы

10 Преобразователи кодов. Индикаторы

11 Синтаксис языка ассемблер

12 Структура программы на языке ассемблера

13 Арифметические команды

14 Команды передачи

15 Функции языка ассемблер

16 Переходы и логические команды

17 Манипуляция над битами

18 Организация циклов

19 троковые операции. Другие команды

20 Макроопределения

21 Массивы.

22 Подпрограммы-процедуры.

23 Команды сдвига. Упаковка данных.

24 Структуры.

25 Основные операторы и директивы ассемблера

26 Совместимость с языками высокого уровня

27 Оптимизация алгоритма смешивания изображений с помощью технологии ММХ

28 Пакет MASM. Структура программы

29 Объектные модули и библиотеки

30 Совместное использование языка ассемблера и Си, Ассемблер +Паскаль

31 Команды передачи управления. Способы адресации на ассемблере

32 Команды управления циклами

|

|

|

33 Команды работы со строками

34 Вывод на экран в текстовом режиме

35 Способы и методы вывода чисел

36 Команды обслуживающие работу с клавиатурой

37 Программирование ветвлений

38 Команды условного и безусловного перехода.

39 Реализация оператора switch

40 Реализация через последовательность команд «Сравнение – Ветвление».

41 Реализация через таблицу адресов переходов

42 Реализация через две таблица: адресов переходов и значений.

43 Программирование циклов. Циклы с предусловием.

44 Циклы с постусловием. Циклы с параметром. Вложенные циклы.

45 Организация подпрограмм

46 Передача параметров через регистры, статическую память, стек, область за командой вызова.

47 Команды организации подпрограмм. Возврат значений. Рекурсивные подпрограммы и сопрограммы.

48 Обработка массивов и адресная арифметика

49 Представление массивов в статической памяти, динамической памяти и в стеке. Обработка одномерных массивов.

50 Обработка многомерных массивов. Массивы Айлиффа.

51 Адресная арифметика

52 Обработка записей и списков. Представление записей.

53 Обращение к полям. Организация и обработка списков

54 Обработка текстов. Представление текстов в памяти

55 Базовые манипуляции с текстами: перекодировка, вставка, удаление, замена.

56 Логическая обработка данных

57 Обработка бит-векторов. Реализация булевых функций

58 Автоматное программирование и интерпретация цифровых автоматов

59 Арифметическая обработка данных

60 Обработка данных повышенной точности.

61 Обработка двоично-десятичных данных. Обработка вещественных чисел

62 Концепция модульного программирования..

63 Возможные подходы в реализации многомодульных программ

64 Процедуры. Вызов, возврат и их типы - внутри- и межсегментные.

|

|

|

65 Передача параметров процедуре через стек

66 Многомодульные программы на основе подпрограмм, оформленных в виде модулей, допускающих независимое ассемблирование.

67 Внешние и внутренние имена. Директивы EXTRN и PUBLIC.

68 Макросы. Микрооператоры подстановки. Локальные метки макроса.

69 Сравнительная оценка использования макросов и процедур.

70 Интерфейс между ассемблером и языком С++

71 Внешние программы (модули) на ассемблере. Соглашения о взаимодействии ассемблера и С++.

72 Вызов ассемблерных функций из С++. Передача аргументов из С++ в язык ассемблер

73. Литература

Тема 1. Моделирование цифровых узлов комбинационного и последовательного типа

Целью практики по основам микропроцессорной техники является получение практических навыков по моделированию цифровых устройств комбинационного и последовательного типов, изучение и программирование на языке ассемблер с использованием MASM.

Микропроцессорная техника сейчас все более широко входит в нашу жизнь, постепенно замещая и вытесняя традиционную цифровую технику на «жесткой логике». Универсальность, гибкость, простота проектирования аппаратуры, практически неограниченные возможности по усложнению алгоритмов обработки информации -- все это обеспечивает микропроцессорной технике большое будущее. На долю традиционной цифровой техники остаются только узлы и устройства, требующие максимального быстродействия, а также устройства с простейшими алгоритмами обработки информации. Обычная цифровая техника также применяется в настоящее время для увеличения возможностей микропроцессорных систем, для их сопряжения с внешними устройствами, для увеличения их возможностей, то есть играет по сути вспомогательную роль. Таким образом, традиционную цифровую технику ждет, по-видимому, в самом недалеком будущем участь аналоговой техники, область применения которой в свое время сильно сузилась с появлением цифровой техники.

|

|

|

На время прохождения учебной практики ставились следующие задачи:

Повторение основных узлов и устройств, входящих в элементную базу микропроцессорной техники.

Строить функциональные схемы узлов.

Определять классификацию и функциональные возможности триггеров, регистров, счетчиков.

Получить представление о принципах программирования на машинном уровне на примере языка ассемблер.

ЦИФРОВЫЕ УЗЛЫ КОМБИНАЦИОННОГО И ПОСЛЕДОВАТЕЛЬНОГО ТИПА

МОДЕЛИРОВАНИЕ ЦИФРОВЫХ УЗЛОВ КОМБИНАЦИОННОГО И ПОСЛЕДОВАТЕЛЬНОГО ТИПА

Для построения цифровых систем, кроме комбинационных узлов, требуются последовательные узлы, логическое состояние которых определяется последовательностью поступления входных сигналов. Последовательная схема представляет собой автомат для выполнения логических операций, обладающий способностью запоминания отдельных состояний переменных. В отличие от схем комбинационного типа выходные переменные зависят не только от входных переменных, но и от текущего состояния устройства. Таким образом, для построения цифровых систем требуются элементы памяти, осуществляющие хранение двоичной информации в течение требуемого времени. В качестве элемента памяти в цифровых микросхемах используется бистабильная ячейка (БЯ), представляющая собой два инвертирующих логических элемента (чаще всего ИЛИ-НЕ или И-НЕ), соединенных перекрестными связями.

На основе элементов памяти строятся триггеры -- электроны схемы, имеющие два устойчивых состояния, которые устанавливаются при подаче соответствующей комбинации на управляющие входы триггера и сохраняются в течение заданного времени после окончания действия этих сигналов. В зависимости от комбинаций сигналов, управляющих переключением, триггеры делятся на ряд типов: RS, JK, Т, D.

В цифровых устройствах используется большое число различных триггеров, которые классифицируются по ряду признаков: способу записи информации, логической структуре, типу функционирования, элементной базе

Система схемотехнического моделирования Electronics Workbench предназначена для моделирования и анализа электрических схем. Electronics Workbench может проводить анализ схем на постоянном и переменном токах. При анализе на постоянном токе определяется рабочая точка схемы в установившемся режиме работы. Результаты этого анализа не отражаются на приборах, они используются для дальнейшего анализа схемы. Анализ на переменном токе использует результаты анализа на постоянном токе для получения линеаризованных моделей нелинейных компонентов. Анализ схем в режиме АС может проводиться как во временной, так и в частотной областях.

|

|

|

В Electronics Workbench можно исследовать переходные процессы при

воздействии на схемы входных сигналов различной формы. Программа также позволяет производить анализ цифро-аналоговых и цифровых схем большой степени сложности. Имеющиеся в программе библиотеки включают в себя большой набор широко распространенных электронных компонентов. Есть возможность подключения и создания новых библиотек компонентов. Широкий набор приборов позволяет производить измерения различных величин, задавать входные воздействия, строить графики. Все приборы изображаются в виде, максимально приближенном к реальному, поэтому работать с ними просто и удобно[1].

Результаты моделирования можно вывести на принтер или импортировать в текстовый или графический редактор для их дальнейшей обработки.

Программа Electronics Workbench совместима с программой P-SPICE, т. е. предоставляет возможность экспорта и импорта схем и результатов измерений в различные ее версии.

Electronics Workbench позволяет разместить схему таким образом, чтобы были четко видны все соединения элементов и одновременно вся схема целиком. Программа использует стандартный интерфейс Windows, что значительно облегчает ее использование.

Для установки программы необходимы:

IBM-совместимый компьютер с модификацией процессора не ниже 486;

не менее 4 МВ свободного пространства на жестком диске;

операционная система Microsoft Windows 3. 1 или более поздние версии;

манипулятор типа мышь.

В библиотеки компонентов программы входят пассивные элементы, транзисторы, управляемые источники, управляемые ключи, гибридные элементы, индикаторы, логические элементы, триггерные устройства, цифровые и аналоговые элементы, специальные комбинационные и последовательные схемы. Активные элементы могут быть представлены моделями как идеальных, так и реальных элементов. Возможно также создание своих моделей элементов и добавление их в библиотеки элементов. В программе используется большой набор приборов для проведения измерений: амперметр, вольтметр, осциллограф, мультиметр, Боде-плоттер (графопостроитель частотных характеристик схем), функциональный генератор, генератор слов, логический анализатор и логический преобразователь. Electronics Workbench позволяет строить схемы различной степени сложности при помощи следующих операций:

выбор элементов и приборов из библиотек;

перемещение элементов и схем в любое место рабочего поля;

поворот элементов и групп элементов на углы, кратные 90;

копирование, вставка или удаление элементов, групп элементов, фрагментов схем и целых схем;

изменение цвета проводников;

выделение цветом контуров схем для более удобного восприятия;

одновременное подключение нескольких измерительных приборов и наблюдение их показаний на экране монитора;

присваивание элементу условного обозначения;

изменение параметров элементов в широком диапазоне.

Все операции производятся при помощи мыши и клавиатуры. Управление только с клавиатуры невозможно.

Путем настройки приборов можно:

изменять школы приборов в зависимости от диапазона измерений;

задавать режим работы прибора;

задавать вид входных воздействий на схему (постоянные и гармонические токи и напряжения, треугольные и прямоугольные импульсы).

Графические возможности программы позволяют:

одновременно наблюдать несколько кривых на графике;

отображать кривые на графиках различными цветами;

измерять координаты точек на графике;

импортировать данные в графический редактор, что позволяет произвести необходимые преобразования рисунка и вывод его на принтер.

Electronics Workbench позволяет использовать результаты, полученные в программах P-SPICE, PCB, а также передавать результаты на Electronics Workbench в эти программы. Можно вставить схему или ее фрагмент в текстовый редактор и напечатать в нем пояснения или замечания по работе схемы.

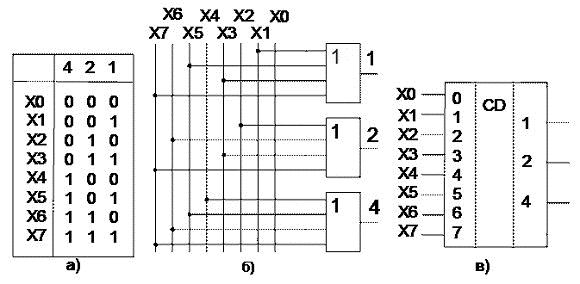

Дешифратор - устройство, в котором при каждой комбинации входных сигналов, единичный сигнал формируется только на одном определенном выходе.

Присвоив номер соответствующему выходу ДШ, можно классифицировать его как преобразователь двоичного кода в десятичный. Очевидно, для преобразования всех возможных комбинаций n-разрядных входных двоичных чисел потребуется 2n-выходов ДШ. Каждый ДШ имеет 4 информационных входа и 16 выходов.

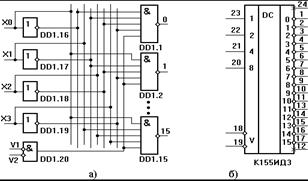

На информационные входы ДШ поступают разряды двоичного кода с весами 8, 4, 2, 1, т. е. с десятичными эквивалентами 23, 22, 21, 20. Если на вход поступает двоичный код 1001, то с учетом десятичных эквивалентов получим: 1001 =. Только на выходе №9 будет 1, а на всех остальных будет 0. В настоящее время ДШ используются как преобразователи двоичного кода в десятичный, используются при организации запоминающих устройств. Функциональная схема дешифратора на 16 выходов приведена на рисунке 1. 1. 1 а. По такой функциональной схеме построена микросхема К155ИД3. Условное обозначение этой микросхемы изображено на рисунке 1. 1. 1 б.

Рисунок 1. 1. 1 Функциональная схема дешифратора на 16 выходов

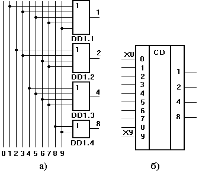

Шифратор используется для преобразования десятичного кода в двоичный. Функциональная схема шифратора, преобразующего десятичные цифры в 4-разрядное двоичное число, приведена на рисунке 2 а, а его условное обозначение - на рисунке 2 б.

Рисунок 1. 1. 2 Функциональная схема шифратора преобразующего десятичные цифры в 4-разрядное двоичное число

При появлении сигнала логической единицы на одном из десяти входов на четырех выходах шифратора будет присутствовать соответствующее двоичное число. Пусть сигнал логической единицы подан на вход 7. Тогда на выходах логических элементов DD1. 1, DD1. 2, DD1. 3 будут сигналы логических единиц, а на выходе элемента DD1. 4 - сигнал логического нуля. Таким образом, на выходах 8, 4, 2, 1 шифратора мы получим двоичное число 0111[2].

Можно конструировать кодовые преобразователи имеющие n-входов, связанных между собой соотношением n = 2k. Следует помнить, что в шифраторе не используется нулевой вход, т. к. при подаче на нулевой уровень на выходе будут нули. Серийно выпускаются и приоритетные шифраторы, которые при одновременном воздействии на входы нескольких сигналов, в первую очередь обслуживают тех, чей приоритет выше (очередь устанавливается заранее)

Цифровые устройства комбинационного типа

Цифровыми устройствами комбинационного типа или цифровыми автоматами без памяти называются цифровые устройства, логические значения на выходе которых однозначно определяются совокупностью или комбинацией сигналов на входах в данный момент времени. К ним относятся суммирующие схемы, шифраторы и дешифраторы, мультиплексоры и демультиплексоры, цифровые компараторы и другие устройства. Цифровые устройства комбинационного типа выпускаются в виде интегральных микросхем или входят в состав больших интегральных микросхем, таких как процессоры, запоминающие и другие устройства.

4. 1 Двоичные сумматоры

4. 1. 1 Одноразрядные сумматоры

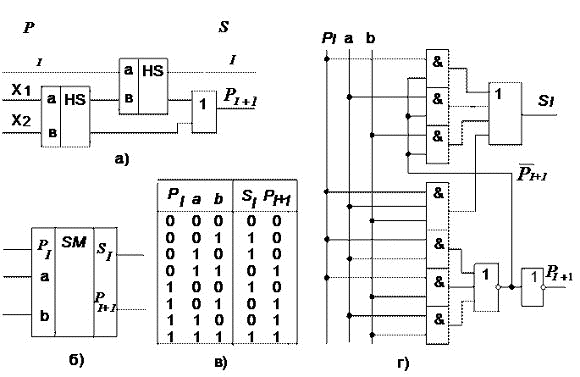

В цифровой вычислительной технике используются одноразрядные суммирующие схемы с двумя и тремя входами, причём первые называются полусумматорами, а вторые — полными одноразрядными сумматорами. Полусумматоры могут использоваться только для суммирования младших разрядов чисел. Полные одноразрядные сумматоры имеют дополнительный третий вход, на который подаётся перенос из предыдущего разряда при суммировании многоразрядных чисел.

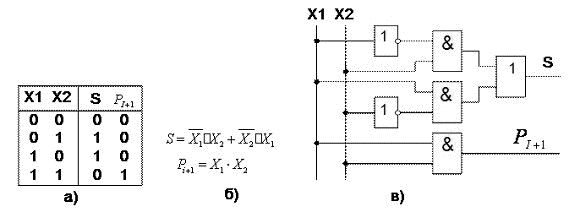

На рисунке 21, а) приведена таблица истинности полусумматора, на основании которой составлена его структурная формула в виде СДНФ (Рисунок 21, б). Функциональная схема, составленная на элементах основного базиса в соответствии с этой структурной формулой, приведена на рисунке 21, в).

Рисунок 21 Одноразрядный полусумматор: а) таблица истинности, б) структурная формула, в) функциональная схема.

Основными параметрами, характеризующими качественные показатели логических схем, являются быстродействие и количество элементов, определяющее сложность схемы.

Быстродействие определяется суммарным временем задержки сигнала при прохождении элементов схемы. В приведённой выше схеме быстродействие определяется задержкой в трёх логических элементах.

Кроме количества элементов сложность схемы, как было отмечено выше, определяется количеством входов элементов, по которым выполняются логические операции. Этот параметр называется «Число по Квайну». Приведённая выше схема содержит 6 элементов и имеет 10 входов (Число по Квайну равно 10).

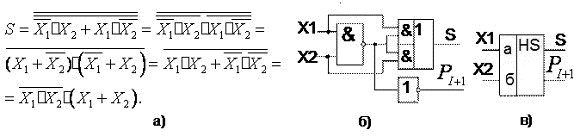

Недостатком схемы рисунок 21, в) является то, что на её входы необходимо подавать и прямые и инверсные значения операндов. Применяя законы алгебры логики схему можно преобразовать, исключив инверсии над отдельными операндами. Порядок минимизации показан на рисунке 22, а), функциональная схема — на рисунке 22, б), а её УГО — на рисунке 22, в).

Рисунок 22 Пример минимизации а), функциональная схема б) и УГО одноразрядного полусумматора в).

Минимизированная схема является более быстродействующей, так как вместо 6 содержит 3 элемента, а число по Квайну уменьшилось с 10 до 7. Учитывая огромное количество используемых суммирующих схем, выигрыш можно считать весьма ощутимым.

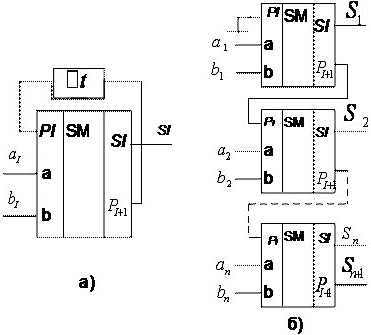

Схему полного одноразрядного сумматора можно получить на основе двух схем полусумматоров и схемы «ИЛИ», как показано на рисунке 23, а).

Рисунок 23 Одноразрядный полный сумматор: а) — функциональная схема на двух полусумматорах; б) — УГО; в) — таблица истинности: г) — минимизированная схема.

Из рассмотрения принципа работы функциональной схемы рисунок 23, а) составлена её таблица истинности, анализ которой показывает, что данная схема выполняет функции полного одноразрядного сумматора. Однако схема не является оптимальной по быстродействию, поскольку в ней сигнал проходит последовательно через две схемы полусумматоров и схему ИЛИ.

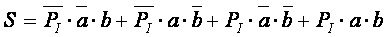

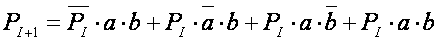

Представляется целесообразным разработка сумматора как устройства, имеющего три входа и два выхода. СДНФ такой функции записывается в виде:

Минимизированные значения, используемые в интегральной схемотехнике:

PI+1 = PIa + PIb + ab

Первое из уравнений минимизируется аналитическим методом, используя законы алгебры логики, а второе — методом минимизирующих карт Карно.

Функциональная схема, составленная по этим уравнениям, приведена на рисунке 23, г). По сравнению со схемой рисунок 23, а) эта схема является более быстродействующей. Условное графическое обозначение (УГО) схемы полного одноразрядного сумматора приведено на рисунке 23, б).

4. 1. 2 Многоразрядные сумматоры

Методы построения многоразрядных сумматоров:

- Последовательное суммирование;

- Параллельное суммирование с последовательным переносом;

- Параллельное суммирование с параллельным переносом.

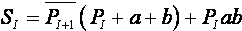

Рисунок 24 Суммирование многоразрядных чисел: а) — Последовательное; б) — Параллельное с последовательным переносом

При последовательном суммировании используется один сумматор, общий для всех разрядов (Рисунок 24, а). Операнды должны вводиться в сумматор через входы аI и bI синхронно, начиная с младших разрядов. Цепь задержки обеспечивает хранение импульса переноса PI+1 на время одного такта, то есть до прихода пары слагаемых следующего разряда, с которыми он будет просуммирован. Задержку выполняет D-триггер. Результаты суммирования также считываются последовательно, начиная с младших разрядов. Для хранения и ввода операндов на входы сумматора, а также для записи результата суммирования обычно используются регистры сдвига.

Достоинство этого метода — малые аппаратные затраты.

Недостаток — невысокое быстродействие, так как одновременно суммируются только пара слагаемых.

Схема параллельного сумматора с последовательным переносом приведена на рисунке 24, б). Количество сумматоров равно числу разрядов чисел. Выход переноса PI+1 каждого сумматора соединяется со входом переноса PI следующего более старшего разряда. На входе переноса младшего разряда устанавливается потенциал «0», так как сигнал переноса сюда не поступает. Слагаемые aI и bI суммируются во всех разрядах одновременно, а перенос PI поступает с окончанием операции сложения в предыдущем разряде.

Быстродействие таких сумматоров ограничено задержкой переноса, так как формирование переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса не распространится по всей цепочке сумматоров.

Параллельные сумматоры с параллельным переносом

Для организации параллельного переноса применяются специальные узлы — блоки ускоренного переноса.

Принцип ускоренного переноса заключается в том, что для каждого двоичного разряда дополнительно находятся два сигнала:

G — образование переноса и H — распространение переноса.

GI = aI·bI

HI = aI + bI

В случае GI=1, то есть aI=bI=1, в данном i-разряде формируется сигнал переноса PI+1 в следующий высший разряд независимо от формирования функций суммы в предыдущих разрядах.

Если хотя бы одно из слагаемых aI или bI равно «1», то есть HI=1, то перенос в последующий разряд производится при наличии сигнала переноса из предыдущего разряда.

Если HI=HI–1=1 и при этом существует сигнал переноса PI из предыдущего в i-й разряд, то перенос производится сразу в i+2 разряд.

В общем случае процесс формирования ускоренного переноса описывается следующим уравнением:

PI+1 = GI + HI·GI–1 + HI·HI–1·GI–2 + … + HI·HI–1·…·H2·H1·P1

Блоки ускоренного переноса выпускаются в интегральном исполнении в виде отдельных микросхем или непосредственно со схемой сумматора или арифметико-логического устройства в одной микросхеме.

4. 1. 3 Арифметико-логические устройства

Основными арифметическими операциями являются сложение и вычитание. Разработаны коды дополнительный и обратный, которые позволяют выполнять операцию вычитания методом суммирования. Для выполнения операции вычитания, при использовании дополнительного кода, вычитаемое следует перевести в дополнительный код и просуммировать с первым слагаемым. Полученный результат (разность) будет представлен в дополнительном коде. Затем его следует перевести в прямой код.

Прямой и дополнительный код положительных чисел совпадают. При преобразовании отрицательного числа в дополнительный код все разряды прямого кода следует проинвертировать и к младшему разряду добавить единицу. При обратном преобразовании дополнительного кода в прямой результат следует также проинвертировать и к младшему разряду добавить единицу.

Таким образом, выполнение операции вычитания методом суммирования требует дополнительных затрат времени и снижает быстродействие вычислительных средств.

Для повышения быстродействия ЭВМ разработаны и используются комбинированные арифметико-логические устройства, которые обеспечивают выполнение ряда арифметических и логических операций над прямыми кодами чисел без их преобразования.

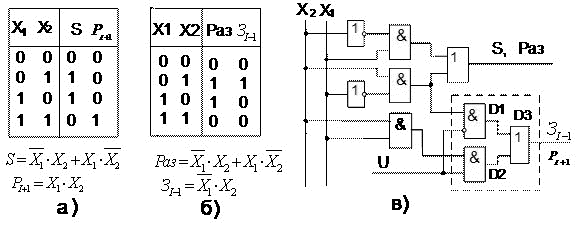

Методика построения одноразрядного арифметического устройства для выполнения операций суммирования и вычитания показана на рисунке 25. Из сравнения логических выражений операций суммирования (Рисунок 25, а) и вычитания (Рисунок 25, б) следует, что выражения для суммы и разности совпадают, а выражение для заёма является частью операции суммирования или вычитания.

Рисунок 25 Таблицы истинности и структурные формулы операции суммирования а), вычитания б) и схема одноразрядного АЛУ в).

Таким образом, для выполнения операции вычитания не требуется получение дополнительных сигналов, поэтому и не требуются дополнительные аппаратные затраты. Необходимо лишь обеспечить коммутацию сигналов переноса и заёма в соответствии с кодом операции.

На рисунке 25, в) приведена схема простейшего АЛУ, на которой роль устройства управления выполняют два клапана, управляемые разнополярными сигналами от управляющего напряжения U. Эта часть схемы на рисунке 25, в выделена пунктирной линией. При U=0 выполняется операция вычитания, а при U=1 — операция суммирования.

Многоразрядные АЛУ выпускаются в виде интегральных микросхем или входят в состав процессоров, являясь их основой.

МС 564ИП3 (Рисунок 26, а) — это 4-разрядное параллельное АЛУ, выполняющая 16 арифметических и 16 логических операций.

Рисунок 26 Схема 4-разрядного АЛУ 564ИП3 а) и схема ускоренного переноса 564ИП4 б).

A(а0–а3) — первый операнд,

B(b0–b3) — второй операнд,

S(s0–s3) — код операции — 4 разряда.

Если M=0, то выполняются арифметические операции: 24=16, при M=1 выполняются логические операции: 24=16. Итого 16+16=32 операции.

F(f0–f3) — результат операции. На выходе A=B появляется «1», если при выполнении операции вычитания результат операции будет равен «0», то есть A=B. Поскольку АЛУ параллельного типа, то имеются выходы генерации G и распространения переноса H. Pn и Рn+4 — входной и выходной переносы.

Для увеличения разрядности обрабатываемых слов МС АЛУ можно соединять последовательно, как и в параллельных сумматорах с последовательным переносом. При этом, конечно, увеличивается время выполнения операций.

Уменьшить это время и, следовательно, увеличить быстродействие АЛУ можно применением схемы ускоренного переноса 564ИП4, рисунок 26, б). Используя четыре МС АЛУ и одну МС ускоренного переноса можно получить 16-разрядное полностью параллельное АЛУ, время суммирования которого равно времени суммирования одной микросхемы.

4. 2 Кодирующие и декодирующие устройства

4. 2. 1 Шифраторы

Шифратор (кодер) — это функциональный узел, предназначенный для преобразования поступающих на его входы управляющих сигналов (команд) в n-разрядный двоичный код. В частности, такими сигналами или командами могут быть десятичные числа, например, номер команды, который с помощью шифратора преобразуется в двоичный код.

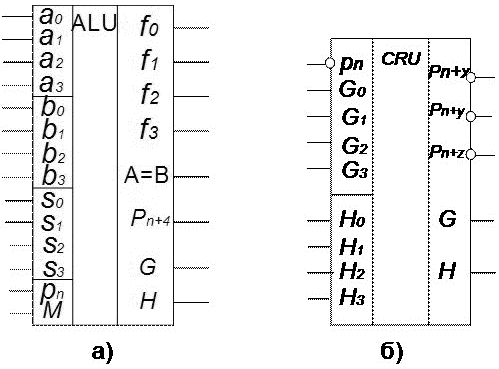

В качестве примера разработаем схему 3-разрядного шифратора. Вначале следует построить таблицу кодов (таблицу истинности), в которой код номера сигнала представим, например, двоичным кодом (Рисунок 27, а). Схема, реализованная на элементах ИЛИ, приведена на рисунке 27, б.

Рисунок 27 Таблица кодов 3-разрядного шифратора а), его функциональная схема б) и УГО в).

В общем случае, при использовании двоичного кода, можно закодировать 2n входных сигналов. В рассмотренной выше схеме выходной код «000» будет присутствовать на выходе при подаче сигнала на вход X0 и в случае, если входной сигнал вообще не подаётся ни на один из входов. Для однозначной идентификации сигнала X0 в интегральных схемах формируется ещё один выходной сигнал — признак подачи входного сигнала, который используется и для других целей.

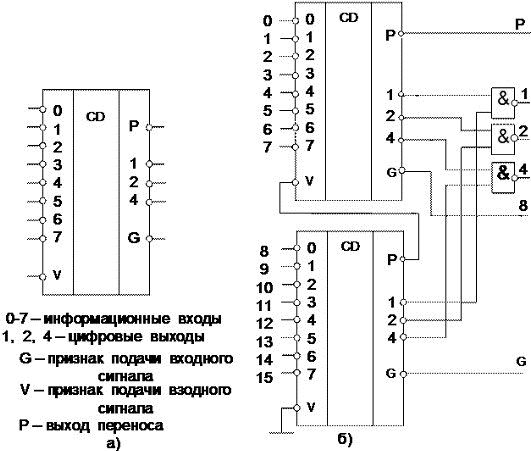

На рисунке 28 приведено УГО схемы 3-х разрядного приоритетного шифратора на 8 входов.

Рисунок 28 3-разрядный приоритетный шифратор К555ИВ1 а) и соединение двух МС б)

При подаче сигнала на любой из входов, устанавливается G=1, P=0, а на цифровых выходах — двоичный код номера входа, на который подан входной сигнал. Если сигнал подан одновременно на два или несколько входов, то на выходе установится код входа с большим номером. Отсюда название шифратора «приоритетный».

Если сигнал (лог. «0») подан на один из входов 0…7, то на выходах DD3 появятся младшие разряды прямого кода, на выходе G DD1 — лог. «0», определяющий разряд с весовым коэффициентом 8 выходного кода, на выходе P — лог. «1».

Если лог. «0» подан на один из входов 8…15, то сигнал лог. «1» с выхода P DD2 запретит работу DD1. При этом младшие разряды на выходах DD3 определяются уже микросхемой DD2, а на выходе 8 выходного кода будет лог. «1».

Таким образом, с выходов 1, 2, 4, 8 можно снять прямой код, соответствующий номеру входа, на который подан входной сигнал.

|

|

|