|

Алгоритм работы UART и SPI

|

|

|

|

СТРУКТУРНА СХЕМА

Структурна схема мікропроцесорої системи обробки даних на базі

мікроконтроллеру ATMEGA8515 зображена на рисунку 2.1

Рисунок 2.1 - Структурная схема микропроцессорной системы обработки

данных на базе микроконтроллеру К1816ВЕ51

NS-нормирователь уровней;

Sensor-датчик

GI_in-гальваническая развязка входных цифровых сигналов;

GI_out-гальваническая развязка выходных цифровых сигналов;

CPU-центральный процессор;

CPU-центральный процессор;

RAM-Оперативное запоминающему устройство;

LCD-жидко кристаллический индикатор;

SD-системный дешифратор;

SPI - согласование между устройствами

KEY - Матричная клавиатура

Порты микроконтроллера используются для вывода адреса и данных в различных функциональных блоков. Взаимодействие микроконтроллера с внешней памятью и периферийными устройствами осуществляется по шине  адреса. Данные передаются и принимаются микроконтроллером по шине данных. Управляющие сигналы передаются по шине управления.

адреса. Данные передаются и принимаются микроконтроллером по шине данных. Управляющие сигналы передаются по шине управления.

Адрес формируется на контактах портов РА 0 - 7 младших разрядов. Обмен данными осуществляет микроконтроллер через порт РА. Поэтому младшие разряды адреса на время обмена хранятся в регистре-защелке.

Для взаимодействия микроконтролера с клавиатурой и индикацией существует отдельный контроллер клавиатуры и индикации.

Разработка принципиальной схемы МК

Данная схема представлена в приложении 3

4.1. Выбор элементной базы

Выбор МК

По заданому варианту микроконтроллер имеет серию 8515-8JC, последние буквы означают корпус PDIP.

Описание:

ATmega8515 - экономичные 8-разрядный микроконтроллер, основанный на усиленной AVR RISC архитектуре. ATmega8515 обеспечивает производительность 1 млн. оп. в сек на 1 МГц синхронизации за счет выполнения большинства инструкций за один машинный цикл и позволяет оптимизировать потребление энергии за счет изменения частоты синхронизации.

AVR ядро объединяет богатый набор инструкций с 32 рабочими регистрами общего на-значения. Все 32 регистра непосредственно подключены к АЛУ (арифметико-логическое уст-ройство), что позволяет указывать два регистра в одной инструкции и выполнить ее за один цикл. Данная архитектура обладает большей эффективностью кода и в 10 раз большей произво-дительностью по сравнения с CISC микроконтроллерами.

ATmega8515 обладает следующими возможностями: 8 кбайт внутрисхемного программы-руемой флэш-памяти с возможностью чтения во время записи, 512 байт ЭППЗУ, 512 байт ста-тического ОЗУ, внешний интерфейс памяти, 35 линий ввода-вывода, 32 рабочих регистров об-щего назначения, два универсальных таймера-счетчика с режимами компаратора, внутренние и внешние запросы на прерывание, последовательный программируемые УСАПП, программы-руемый сторожевой таймер с внутренним генератором, последовательный порт SPI и три про-граммно настраиваемых режима управления энергопотребления. Режим холостого хода (Idle) останавливает ЦПУ, но оставляет в работе статическое ОЗУ, таймеры-счетчики, порт SPI и сис-тему прерываний. Режим пониженному потребления (Power-down) сохраняет содержимое реги-

|

|

|

стров, но останавливает генератор, выключает все Встроенные функции в появления следую-щего запроса на прерывание или аппаратного сброса. В дежурно режиме (Standby) генератор на кварцевом резонаторе запущен, а Остальная часть отключена. Данный режим позволяет реа-лизовать быстрый запуск в комбинации с малым потреблением.

|

Расположение выводов микроконтроллера ATmega851

1.4.2. РАЗРАБОТКА БЛОКА ПАМЯТИ (ОЗУ и ПЗУ)

Исходный данные:

Количество ячеек внешнего ОЗУ NОЗУ - 2К × 8

Входные токи:

при логическому 0, IIL - 1,6 мА

при логической 1, IIH - 0,1 мА

Входная емкость логических схем погрузки, СI - 5 пФ

Монтажные емкости всех цепей (См = 20 пФ).

Согласно задания количество ячеек ОЗУ составляет NОЗУ.

Разрядность ОЗУ nОЗУ должна соответствовать разрядности обработки данных ЦБ.

Информационная емкость СОЗУ определяется по формуле

Исходный данные:

Количество ячеек внешнего ОЗУ NОЗУ - 2К × 8

Входные токи:

при логическому 0, IIL - 1,6 мА

при логической 1, IIH - 0,1 мА

Входная емкость логических схем погрузки, СI - 5 пФ

Монтажные емкости всех цепей (См = 20 пФ).

Согласно задания количество ячеек ОЗУ составляет NОЗУ.

Разрядность ОЗУ nОЗУ должна соответствовать разрядности обработки данных ЦБ.

Информационная емкость СОЗУ определяется по формуле:

|

|

|

ВкачествемикросхемыОЗУвыберемК537РУ10.

Микросхему ОЗУ выберем К537РУ10, потому что она идеально подходит и не создает убыточности для данного случая. Для этой микросхемы памяти емкость2К,аразрядностьслова8бит:

.

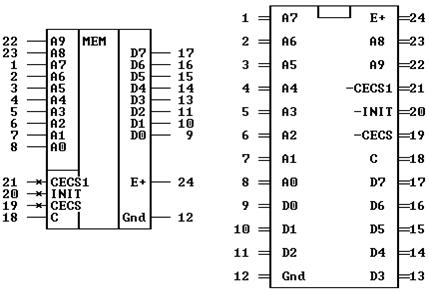

Рис.6 Условно графическое обозначение ОЗУ К537РУ10

Наименование выводов:

A0 ÷ A10 - адресные входы.

W / R - запись / считывание.

CS1 - chip select, чип выбора.

CEO - выход разрешения.

D0 ÷ D7 - шина данных ввода / вывода.

| CS | OE | WR | A0..10 | D0..7 | Режим |

| M | X | X | Адрес | Дані | Зберігання |

| L | X | L | Запись | ||

| L | L | H | Зчитування | ||

| L | H | H | Заборона виходу |

ОЗУ представляет собой статический асинхронный оперативно запоминающее устройство.

Режимы работы ОЗУ:

CS OE WR A0..10 D0..7 Режим

M X X Адрес Данные Хранение

L X L Запись

L L H Считывание

L H H Запрет выхода

Технологические и электрические характеристики К537РУ10:

|

Технология – КМОП

Технология – КМОП

Организация - 2К × 8

Время выборки, ns - не более 220

Напряжение питания, V - 5

Ток, мА

в режиме обращения - 30

в режиме хранения - 1-2

Входное напряжение, V

при логическом 0 - min 0 - max 0,4

при логической 1 - min 0,9 Ucc - max 0,5

Выходное напряжение, V

при логическом 0 - min 0 - max 0,4

при логической 1 - min 2,4 - max 0,4

Выход - 3 с.

Диапазон рабочих температур, º С - 10 - +70

Исходные данные для микросхемы КР556РТ20 1К 8:

Количество ячеек внешнего ПЗУ NОЗУ - 1К × 8

Входные токи:

при логическому 0, IIL - 0,25 мА

при логической 1, IIH - 0,04 мА

Входная емкость логических схем погрузки, СI - 5 пФ

Монтажные емкости всех цепная (См = 20 пФ).

Согласно задания количество ячеек ПЗУ составляет NОЗУ.

Разрядность ПЗУ nОЗУ должна соответствовать разрядности обработки данных ЦБ.

Информационная емкость СОЗУ определяется по формуле:

|

|

|

В качестве микросхемы ПЗУ выберем КР556РТ20, потому что она идеально подходит и не создает убыточности для данного случая. Для данной микросхемы памяти емкость 1К, а разрядность слова 8 бит:

где IIАL, IIAH - входные токи логического 0 и логической 1 по цепям адрес выбранной БИС ПЗУ. CIА - входная емкость по входу адрес БИС ПЗУ.

Рис.7 Условно графическое обозначение ПЗУ КР556РТ20

Наименование выводов:

A0 ÷ A9 - адресные входы.

D0 ÷ D7 - шина данных ввода / вывода.

CECS, CECS1 - выбор микросхемы

Технологические и электрические характеристики КР556РТ20:

Технология - ТТЛШ

Организация - 1К × 8

Время выборки, ns - не более 65

Напряжение питания, V - 5

Ток, мА - 180 мА

Входное напряжение, V

при логическом 0 - min 2,4 - max 0,5

при логической 1 - min 2,4 - max 0,5

Выходное напряжение, V

при логическом 0 - min 2,4 - max 0,5

при логической 1 - min 2,4 - max 0,5

Выход - 3 с.

Потребляемая мощность, mW - 875

Диапазон рабочих температур, º С - 10 - +70

Исходные данные для микросхемы КР556РТ18 2К 8:

Количество ячеек внешнего ПЗУ NОЗУ - 4К × 8

Входные токи:

при логическому 0, IIL - 0,25 мА

при логической 1, IIH - 0,04 мА

Входная емкость логических схем погрузки, СI - 5 пФ

Монтажные емкости всех цепей (См = 20 пФ).

|

4.1.3. Выбор жидко-кристаллического индикатора.

Жидко-кристаллические (ЖК)-модули являются одними из основных средств вывода информации для современных цифровых систем. Представляют собой недорогое и удобное решение, позволяющее сэкономить время и ресурсы при разработке новых изделий. Обеспечивают отображение большого объема информации при хорошей различимости и низком энергопотреблении, благодаря чему широко используются в измерительных приборах, медицинском оборудовании, промышленном оборудовании, информационных системах, аппаратуре с автономным питанием.

|

Алфавитно-цифровой ЖК-модуль BC2004A фирмы Bolymin

20 символов, 4 строки

| Назначение выводов | ||

| № вывода | Название | Функция |

| Vss | Общий (GND) | |

| Vdd | Напряжение питания | |

| Vo | Контрастность | |

| RS | Команды/Данные | |

| R/W | Чтение/запись | |

| E | Выбор модуля | |

| DB0 | Линия данных 0 | |

| DB1 | Линия данных 1<> | |

| DB2 | Линия данных 2<> | |

| DB3 | Линия данных 3<> | |

| DB4 | Линия данных 4<> | |

| DB5 | Линия данных 5<> | |

| DB6 | Линия данных 6<> | |

| DB7 | Линия данных 7<> | |

| A | Напряжение питания подсветки (+)<> | |

| K | Напряжение питания подсветки (-)<> |

|

|

|

| Механические характеристики | ||

Размер модуля Размер модуля

| 98.0 x 60.0 | мм |

| Размер экрана | 77.0 x 25.2 | мм |

| Размер символа | 2.95 x 4.75 | Мм |

| Размер точки | 0.55 x 0.55 | мм |

| Шаг точек | 0.6 x 0.6 | мм |

| Электрические параметры (Vdd=+5V, Ta=25C) | ||||||

| Параметр | Обозначения | Условие теста | Значение | Единицы измерения | Параметр | Обозначения |

| Напряжение питания | Vdd | - | V | Напряжение питания | Vdd | |

| Ток потребления | Idd | Vdd=5V | 1,6 | mA | Ток потребления | Idd |

| Напряжение питания стекла | Vdd-Vo | 25oC | 4,5 | V | Напряжение питания стекла | Vdd-Vo |

| Напряжение питания подсветки | Vf | 25oC | 4,2 | V | Напряжение питания подсветки | Vf |

| Ток потребления подсветки (светодиодная) | If | 25oC | mA | Ток потребления подсветки (светодиодная) | If | |

| Ток потребления подсветки (электролюминисцентная) | If | Vf=110Vac/400Hz | 5.0 | mA | Ток потребления подсветки (электролюминисцентная) | If |

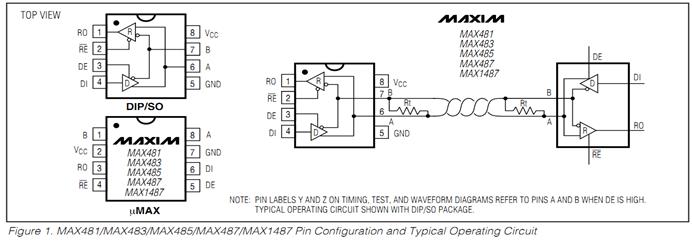

4.1.5. Выбор устройства связи (RS-485).

Интерфейс RS-485 (другое название - EIA/TIA-485) - один из наиболее распространенных стандартов физического уровня связи. Физический уровень - это канал связи и способ передачи сигнала (1 уровень модели взаимосвязи открытых систем OSI). Сеть, построенная на интерфейсе RS-485, представляет собой приемопередатчики, соединенные при помощи витой пары - двух скрученных проводов. В основе интерфейса RS-485 лежит принцип дифференциальной (балансной) передачи данных. Суть его заключается в передаче одного сигнала по двум проводам. Причем по одному проводу (условно A) идет оригинальный сигнал, а по другому (условно B) - его инверсная копия. Другими словами, если на одном проводе "1", то на другом "0" и наоборот. Таким образом, между двумя проводами витой пары всегда есть разность потенциалов: при "1" она положительна, при "0" - отрицательна.

Именно этой разностью потенциалов и передается сигнал. Такой способ передачи обеспечивает высокую устойчивость к синфазной помехе. Синфазной называют помеху,  действующую на оба провода линии одинаково. К примеру, электромагнитная волна, проходя через участок линии связи, наводит в обоих проводах потенциал. Если сигнал передается потенциалом в одном проводе относительно общего, как в RS-232, то наводка на этот провод может исказить сигнал относительно хорошо поглощающего наводки общего ("земли"). Кроме того, на сопротивлении длинного общего провода будет падать разность потенциалов земель - дополнительный источник искажений. А при дифференциальной передаче искажения не происходит. В самом деле, если два провода пролегают близко друг к другу, да еще перевиты, то наводка на оба провода

действующую на оба провода линии одинаково. К примеру, электромагнитная волна, проходя через участок линии связи, наводит в обоих проводах потенциал. Если сигнал передается потенциалом в одном проводе относительно общего, как в RS-232, то наводка на этот провод может исказить сигнал относительно хорошо поглощающего наводки общего ("земли"). Кроме того, на сопротивлении длинного общего провода будет падать разность потенциалов земель - дополнительный источник искажений. А при дифференциальной передаче искажения не происходит. В самом деле, если два провода пролегают близко друг к другу, да еще перевиты, то наводка на оба провода

|

|

|

одинакова. Потенциал в обоих одинаково нагруженных проводах изменяется одинаково, при этом информативная разность потенциалов остается без изменений.

Аппаратная реализация интерфейса - микросхемы приемопередатчиков с дифференциальными входами/выходами (к линии) и цифровыми портами (к портам UART контроллера). Существуют два варианта такого интерфейса: RS-422 и RS-485.

RS-422 - полнодуплексный интерфейс. Прием и передача идут по двум отдельным парам проводов. На каждой паре проводов может быть только по одному передатчику.

RS-422 - полнодуплексный интерфейс. Прием и передача идут по двум отдельным парам проводов. На каждой паре проводов может быть только по одному передатчику.

RS-485 - полудуплексный интерфейс. Прием и передача идут по одной паре проводов с разделением по времени. В сети может быть много передатчиков, так как они могут отключаются в режиме приема.

Остановлюсь поподробнее на приемопередатчике RS-485. Цифровой выход приемника (RO) подключается к порту приемника UART (RX). Цифровой вход передатчика (DI) к порту передатчика UART (TX). Поскольку на дифференциальной стороне приемник и передатчик соединены, то во время приема нужно отключать передатчик, а во время передачи - приемник. Для этого служат управляющие входы - разрешение приемника (RE) и разрешения передатчика (DE). Так как вход RE инверсный, то его можно соединить с DE и переключать приемник и передатчик одним сигналом с любого порта контроллера. При уровне "0" - работа на прием, при "1" - на передачу.

Приемник, получая на дифференциальных входах (AB) разность потенциалов (UAB) переводит их в цифровой сигнал на выходе RO. Чувствительность приемника может быть разной, но гарантированный пороговый диапазон распознавания сигнала производители микросхем приемопередатчиков пишут в документации. Обычно эти пороги составляют ± 200 мВ. То есть, когда UAB > +200 мВ - приемник определяет "1", когда UAB < -200 мВ - приемник определяет "0". Если разность потенциалов в линии настолько мала, что не выходит за пороговые значения - правильное распознавание сигнала не гарантируется. Кроме того, в линии могут быть и не синфазные помехи, которые исказят столь слабый сигнал.

4.1.4. Ра 3.9 Выбор аналого-цифрового преобразователя

4.1.4. Ра 3.9 Выбор аналого-цифрового преобразователя

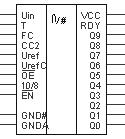

По заданию, в системе должен присутствовать восьмиразрядный аналого-цифровой преобразователь. Есть множество подобных АЦП, на-до выбрать какой-нибудь из них. Выбирать нужно, скорее всего, по бы-стродействию. Микроконтроллер работает при частоте синхрогенератора не больше 12МГц, а значит, что Тактовая частота будет в 12 раз меньше, то есть 1МГц. Поэтому фотоаппарата смысла брать АЦП с большим быстродейст-вием.

Среди функционально законченных АЦП, сопрягаемых с микропро-цессоров, есть микросхема К1108ПВ1. Это восьмиразрядный АЦП по-следовательно приближения со временем преобразования в восьми-разрядный код не более 0.5мкс. Эта микросхема не требует внешнего устройства выборки и хранения. АЦП может работать как десяти-или восьмиразрядный. В микросхеме есть внутренний источник опорного на-пряжения

Рисунок 2.7 - Аналогово-цифровой преобразователь

АЦП может работать с внутренним тактирование, готовность дан-ных  отмечается уровнем логического нуля соответствующей выходе. Вход OE разрешает выдачу цифрового кода на шину данных. Вход T - вход внешнего тактирования, для использования внутреннего тактирова-ния Этот вывод нужно через емкость 25пФ подать на «землю». Инверс-ный вход EN - разрешение преобразования. Для работы в восьмиразряд-ном режиме на вход 10/8 нужно подать напряжение питания. Тогда код будет на младших восьми выходах.

отмечается уровнем логического нуля соответствующей выходе. Вход OE разрешает выдачу цифрового кода на шину данных. Вход T - вход внешнего тактирования, для использования внутреннего тактирова-ния Этот вывод нужно через емкость 25пФ подать на «землю». Инверс-ный вход EN - разрешение преобразования. Для работы в восьмиразряд-ном режиме на вход 10/8 нужно подать напряжение питания. Тогда код будет на младших восьми выходах.

На вход OE будет поступать сигнал от дешифратора адреса, цифровые выходы будут подключены к шине данных. счет RC – цепи интегратора

Сигналы ШИМ представляют собой цифровые сигналы с постоянной частотой. Если коэффициент заполнения ШИМ-сигнала изменяется со временем, то, отфильтровав его, получим на выходе аналоговый сигнал. В общем виде, разрешение ЦАП на базе ШИМ, построенного на таймере и фильтре эквивалентно разрешению ШИМ-сигнала, используемого ЦАП-ом.  Таким образом, разрешение ШИМ-сигнала зависит от длины счётчика и наименьшего возможного изменения коэффициента заполнения в ШИМ-счётчике.

Таким образом, разрешение ШИМ-сигнала зависит от длины счётчика и наименьшего возможного изменения коэффициента заполнения в ШИМ-счётчике.

Частота среза фильтра вычисляется следующим образом:

Подставив частоту из задания рассчитаем RC:

=>

=>  =>

=>

Приняв R за 1кОм получим С=10nF

4.1.5. Выбор устройства связи (UART).

При программировании UART в простейшем случае решаются три задачи: инициализация UART (задание режимов работы), организация приема данных и организация передачи данных.

Примером инициализирующей подпрограммы может быть следующая последовательность команд:

.def tmp =r20 Init_uart: ldi tmp,0b00011101;Инициализация UART out UCR,tmp;TXEN=1,RXEN=1,СРH9=1,TXB8=1 ldi tmp,25;9600 бит/c при fclk=4МГц out UBRR,tmp retЕсли микропроцессор использует последовательный канал для коротких однобайтных сообщений, то передавать и принимать данные можно, просто опрашивая флаги готовности передатчика и приемника UART. При передаче байта в последовательный канал все, что должен сделать процессор - дождаться установки флага готовности передатчика UDRE и записать затем передаваемый символ в регистр данных передатчика:

trans: sbis USR, UDRE;Если бит UDRE в USR установлен, то;пропустить cледующую команду rjmp trans;Вернуться на метку trans out UDR, r15;Вывести в регистр данных передатчика UART;содержимое r15 ret4.1.6. Выбор устройства согласования.

В качестве устройства согласования используется схема выполненная на операционном усилителе с подключением необходимой навески. Основные параметры:

· Конденсаторы используются для фильтрации по питанию.

·  Диоды на случаи пробоя

Диоды на случаи пробоя

· Вводится отрицательная обратная связь

Операционный усилитель работает в режиме повторителя.

Схема представлена на рисунке.

5. Разработка алгоритмов работы.

5. Разработка алгоритмов работы.

Алгоритм работы АЦП.

Инициализация:

ldi temp, 0;Активный канал 0

out ADMUX, temp

ldi temp, 0b10101111

out ADCSR, temp

sbi ADCSR, 6;Запуск преобразован ия

Алгоритм работы UART и SPI

SPI

Инициализация как ведущего (мастера):

SPI_MasterInit:

; Установка MOSI и SCK на вывод, все остальные на ввод

ldi r17,(1<<DD_MOSI)|(1<<DD_SCK)out DDR_SPI,r17

; Разрешение SPI в режиме мастера, установка скорости связи fck/16

ldi r17,(1<<SPE)|(1<<MSTR)|(1<<SPR0)

out SPCR,r17

ret

SPI_MasterTransmit:

; Запуск передачи данных (r16)

out SPDR,r16

Wait_Transmit:

; Ожидание завершения передачи данных

sbis SPSR,SPIF

sbis SPSR,SPIF

rjmp Wait_Transmit

ret

Инициализация как подчинненого:

SPI_SlaveInit:

; Установка MISO на вывод и всех ост. на ввод

ldi r17,(1<<DD_MISO)

out DDR_SPI,r17

; Разрешение SPI

ldi r17,(1<<SPE)

out SPCR,r17

ret

SPI_SlaveReceive:

; Ожидание завершения передачи

sbis SPSR,SPIF

rjmp SPI_SlaveReceive

; Чтение принятых данных и выход из процедуры

in r16,SPDR

ret

UART:

;Инициализация:

st: ldi tmp1_r,LOW(RAMEND);Установка стека out spl,tmp1_r ldi tmp1_r,HIGH(RAMEND) out sph,tmp1_r; ldi tmp1_r,0b00011101;Инициализация UART out UCR,tmp1_r;TXEN=1,RXEN=1,СРH9=1,TXB8=1 ldi tmp1_r,25;9600 бит/c при fclk=4МГц out UBRR,tmp1_r; clr tmp1_r;Настроить порт D на ввод out ddrd,tmp1_r; clr tmp1_r;Инициализация буфера UART_OUT sts UART_OUT_T,tmp1_r;Установить указатель хвоста в ноль sts UART_OUT_H,tmp1_r;Установить указатель головы в ноль sts UART_IN_T,tmp1_r

|

|

|