|

Исследование маршрута проектирования цифровых устройств в САПР Xilinx ISE

|

|

|

|

Цель работы: изучение маршрута проектирования электронных устройств в базисе ПЛИС; знакомство со средствами проектирования САПР ПЛИС Xilinx ISE; временное моделирование полученного устройства. Получение навыков проектирования простых цифровых схем.

1.1Общий маршрут проектирования устройств на ПЛИС в САПР Xilinx ISE

Процесс проектирования устройств на ПЛИС состоит из следующих шагов:

1) Запуск системы и создание нового (открытие существующего) проекта.

а) Запустить Xilinx ISE > Project Navigator.

Главное окно ISE называется ” Project Navigator ”. В этом окне находятся инструментальные панели и консоль сообщений.

Панели, расположенные слева, представляют собой соответственно список файлов текущего проекта – окно «Sources in Project» и список процессов (этапов обработки) проекта – «Processes for Current Source».

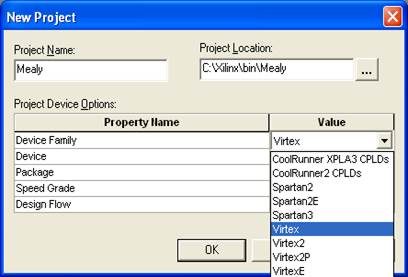

б) Для создания нового проекта необходимо выбрать соответствующий пункт главного меню (File > New Project). В окне открывающегося мастера (Рисунок 1) необходимо задать имя проекта (Project Name) и размещение проекта (Project Location) папки с материалами. Необходимо определить параметры проекта (Project Device Options):

· Выбор типа ПЛИС - п ункт Device Family. Для FPGA выбрать соответствующие типы (Virtex/ Spartan/ ХС4000/ ХС5200/ ХС3000). Для ПЛИС типа CPLD - (CPLD XC9500/ XC9500/ XC9500XL/ CoolRunner/ CoolRunner - II).

Рисунок 1 - Диалоговое окно создания нового проекта

· Задать тип микросхемы (Device), тип корпуса (Package) (в лабораторной работе можно оставить значения по умолчанию).

· Задать маршрут проектирования (Design Flow) (Рисунок 2). Типы XST VHDL и XST Verilog соответствуют описанию на одном из языков описания аппаратуры или графический ввод, типы EDIF и NGC/NGO предусматривают использование результатов работы внешних средств синтеза. При выполнении лабораторной работы использовать тип XST VHDL.

|

|

|

Рисунок 2 - Диалоговое окно выбора ПЛИС и маршрута проектирования

2) Ввод описания проекта.

а) Для ввода проекта можно использовать графический ввод или описание на языке описания аппаратуры. Для этого в окне «Project Navigator» выполнитьProject> New Source, появится окно New, представленное на рисунке 3. Для графического ввода выбрать тип Schematic, для VHDL- описания – VHDL Module.

Рисунок 3

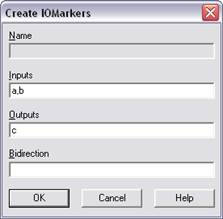

б) Графический ввод схемы. Определить интерфейс (входы/ выходы) объекта. Для графического ввода можно воспользоваться конструктором создания входных и выходных элементов схемы Tools -> Create IOMarkers (рисунок 4), указав через запятую имена входных (Inputs) и выходных (Outputs) портов. Чтобы воспользоваться конструктором, необходимо, чтобы на схеме элементов не было.

Рисунок 4

Схему можно сформировать вручную, перенося элементы с панели компонентов. Подсоединять порты (Add I/O Marker на главной панели) можно только к соединительным линиям. Т.е. первоначально нужно «нарисовать» линию (Add Wire на главной панели).

Используя панель компонентов собрать схему. Готовую схему сохранить.

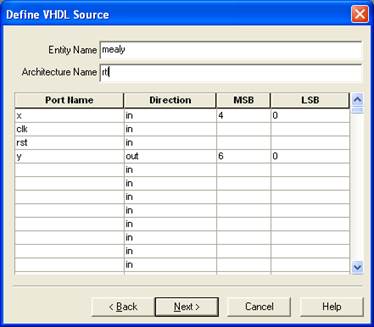

в) Ввод описания на языке VHDL.

Определение интерфейса представлено на рисунке 5. По умолчанию сигналам портов присваивается тип STD_Logic_vector, порядок данных задается позициями MSB, LSB. При необходимости, типы сигналов можно изменить в текстовом редакторе.

Рисунок 5 - Диалоговое окно настройки выводов компонента

После завершения работы мастера будет создан шаблон VHDL- файла, который можно редактировать в окне текстового редактора «Project Navigator». По завершении редактирования файл необходимо сохранить.

3) Трансляция компонента во внутреннее схемное представление.

Выбрать компонент в списке файлов проекта. После выбора, в окне доступных процессов появится список операций (процессов), которые можно выполнять для выбранного файла.

|

|

|

Создание схемного представления компонента производится через Design Entry Utilities > Create Schematic Symbol. Двойной щелчок на этом пункте запускает синтез схемотехнического представления компонента, при этом ход синтеза и результаты будут показаны в консоли системных сообщений в нижнем окне. Необходимо анализировать сообщения о результате трансляции, поскольку данная операция производит проверку корректности описания и синтезирует компонент по обычным правилам компиляции. При ошибках в описании, в том числе и методологических, будет выведено сообщение об ошибке и компонент создан не будет. На рисунке 6 показано окно «Project Navigator» после удачного завершения трансляции. В дерево процессов добавляются основные операции, которые соответствуют этапам проектирования устройства – трансляция, синтез, реализация (размещение и трассировка), генерация файла для программирования ПЛИС.

Рис. 6. Окно после создания нового компонента

4) Функциональное моделирование.

а) Для моделирования используется компонента Model Technology Incorporated (ModelSim). Необходимо убедиться, что она подключена к Xilinx ISE. Для определения пути к ModelSim, выберите Preferences в меню Edit, и выберите Par tners Tool (рисунок 7).Путь должен указывать на каталог, который содержит приложение. Изменения вступят в силу после выхода и перезапуска Project Navigator.

Рис. 7. Диалоговое окно для установления пути (ModelSim)

б) Формирование входных тестовых последовательностей. Добавить в проект новый источник New Source (тип – Test Bench Waveform). Выбрать файл, созданный с помощью схемного редактора или VHDL- файл. Задать тестовые последовательности для входных портов (рисунок 8). Сохранить файл.

Рисунок 8

в) Запуск на моделирование выполняется в окне «Processes for Current Source» Design Entry Utilities > Launch MolelSim Simulator двойным щелчком (рисунок 9).

г) Возможны следующие варианты завершения процессов:

- текущий процесс выполнен успешно;

- текущий процесс выполнен успешно;

-процедура исполнена без ошибок, но имеются предупреждения;

-процедура исполнена без ошибок, но имеются предупреждения;

-при выполнении процесса обнаружены ошибки (не соответствует исходным данным).

-при выполнении процесса обнаружены ошибки (не соответствует исходным данным).

- результаты выполнения процесса устарели

- результаты выполнения процесса устарели

Рисунок 9 - Моделирование схемотехнического представления компонента

|

|

|

Ошибки при выполнении трансляции могут возникать в следующих типичных ситуациях:

· В списке файлов не выбран нужный объект. Синтез производится не для объекта, исходный текст которого показан в текстовом редакторе главного окна, а для объекта, выбранного в списке файлов текущего проекта.

· После редактирования компонента возникла ошибка и активной осталась старая версия. После повторного синтеза компонента убедитесь в том, что компонент оттранслирован без ошибок.

· Синтез и реализация, просмотр отчетов и результатов размещения (для FPGA и CPLD).

При отсутствии ошибок на этапе трансляции для простого (не иерархического) проекта автоматически выполняются этапы синтеза (Synthesize) и реализации (Implement Design). Для иерархического проекта необходимо выполнить трансляцию всех составных частей.

Необходимо проанализировать результаты выполнения этапа синтеза и реализации, которые содержатся в соответствующем отчете. Для просмотра отчета удобнее всего дважды щелкнут левой кнопки мыши на строке с его названием в окне процессов (рисунок 10).

Рисунок 10

|

|

|