|

Комутатор Проза. Система МОС – 100. Система зберігання даних та програм в комп’ютерних системах

|

|

|

|

25. 11. 11

Комутатор Проза

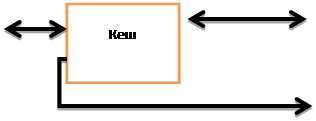

Комутатор проза має альтернативну організацію прямокутним комутаторам і відрізняється тим, що має організацію яка не змінюється від кількості точок з’єнання, має три ступені організації: вхідний, проміжний та вихідний:

Комутатор проза має альтернативну організацію прямокутним комутаторам і відрізняється тим, що має організацію яка не змінюється від кількості точок з’єнання, має три ступені організації: вхідний, проміжний та вихідний:

|  | ||

m(dxd) d(mxm) m(dxd)

Організація першого ступеня складається з m комутаторів по d входів, другий m входів і d комутаторів.

Правило з'єднання між ступенями наступне:

j-вихід і-го з і-входом j.

Вихід k ком. 3 з виходом j-го ком 2.

Система МОС – 100

Базовий вузол такої системи складається 4x4. Кожен процесор, який знаходиться на вузломову має чотири лінії зв’язку, найбільша довжина між елементами матриці дорівнює більше шести, тому для покращення комутаційних характеристик було запропоновано з’єднувати діагональні елементи цієї матриці за наступним принципом: максимальна довжина з’єднання зменшилася до чотирьох і це було одним з найкращих показників для такої кількості активних елементів. Останні 12 виходів використовуються для з’єднання з іншими зовнішніми активними чи пасивними елементами, це можуть бути додаткові процесори, зовнішня пам’ять тощо. Такий базовий вузол з 16 процесорів є основою для нарощування кількості процесорів в системі, з наступними варіантами з’єднання: вузол з 32 процесорів має максимальну довжину з’єднання 5, 16 вільних виходів, також можуть бути використанні для з’єднання з іншим вузлом, або підключення до додаткових пасивних елементів. Максимальна довжина підключення 128 процесорів, максимальна довжина з’єднання процесора з процесором дорівнює 7 затримкам. Тобто розглянута система є одним із вдалих експериментів побудови комутації. Існують окремі дисципліни, які займаються виключно розв’язання задач проблем комутації між елементами комп’ютерних систем, вони складають вагомий напрямок у мережних технологіях, розв’язання проблеми розв’язання паралельних процесів. Система MPI є прикладом організації в паралельних кластерних системах має свої недоліки, але не існує багато розв’язань і тому всі існуючі системи на даний час ґрунтуються на ній.

|

|

|

Система зберігання даних та програм в комп’ютерних системах

Система зберігання або пам’ять є необхідних складовою, без якої не існує комп’ютерних засобів або систем, якщо розглядати спрощену структуру ЕОМ процесор має декілька структурних одиниць, з якими він працює:

- Регістровий запам’ятовуючий пристрій, який використовується для реалізації алгоритмів обробки даних.

- Допоміжне запам’ятовуюча система, яка складається з односторонньої та постійної пам’яті.

- Керуюча пам’ять – пам’ять мікропрограм та службової інформації.

- Швидка пам’ять або кеш-пам’ять – буферний запам’ятовуючий пристрій.

- Основна пам’ять – яка може складатися з масової пам’яті, оперативної пам’яті.

- Пам’ять на зовнішніх носіях

- Пам’ять каналів, яка об’єднує дані з багатьох джерел: відеопам’ять, системи перетворення «аналог-цифра» (пам’ять сигналів), дані з терміналів, або з мережевих джерел. Головною проблемою при побудові високопродуктивних засобів була і є проблема підвищення роботи системи зберігання або пам’яті відносно швидкодії процесора. Завжди процесор працював швидше тому система керування вдосконалювалася і мала новітні рішення, які прискорювали роботу пам’яті: по-перше регістрова пам’ять, яка в деяких архітекторах віднесена до складу процесора, тобто працює як частина арифметично-логічного пристрою. Іще було запропоновано мати швидкодіючу пам’ять. Яка б виконувала завдання буфера між основною та процесорним пам’ятями. Буфер або кеш-пам’ять була запропонована на початку 60-х років, спочатку невеликого об’єму, а згодом і більше. Основний механіз запропонований для кеш: в програмах запропонованих для ЕОМ: в програмах є можливість багатократового використання підпрограм, або частин програм – такий маханізм названий локалізацією посилань, тобто такі багаторазові використані частини програм завантажити в таку частину пам’яті яка б підвищувала швидкодію взаємодії пам’яті. Був запропонований механізм, який був реалізований у вигляді контролера кеш та виконував би оперативні завантаження програм та команд або циклів, які мають велику частоту використання. Якщо в кеш пам’яті процесор не знаходив би потрібні дані чи програми, кеш повинна стати «прозорою» і обмін даними процесора чи програмами здійснювався б з основною пам’яттю. Схема:

|

|

|

| |||

| |||

Таке розв’язання дозволяє підвищувати загальну продуктивність до 1 порядку і більше. Кеш-пам’ять це пам’ять, яка працює за звичним принципом адресації таким чином, щоб адресація даних та програм, які записані і зберігаються в основній пам’яті не змінювалася, наприклад, маємо основну пам’ять яка має адресу з 12 розрядів, при використанні кешу з наступною організацією адресне поле розділяється наступним чином: 4 розряди – це адрес слова, який є в основній пам’яті, 7 розрядів – це адрес блоку, який розміщується в кеші, кожен блок по 16 слів, які адресуються 4-розрядним полем і кожен блок має тег, який є в адресній частині основоної пам’яті, тобто, коли потрібно звернутися до конкретної коміпки пам’яті, то щвернаються № блоку і асоціативний тег який конкретизує розміщення: тобто, якщо адреса була з 12 розрядів 7 розрядів реалізовано апаратнм 5 і 4 реалізуються звичайним чином. Чому в кеш пам’яті. Контроллер кешу будується на підставі статистичних даних, якщо зчитується комірка з певним адресними даними, то наступні комірка десь поблизу. Організація блоками, тобто заповнення кешу реалізується методом огляду наперед програм. Якщо контролеру кешу не знаходить блоку, який потрібний процесу для роботи, а кеш уже заповнений реалізується алгоритм видалення блоків – LRU (алгоритм заміщення). Для цього реалізований механізм: в контролері кешу для кожного блоку реалізується система підрахунку даних, якщо блок вперше переміщується з основної пам’яті до кешу, то значення 0. Інші схеми додають 1 до попередніх значень. Якщо процесор звертається до будь-якого блоку, схема підрахунку використання теж встановлюється в 0, а інші додають 1. Таким чином, за деякий час для кожного блоку формується код використання і якщо кеш заповнений повністю, то видаляється блок, яким має максимальне значення. Існує декілька механізмів фіксації даних кеш, якщо така фіксація є то це пряма реалізація, якщо такого механізму немає, а існує об’єднання № блоку та тегу, то блок, який переміщується може бути записаний у різне місце кеш пам’яті. При цьому назва такого механізму стає асоціативне відображення, тобто частина адресу вважається деяким кодовим ключем для розташування блоку певного розміру. Час роботи не зменшується при асоціативному відображення але вважається, що технологічно він краще. Кеш пам’ять як і основна працює на принципі адресації, тобто реалізація доступу до інформації передбачає використання адресу. Швидкодія пристроїв в пам’яті в основному залежить від швидкодії дешифраторів, які перетворюють адресні часу у відповідні сигналу. Тобто для підвищення швидкодії є розв’язання, які реалізуються на пристроях, які не мають адресної частини – це магазинна пам’ять, або стеки, які складаються з ансамблю регістрових структур пов’язаних між собою послідовним зв’язком. Регістрові структури працюють при апаратному керуванні, передаючи інформацію з входу пристрою між собою. Інформація, яка поступає на вхід стеку послідовно переміщається між регістрами заповнюючи послідовно всі слоти такої структури, кількість даних які зберігаються, фіксуються значенням флагу, який відображає ступінь заповнення такої структури. Керуючою програмою передбачено список джерел, які передають інформацію в стек у різних режимах роботи основного процесора. Якщо стек має таку організацію, що вхід і вихід реалізується через однакове обладнання, то по організації роботи такий стек керується алгоритмом «перший прийшов – першим вийшов», тобто щоб реалізувати зчитування якогось операнда потрібно перевантажити в інші джерела. Якщо організація стеку має різні рознесені в апаратурі входи та виходи реалізується алгоритм FIFO. Кожен з таких пристроїв має певний об’єм і частіше використовується при порушенні режиму роботи, при процедурі копіювання процедурі копіювання даних, а також спеціалізованих системах для формування черги по даних певного порядку. Наприклад, при цифровій обробці сигналів потрібно інверснодвійковий порядок даних, і якщо не реалізувати певну роботу з пам’яттю процесор може не виконати обробку в реальному часі. Наступним прикладом запам’ятовуючих пристроїв є ортогональне зчитування даних з відповідною апаратною підтримкою. Вперше системі ОМЕН-60 було використане ортогональне запам’ятовуюча система, яка відрізнялася від звичайної тим, що з масиву даних для обробки на звичайному процесорі з пам’яті зчитувався зріз по розрядах, які мають однакову вагу. Такий варіант організації обробки був реалізований для асоціативного пошуку. Тобто позначеннях старших розрядів формувалися маски, які швидко дозволяли визначити максимальні чи мінімальні значення в масиві. В такій пам’яті реалізується так званий вертикальний зріз по значенню керуючої інформації, яка має вигляд адресної частини. В подальшому такий принцип ортогональної обробки був реалізований а асоціативних процесорах а також в асоціативних пристроях зберігання, які працюють за принципом зчитування інформації по ключовому керуючому слову, яке передається замість адреси. Тобто маємо ключ або тег, який фіксує наявність такої комірки пам’яті (або кілька комірок) і на виході пристрою маємо результат перегляду всього масиву по ключу (тегу). З підвищенням рівня інтелектуалізації комп’ютерних засобів, які відповідають збільшенню задач, що розв’язуються по тупу «штучного інтелекту» такі пристрої зберігання мають все більше впровадження.

|

|

|

|

|

|

|

|

|