|

Архитектура микропроцессора КР580ВМ80А

|

|

|

|

Микросхема КР580ВМ80А — функционально законченный однокристальный параллельный 8-разрядный микропроцессор с фиксированной системой команд, применяется в качестве центрального процессора в устройствах обработки данных и управления. Микропроцессор имеет раздельные 16-разрядный канал адреса и 8-разрядный канал данных. Канал адреса обеспечивает прямую адресацию внешней памяти объемом до 65536 байт, 256 устройств ввода и 256 устройств вывода.

Восьмиразрядное арифметико-логическое устройство микропроцессора обеспечивает выполнение арифметических и логических операций над двоичными данными, представленными в дополнительном коде, а также обработку двоично-десятичных упакованных чисел.

В состав блока регистров входят: 16-разрядный регистр адреса команды (IP), 16-разрядный регистр указателя стека (SP), 16-разрядный регистр временного хранения (WZ), 16-разрядная схема инкремента-декремента и шесть 8-разрядных регистров общего назначения (B, С, D, Е, Н, L), которые могут использоваться и как три 16-разрядных регистра (ВС, DE, HL).

Микропроцессор выполняет команды по машинным циклам. Число циклов, необходимое для выполнения команды, зависит от ее типа и может быть от одного до пяти. Машинные циклы выполняются по машинным тактам. Число тактов в цикле определяется кодом выполняемой команды и может быть от трех до пяти. Длительность такта равна периоду тактовой частоты и при частоте 2,0 МГц составляет 500 нс.

6. Определение микроконтроллера.

Контроллером в технике регулирования считается управляющее устройство, осуществляющее регулирование или контролирующие функции в системе. Контроллер, реализованный на одном кристалле, называется микроконтроллером. Современный микроконтроллер является большой цифровой интегральной схемой, объединяющей миллионы, выполненных по микронным технологиям, транзисторов.

|

|

|

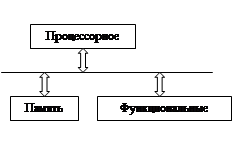

Типовая структура МК изображена на рис. МК состоит из трех, связанных системными шинами, элементов: процессорного ядра, памяти и набора программируемых функциональных блоков различного назначения.

Процессорное ядро является основой МК.

Процессорное ядро является основой МК.

Оно выполняет все вычислительные операции и, одновременно, управляет работой всех остальных элементов схемы.

По системным шинам ПрЯд обменивается данными с памятью и всеми функциональными блоками. Разрядность ПЯ определяет разрядность МК (4,8,16,32-битные).

В памяти хранится программа работы МК, исходные данные и все промежуточные результаты вычислений. Память состоит из множества многоразрядных ячеек, каждая из которых имеет свой адрес. Память МК обычно разделена на две части: память данных и память программ.

Функциональные блоки различных типов обеспечивают взаимодействие МК с внешним миром. Эти блоки могут выполнять самые различные функции: ввод и вывод информации, подсчет внешних событий и интервалов времени, передача внешних запросов на ПЯ, анолого-цифровые и цифроанологовые преобразования сигналов. Для ПЯ любой функциональный блок представляется в виде одного или нескольких регистров. Каждый регистр имеет свой оригинальный адрес, по которому ПЯ находит его процессе работы.

Программа работы МК хранится в памяти в виде последовательности команд. В процессе работы ПЯ последовательно извлекает из памяти инструкции, расшифровывает и выполняет их. В зависимости от инструкций в ядре выполняются различные арифметические и логические операции, пересылки данных. При необходимости, в процессе выполнения инструкций, ПЯ обращается за данными к ячейкам памяти и функциональным блокам, либо пересылает в них результаты вычислений. Множество инструкций, которые понимает ПЯ, образуют систему команд МК.

|

|

|

В настоящее время известны четыре общих архитектурных принципа в той или иной мере, реализуемых в любом ПЯ.

По организации памяти различаются:

- Неймановская архитектура – характеризуется общим пространством памяти для хранения данных и программы. При этом разрядность памяти зафиксирована (как правило 1 байт)

- Гарвардская архитектура – отличается разделением памяти программ и памяти данных. При этом разрядность памяти программ и памяти данных, а также шины доступа к ним, различны.

По системе команд различаются:

- CISC архитектура – архитектура с развитой системой команд. Система команд ПЯ имеет инструкции разного формата: однобайтовые, двухбайтовые, трехбайтовые. Различные имеют разное время исполнения.

- RISC архитектура – архитектура с сокращенным набором команд. Одна инструкция как правило занимает одну ячейку памяти, и все инструкции имеют равное время исполнения.

7. Процессорное ядро.

Каждый производитель МК для серии выпускаемых им изделий разрабатывает и патентует свое оригинальное процессорное ядро. Однако в большинстве из них присутствуют одни и те же элементы: регистр инструкций, программный счетчик, арифметико-логическое устройство, регистры общего назначения, регистр состояния, регистры ввода/вывода, стек.

Программный счетчик: регистр предназначенный для хранения адреса ячейки памяти программ, в которой находится выполняемая в данный момент инструкция. Разрядность программного счетчика определяется количеством ячеек в памяти программы. При выполнении команды содержимое ПС изменяется. В простейшем случае оно увеличивается на 1. Но некоторые команды способны сами записывать данные в ПС. В этом случае новое содержимое ПС и определяется данными, заложенными в выполняемой инструкции.

Регистр инструкций: регистр, предназначенный для хранения считанной из памяти программ инструкции. Считанная из памяти программ инструкция декодируется дешифратором команд и исполняется микропрограммным автоматом ядра. Разрядность регистра инструкций определяется разрядностью памяти программ.

Арифметико-логическое устройство: логическая схема, непосредственно осуществляющая преобразование одной или двух переменных в соответствии с инструкцией занесенной в регистр команд. Стандартное АЛУ способно выполнять простейшие арифметические или логические операции над одной или двумя переменными (сложение, вычитание, инкремент, декремент, NOT, AND, OR, exclusive OR). Некоторые производители интегрируют на кристалл также встроенный умножитель двух переменных.

|

|

|

Регистры общего значения: Регистры общего значения предназначены для временного хранения данных в процессе вычислений. Разрядность регистров определяет разрядность вычислений и разрядность самого МК. Количество регистров может быть произвольным. Обычно в этих регистрах хранится информация, обрабатываемая АЛУ и полученный в нем результат вычислений. На некоторые из регистров могут быть возложены дополнительные функции. В большинстве архитектур один из регистров отличается от других большими возможностями. Он обычно называется аккумулятор или рабочий регистр. В этом регистре может храниться одна из переменных, обрабатываемых в АЛУ, и туда же помещается результат операции.

Регистры ввода/вывода: предназначены для управления функциональными блоками МК, энергозависимой памятью данных и программ. В различных операциях регистры могут участвовать целиком или отдельными битами. Отдельный бит регистра именуется флагом. Обращение к регистрам в различных архитектурах организуется различным образом. Обычно обращение к ним осуществляется как к элементам процессорного ядра по присвоенным в архитектуре именам и адресам, в ряде случаев к ним обращаются с помощью специальных команд ввода/вывода.

Регистр состояния: предназначен для хранения отдельных признаков результата, полученного при выполнении различных арифметических и логических операций в АЛУ. Регистр обычно рассматривается состоящим из отдельных бит (флагов), каждый из которых несет в себе определенную информацию о каком либо одном признаке результата. Типовыми флагами регистра состояния являются:

|

|

|

- флаг переноса: устанавливается при возникновении переноса из старшего разряда результата.

- флаг переполнения: устанавливается при переполнении разрядной сетки.

- флаг отрицательного результата: устанавливается, когда результат является отрицательным числом.

- флаг нулевого результата: устанавливается, когда результат операции равен нулю.

- флаг полупереноса: устанавливается при возникновении переноса из младшей тетрады 8-битного числа в старшую (из третьего разряда в четвертый).

Стек: память данных, организованная по принципу: последний зашел - первый вышел. Такая память предназначается, обычно, для оперативного сохранения содержимого отдельных регистров при переходах к подпрограммам. Одним из таких регистров является программный счетчик. Извлечение из стека содержимого регистров производится в порядке, обратном порядку записи. Запись в стек и извлечение из стека не требует знания адреса ячеек памяти, в которые записываются данные. Стек может быть организован либо в специально созданных в ядре ячейках памяти, либо в области SRAM. В последнем случае в ядре предусматривается специальный регистр – указатель стека. Указатель стека хранит адрес последней записанной ячейки памяти в области стека. Количество ячеек памяти, которые используются в стеке для хранения данных, именуется глубиной стека. Глубина стека в различных архитектурах ядра может быть различна: от 2-х ячеек до размера SRAM.

Классификация команд

Множество инструкций микроконтроллера образует систему команд. Система команд, как правило, не меняется для всех микроконтроллеров одного семейства. В полном списке инструкций при описании системы обычно выделяются отдельные группы, родственных по применению инструкций, например, арифметические и логические команды, команды пересылки и др. Это деление довольно условно и полностью определяется политикой разработчика.

При описании системы команд приводится полная информация о каждой инструкции: способах адресации, использовании флагов регистра состояния, времени исполнения.

В качестве примера рассмотрим систему команд микроконтроллера А Ттеда 163

Система команд микроконтроллера содержит 130 команд, условно разделенных на четыре группы:

команды пересылки данных (data transfer instructions), 0 арифметические и логические команды (arithmetic and logic instructions), ° команды работы с битами (bit and bit-test instructions), ° команды ветвления (branch instructions).

При описании системы команд использованы следующие обозначения:

Rd - регистр-приемник результата (0 < d < 31),

Rd* - регистр-приемник результата с номером более 16 (16 < d < 31),

|

|

|

Rr-регистр-источник (0 < г < 31),

Rdl: регистры R24, R26, R28, R30 (для инструкций ADIW и SBIW),

Р- адрес регистра ввода/вывода, Р*- адрес побитно адресуемого регистра ввода/вывода ($00-$1F)

К - символьная или численная константа (8 бит)

к - адресная константа

b - номер бита в регистре (3 бита)

0 s - номер бита в регистре статуса (3 бита)

0 X, Y, Z - регистры косвенной адресации (X=R27:R26, Y=R29:R28; Z=R31:R30 Команды пересылки

Команды пересылки осуществляют перемещение данных между ячейками памяти и регистрами процессорного ядра. Один из операндов, участвующих в инструкции, является источником данных, второй - приемником. При пересылке из источника в приемник копия данных всегда остается в источнике. Таким образом, все команды пересылки практически осуществляют копирование данных.

Одним из операндов в любой команде пересылки обычно является регистр общего назначения процессорного ядра. Вторым может быть любой регистр или ячейка памяти.

Инструкции, как правило, не влияют на флаги в регистре состояния процессорного ядра.

В системе команд микроконтроллеров AVR предусмотрено 34 инструкции, осуществляющие пересылку данных. В инструкциях используются все, за исключением битовых, способы адресации данных; одним из операндов в любой инструкции является регистр общего назначения. Инструкция Idi (toad immediate), использующая непосредственную адресацию, может быть использована только в старшей половине файла регистров общего назначения (R16....R31), остальные команды работают с любым из регистров файла. Инструкцию spm (store program memory), осуществляющую запись когда в память программ, можно использовать только в Boot Program Section памяти программ;

Время выполнения инструкций, работающих с регистрами, равно 1 такту. Инструкции, обращающиеся к ячейкам памяти данных, выполняются за 2 такта, а 'вращающиеся к ячейкам памяти программ - за 3 такта.

|

|

|

|

|