|

Организация обмена прямым доступом к памяти (ПДП)

|

|

|

|

Одним из способов обмена данными с ВУ является обмен в режиме прямого доступа к памяти (ПДП). В этом режиме обмен данными между ВУ и основной памятью микроЭВМ происходит без участия процессора. Схема, управляющая обменом в режиме ПДП, размещаются в специальном контроллере, который называется КПДП. Обмен данными в режиме ПДП позволяет использовать в микроЭВМ быстродействующие внешние запоминающие устройства, такие, например, как накопители на жестких магнитных дисках, поскольку ПДП может обеспечить время обмена одним байтом данных между памятью и ВЗУ, равное циклу обращения к памяти.

Одним из способов обмена данными с ВУ является обмен в режиме прямого доступа к памяти (ПДП). В этом режиме обмен данными между ВУ и основной памятью микроЭВМ происходит без участия процессора. Схема, управляющая обменом в режиме ПДП, размещаются в специальном контроллере, который называется КПДП. Обмен данными в режиме ПДП позволяет использовать в микроЭВМ быстродействующие внешние запоминающие устройства, такие, например, как накопители на жестких магнитных дисках, поскольку ПДП может обеспечить время обмена одним байтом данных между памятью и ВЗУ, равное циклу обращения к памяти.

Для реализации режима прямого доступа к памяти необходимо обеспечить непосредственную связь контроллера ПДП и памяти микроЭВМ. Контроллер ПДП подключается к памяти посредством шин адреса и данных системного интерфейса.

Существуют две разновидности прямого доступа к памяти с "захватом цикла". Наиболее простой способ организации ПДП состоит в том, что для обмена используются те машинные циклы процессора, в которых он не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора. Однако возникает необходимость выделения таких циклов, чтобы не произошло временного перекрытия обмена ПДП с операциями обмена, инициируемыми процессором. В некоторых процессорах формируется специальный управляющий сигнал, указывающий циклы, в которых процессор не обращается к системному интерфейсу. Такой обмен в режиме ПДП возможен только в случайные моменты времени одиночными байтами или словами.

Более распространенным является ПДП с "захватом цикла" и принудительным отключением процессора от шин системного интерфейса. Для реализации такого режима ПДП системный интерфейс микроЭВМ дополняется двумя линиями для передачи управляющих сигналов "Требование прямого доступа к памяти" (ТПДП) и "Предоставление прямого доступа к памяти" (ППДП).

|

|

|

Управляющий сигнал ТПДП формируется контроллером прямого доступа к памяти. Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, не дожидаясь ее завершения, выдает на системный интерфейс управляющий сигнал ППДП и отключается от шин системного интерфейса. С этого момента все шины системного интерфейса управляются контроллером ПДП. Контроллер ПДП, используя шины системного интерфейса, осуществляет обмен одним байтом или словом данных с памятью микроЭВМ и затем, сняв сигнал ТПДП, возвращает управление системным интерфейсом процессору. Как только контроллер ПДП будет готов к обмену следующим байтом, он вновь "захватывает" цикл процессора и т.д. В промежутках между сигналами ТПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы замедляется, но в меньшей степени, чем при обмене в режиме прерываний.

Применение в микроЭВМ обмена данными с ВУ в режиме ПДП всегда требует предварительной подготовки, а именно: для каждого ВУ необходимо выделить область памяти, используемую при обмене, и указать ее размер, т.е. количество записываемых в память или читаемых из памяти байт (слов) информации. Следовательно, контроллер ПДП должен обязательно иметь в своем составе регистр адреса и счетчик байт (слов). Перед началом обмена с ВУ в режиме ПДП процессор должен выполнить программу загрузки. Эта программа обеспечивает запись в указанные регистры контроллера ПДП начального адреса выделенной ВУ памяти и ее размера в байтах или словах в зависимости от того, какими порциями информации ведется обмен. Сказанное не относится к начальной загрузке программ в память в режиме ПДП. В этом случае содержимое регистра адреса и счетчика байт слов устанавливается переключателями или перемычками непосредственно на плате контроллера.

|

|

|

Интерфейс UART.

Асинхронный последовательный интерфейс UART (Universal Asynchronous Receiver Transmitter – универсальный асинхронный приемопередатчик) обеспечивает полудуплексный режим обмена по трем линиям. В обмене всегда участвуют только два устройства, одно из которых является передатчиком, второе – приемником.

В режиме асинхронной передачи каждое слово данных передается автономно и передача может быть начата в любой момент времени. Стандартный формат асинхронной передачи:

Передача начинается со стартового (нулевого) бита. Затем передается от 5 до 8 бит данных.

Подразумевается, что приемник и передатчик работают на одной скорости. Внутренний генератор синхронизации запускается при обнаружении стартового бита.

В простейшем случае асинхронный приемопередатчик имеет две сигнальные линии:

TxD (Transmit Data)-выход,

RxD (Receive Data)-вход.

При этом два устройства-приемопередатчика должны быть соединены между собой тремя линиями, или мак называемым нуль-модемным кабелем:

Интерфейс SPI.

Последовательный интерфейс SPI(Serial Peripheral Interface) обеспечивает полный дуплексный обмен данными между двумя контроллерами. При этом один контроллер считаемся ведущим (master), второй – ведомым (slave). Ведущий контроллер является источником сигнала синхронизации (SCK).

Ведущий и ведомый контроллеры связаны тремя сигнальными линиями:

MISO (Master In Slave Out) – вход ведущего – выход ведомого.

MOSI (Master Out Slave In) – выход ведущего – вход ведомого.

SCK (Serial Clock) – синхронизация.

Контакт #SS (Slave Select) – предназначен для выбора ведомого контроллера. Контроллер является ведомым если #SS=0.

Регистры сдвига (Shift Register) ведущего и ведомого контроллеров по линиям MOSI и MOSO соединяются в кольцо. Запись в регистр данных ведущего контроллера запускает генератор синхронизации (SPI clock generator) и данные сдвигаются в регистрах сдвига соединенных в кольцо ведущего и ведомого контроллеров.

Интерфейс I2C.

2-проводной последовательный интерфейс (2-Wire Serial Interface) или I2C (Inter-Integrated Circuit) поддерживает двунаправленную последовательную связь нескольких устройств в полудуплексном режиме. В системе все устройства, участвующие в обмене, связываются двумя сигнальными линиями:

|

|

|

SDA (Serial Data) – данные.

SCA (Serial Clock) – синхронизация.

Типичная 2-х проводная последовательная конфигурация шины:

Каждое из устройств может выступать в роли передатчика или приемника. Синхронизацию обмена обеспечивает передатчик. Двунаправленную линию данных, выполненную по схеме «открытый коллектор» используют передатчик и приемник поочередно.

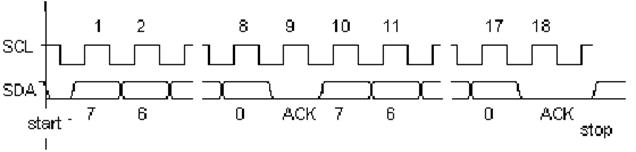

Начало любой операции (Start) инициализируется переводом сигнала SDA из высокого уровня в низкий при высоком уровне SCL. Завершается обмен переводом сигнала SDA из низкого уровня в высокий при высоком уровне SCL (Stop).

При передаче данных состояние линии SDA может изменяться только при низком уровне SCL. Биты данных стробируются положительным фронтом SCL.

Каждая посылка, формируемая передатчиком, состоит из байта данных. Посылка начинается со старшего бита. После чего передатчик на один такт освобождает линию, а приемник формирует нулевой сигнал подтверждения Ack (Acknowledge).

Каждое ведомое устройство имеет свой 7-битный адрес. Семь бит адреса передаются ведущим устройством в битах [7-1] первого байта.

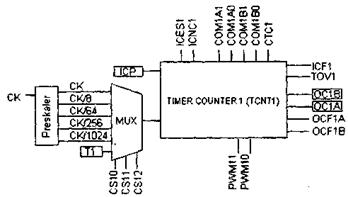

25. 16-бит т/с1 мик-ра доступен проц-му ядру для чтения и записи, он может считать импульсы синхронизации CK импульсы с выхода предделителя или импульсы с внешнего вывода Т1.

Шесть 16 бит рег-в обеспечивают режимы вх-го захвата, вых-го сравнения и ШИМ.

16-бит т/с1 считает импульсы со входа Т1 или тактовые импульсы СК.

Переключением входа управляют биты CS10....CS12.

При переполнении - флаг запроса на прерыв-е TOV1.

регистры упр т/с1 TCCR1A и TCCR1B;

регистры данных TCNT1H и TCNT1L;

регистры выходного сравнения OCR1AH и OCR1AL;

регистры выходного сравнения OCR1BH и OCR1BL;

регистры входного захвата - ICR1H и ICR1L;

регистр флагов прерывания TIFR;

регистр маски прерывания TIMSK;

регистр состояния микроконтроллера SREG.

Регистр масок прерываний TIMSK уст-ся разрешения/запрещения прерываний т/с1:

|

|

|

Бит 5 -TICIE1 бит разрешения прерывания при срабатывании входа захвата.

Бит 4 - OCIE1A бит разрешения прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1 А.

Бит 3 - OCIE1B бит разрешения прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1B.

Бит 2 - TOIE1 бит разрешения прерывания при переполнении таймера/счетчика 1.

Регистр флагов прерываний T1FR фиксируются события, являющиеся источниками прерываний:

Бит 5 - ICF1 флаг прерывания при возникновении захвата.

Бит 4 - OCF1A флаг прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1A.

Бит 3 - OCF1B флаг прерывания при равенстве содержимого счетчика и содержимого регистра сравнения OCR1B.

Бит 2 - TOV1 флаг прерывания при переполнении таймера/счетчика 1.

В регистре управления TCCR1B находятся биты для переключения входа счетчика/таймера 1.

Упр-е входом т/с1. Рег-ы данных TCNT1H и TCNT1L содержат зн-е т/с 1.Если проц-е ядро производит запись в TCNT1H, то данные размещаются в регистре TEMP. Затем, когда процессорное ядро производит запись вTCNT1L данные младшего байта объед-я с байтом данных регистра TEMP и все 16 битов одновременно переписываются в регистр таймера/счетчика TCNT1.Если CPU считывает TCNT1L, то содержимое TCNT1L направляются непосредственно в процессорное ядро, а содержимое TCNT1Н размещается в регистре TEMP. При считывании TCNT1H его содержимое будет изъято из регистра TEMP.

ВХОД ЗАХВАТА. Ф-я захвата заключается в копировании содержимого т/с1 в регистр входа захвата ICR1.

Регистры входа захвата ICR1H и ICR1L образуют 16-битный регистр ICR1, доступный только для чтения.

При нарастающем или падающем фронте сигнала ICP (опр уст-ой бита ICES1) состояние т/с 1 пересылается в регистр входа захвата ICR1. Одновременно устанавливается в состояние 1 флаг захвата входа ICF1 в регистре флагов прерывания TIFR

Для упр-я входом захвата используются биты TCCR1B:

Бит 7 - ICNC1 установка режима подавления шума на входе захвата 1. При установленном в 1 бите ICNC1 импульс, поступивший на вход захвата IC1 подвергается серьезной проверке - состояние входа IC1 опр-ся 4 раза.

Бит 6 - ICES1 выбор фронта срабатывания на входе захвата 1. При сброшенном в состояние 0 бите ICES1 содержимое т/с 1 пересылается в регистр захвата входа ICR1 по падающему фронту на входе.

ВЫХОДЫ СРАВНЕНИЯ. Т/с1 поддерживает два выхода сравнения, OCR1А и OCR1B в качестве источников данных, сравниваемых с содержимым таймера/счетчика 1.

Регистры выходов сравнения OCR1AH и OCR1AL, OCR1BH и OCR1BL образуют два 16-разрядных регистра OCR1A и OCR1B. OCR1A и OCR1B 16-битные то для обеспечения одновременного занесения старшего и младшего байтов данных в регистры OCR1A/B используется регистр временного хранения TEMP.

|

|

|

Регистр управления TCCR1A: Биты 7,6 - СОМ1А1, СОМ1А0 биты задания режима выхода А Биты 5,4 - СОМ1В1, СОМ1В0 биты задания режима выхода В. При изм битов СОМ1Х1/СОМ1Х0 прерывания должны быть запрешены.

Регистр TCCR1B: Бит 3 - СТС1 очистка таймера/счетчика 1 no совпадению. ШИМ.Т/с 1 может быть использован в качестве 8, 9 или 10-разрядного ШИМ. Работой PWM управляют отдельные биты регистра управления TCCR1A:

Биты 1,0 - PWM11, PWM 10 биты выбора режима широтно-импульсной модуляции. Данные биты определяют установку режима ШИМ.

Таймер/счетчик1 в этом случае работает как реверсивный счетчик, считающий от $0000 до значения ТОР, при котором направление счета меняется и отсчет ведется до нуля, после чего цикл повторяется.

ТОР значения таймера и частота ШИМ

| Разрешение ШИМ | ТОР значения таймера | Частота ШИМ |

| 8-разрядное | $OOFF (255) | f/510 |

| 9-разрядное | $01FF(511) | f/1022 |

| 10-разрядное | $03FF(1023) | f /2046 |

В ШИМ режиме флаг переполнения таймера 1 (TOV1) устанавливается при смене направления счета по достижении значения $0. Прерывание по переполнению таймера/счетчика 1 работает так же как и в обычном режиме таймера/счетчика, т.е. оно выполняется когда флаг TOV1 в регистре T1FR установлен, установлен бит I в регистре SREG и разрешены прерывания по переполнению таймера 1.

|

|

|