|

Синхронный транспортный модуль STM-N

|

|

|

|

Структура STM-N представлена ранее на рис. 3.1. Она формируется побайтовым мультиплексированием N-го числа {N = 4, 16, 64 и 256) AUG и присоединением к этой вновь созданной структуре секционных заголовков SOH, которые разделяются на заголовок секции регенерации RSOH и секции мультиплексирования MSOH (рис. 3.31). На рис. 3.32-3.34 представлены примеры заголовков STM-4, STM-16, STM-64.

|

|

|

|

Байты Al, А2 определены двумя фиксированными группами битов:

А1: 11110110,

А2: 00101000.

Число этих байтов от SOH STM-1 до STM-64 возрастает пропорционально N (N=1,4, 16, 64). Для STM-256 заголовок уточняется относительно А1 и А2 для будущих стандартов.

Байт J0 характеризуется как маршрут секции регенерации. Используется в шестнадцати подряд следующих STM-N. При этом один байт служит для контроля ошибок по алгоритму CRC-7, а остальные 15 байтов служат в качестве идентификатора. Структура байта J0 приведена на рис. 3.35. В примерах заголовков MSOH и RSOH (рис. 3.32-3.34) использованы следующие обозначения, описанные ниже.

|

Байт Z0 зарезервирован для будущих стандартов.

Байт В1 служит для контроля ошибок на регенерационной секции по алгоритму BIP-8.

Байты El, Е2 служат для организации канала речевой служебной связи в секциях регенерации и мультиплексирования.

Байт F1 может быть определен оператором для своих целей (канал передачи документальных или звуковых сигналов).

Байты D1-D3 образуют канал передачи данных сетевого управления в секции регенерации DCCr (Data Communication Channel regeneration) на скорости 192 кбит/с.

Байты D4-D12 образуют канал передачи данных сетевого управления в секции мультиплексирования DCCm (Data Communication Channel multiplexing) на скорости 576 кбит/с. В заголовке MSOH STM-256 число байтов может быть увеличено до 156 для скорости до 9216 кбит/с.

|

|

|

Байты В2 используются для контроля ошибок в секции мультиплексирования по алгоритму BIP-Nx24.

Байты Kl, К2 (биты 1...5) используются для автоматического защитного переключения секции мультиплексирования согласно Рекомендации МСЭ-Т G.841. Для индикации дефекта удаленной стороны секции мультиплексирования применяют биты (6...8) байта К2.

Байт S1 определяет статус синхронизации в битах (5...8), распространяемой линейным сигналом. В табл. 3.8 представлены биты байта S1 и указаны их значения.

Необходимо отметить, что обозначения младших битов байта S1 имеют в технической литературе различную трактовку. Так Рекомендацией МСЭ-Т G.781 допускаются варианты трактовки комбинации бит 0010 как показателя качества синхросигнала Q1 или Q2 (согласно двоичного и шестнадцатеричного кодирования). При этом смысл обозначения одинаков: источник синхросигнала высшего качества, первичный эталонный генератор (ПЭГ) — атомные часы (водородные, цезиевые или рубидиевые). Причиной подобных разночтений являются различные международные и национальные стандарты в области телекоммуникаций. Аналогично, качество вторичного задающего генератора (ВЗГ) может иметь обозначение в двоичном коде 0100, что трактуется в одном случае Q2, а в другом — Q4. Качество генератора сетевого элемента ГСЭ обозначается в двоичном коде 1011, что трактуется в одном случае Q4, а в другом QB и т.д. Старшие биты байта S1 не определены по своему назначению.

|

Байты МО, Ml применяются для сообщений об ошибках удаленной стороны (MS-REI). В STM-N (N= 0, 1,4, 16) применяется байт Ml.

В STM-N (N= 64 и 256) применяются два байта (МО, Ml).

В STM-1 генерируется Ml по результатам контроля BIP-24.

В STM-4 генерируется байт Ml по результатам контроля BIP-96.

В STM-16 генерируется байт Ml по результатам контроля BIP-384.

Байт МО расширяет пространство интерпретации ошибок в STM-64 и STM-256.

Байты FEC, FEC2, PI, Q1 зарезервированы для реализации функций упреждающей коррекции ошибок FEC (Forward Error Correction). Возможности FEC с кодами Рнда-Соломона (RS) демонстрируются на рис. 3.36. Участки применения заголовков RSOH и MSOH в системе передачи SDH указаны на рис. 3.37.

|

|

|

3.1.5. Формирование указателей PTR

Указатели административных блоков AU-n подразделяются на указатели для AU-3 и AU-4. Они одинаковы по своей структуре, поэтому рассматривается указатель PTR AU-4 (рис. 3.38, 3.39). Он представлен байтами HI и Н2. Биты указателя имеют следующее назначение: N — биты флага новых данных NDF (New Data Flag); S — биты идентификатора типа AU-n; I — биты сообщения об увеличении значения PTR на единицу; D — биты сообщения об уменьшении значения PTR на единицу; 1* — байты с единичным заполнением (11111111); Y — байты с заполнением 1001SS11; S — биты не определенные по назначению.

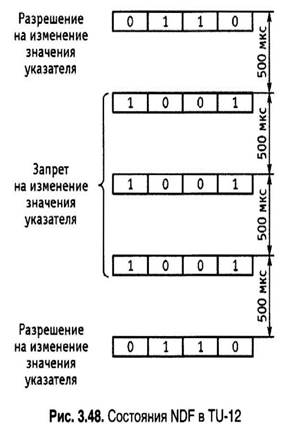

Флаг новых данных NDF может иметь два состояния: 1001 и 0110. Первое состояние указывает на возможность изменения указателя. Второе состояние указывает на невозможность изменения указателя. Из пяти бит D или I минимум три бита должны приниматься с инверсией в случае подстройки указателя. Биты SS имеют состояние «10» для AU-4, AU-4-Xc, AU-3. В случае применения сцепления (последовательного или виртуального) значения битов SS могут быть изменены, что в настоящее время не специфицируется.

Три байта НЗ и три байта, примыкающие к байтам НЗ справа, используются для процедур согласования скоростей. Адресуемое пространство PTR AU-4 представляет в 10-разрядном коде числа от 0 до 1023, что недостаточно для идентификации по байтам начала нагрузки VC-4 в AU-4, т.к. число байтов AU-4 составляет 2349 1261x9). По этой причине идентификатор PTR используется для триад байтов 783 = 2349:3. Адресуемое пространство составляет 0...782 триады байтов AU-4 spec. 3.39).

|

Процедуры согласования скоростей в AU-4 необходимы для компенсации измерения фазы VC-4 по отношению к AU-4, что обусловлено различием тактовых час- ют VC-4 и AU-4, возникающим по различным причинам (изменение длины пути, дрейф частот задающих генераторов и т.д.). Согласование скоростей связано с изменением значений указателей, которые могут возрастать или уменьшаться на единицу. Рис. 3.40, 3.41 иллюстрируют процедуры изменений указателей при подстройке под фазу VC-4.

|

|

|

|

|

Положительное согласование происходит в случае, если частота загрузки VC-4 ниже частоты AU-4. При этом согласовании скоростей байты триады «0» сдвигаются на одну триаду вправо в третьем цикле согласования, а в четвертом цикле согласования значение PTR AU-4 увеличивается на единицу.

Отрицательное согласование происходит в случае, если частота загрузки VC-4 выше частоты AU-4. При этом согласовании скоростей байты триады «0» сдвигаются на одну триаду влево в третьем цикле согласования, а в четвертом цикле согласования значение PTR AU-4 уменьшается на единицу.

Генерация и интерпретация указателя PTR AU-4 происходит в несколько этапов.

Генерация указателя в передатчике:

- прохождение нормальных операций обработки данных по размещению VC-4 в AU-4, значение флага новых данных — 0110;

- значение указателя может преобразовываться по одной из операций, перечисленных ниже.

В случае требуемого положительного согласования скоростей VC-4 и AU-4 содержимое указателя передается с инверсией бит I, и становится возможным положительное выравнивание последовательности с балластным заполнением информационной триады «0». Последовательность указателя увеличивается на единицу. Если значение указателя было 782, то он обнуляется.

После этой операции запрещается изменение указателя в последующих трех циклах.

В случае требуемого отрицательного согласования скоростей VC-4 и AU-4 содержимое указателя передается с инверсией бит D, и становится возможным отрицательное выравнивание последовательности с перезаписью вперед данных VC-4. Значение указателя уменьшается на единицу. Если предшествующее значение указателя было 0, то оно становится равным 782. После этой операции запрещается изменение указателя в последующих трех циклах.

Новое значение указателя сопровождается изменением флага новых данных на состояние «1001». Такой флаг передается только в первом цикле нового значения указателя. Полный цикл согласования скоростей AU-4 и VC-4 занимает 500 мкс.

|

|

|

Интерпретация указателя в приемнике:

- нормальное прохождение операций с указателем, обозначающим начало VC-4 в цикле AU-4;

- какое-либо отклонение в последовательности значений указателя не может быть пропущено, поскольку отклонение является признаком нового адреса, и на приемной стороне должна быть выполнена обработка указателя по одной из трех операций, перечисленных ниже:

■ если в значении указателя инвертированы биты I, то это признак положительного согласования, и последовательность PTR интерпретируется на единицу больше;

■ если в значении указателя инвертированы биты D, то это признак.отрицательного согласования, и последовательность PTR интерпретируется на единицу меньше;

■ если NDF интерпретируется как для совпадающего нового указателя один раз, то это является индикацией нового значения указателя в приемнике и также может быть интерпретировано как потеря указателя.

Для индикации сцепки используется состояние битов указателя — 1001SS1111111111.

Структура указателя компонентного блока TU-3 аналогична структуре указателя AU-4 (рис. 3.42). При этом все биты байтов HI и Н2 имеют одинаковое с AU-4 назначение. Принципиальные различия PTR AU-4 и TU-3 состоят в образуемом пространстве указателя и использовании в TU-3 одного байта НЗ для отрицательного согласования и байта с адресом 0 — для положительного согласования. Указатель TU-3 фиксирует начало цикла загрузки VC-3 в TU-3.

Флаг новых данных и метка типа TU-3 идентичны ранее рассмотренным в AU- 4. Также аналогично функционирование PTR TU-3 при отрицательном и положительном согласовании VC-3 и TU-3.

В случае мультиплексирования трех TU-3 в структуру VC-4 и размещения последней в AU-4 и AUG, функции указателей PTR TU-3 сохраняются без изменений «рис. 3.43).

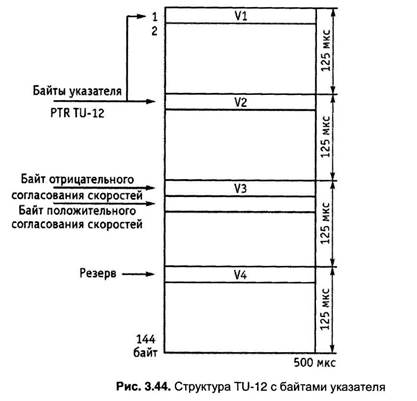

К структуре указателя компонентного блока TU-12 относятся байты VI, V2, V3, V4 (рис. 3.44).

|

Функции флага новых данных аналогичны ранее рассмотренным для PTR AU-4. Идентификация битами S типа TU-n соответствует: TU-11 (11); TU-12 (10); TU-2 (00).

Адресуемое пространство обозначается битами I, D и составляет 0...139 (рис. 3.45). Это пространство начинается после байта V2. Байт 35 этого адресуемого пространства, предусмотренный после V3, обеспечивает положительное согласование скоростей TU-12 и VC-12.

|

Пример размещения VC-12 в TU-12 приведен на рис. 3.46. Отрицательное и положительное согласование скоростей TU-12 и VC-12 проходит аналогично AU-4. При этом полный цикл согласования занимает 2 мс. На рис. 3.47 показано одно из возможных состояний нагрузки VC-12 в блоке TU-12.

На рис. 3.48 представлена структура флага новых данных TU-12. Для индикации сцепки используется состояние бит указателя — 1001SS1111111111.

|

|

|

|

|

|

|

|

|