|

Минимизация логических уравнений

|

|

|

|

Целью минимизации одиночных логических функций является сокращение ранга и числа элементарных конъюнкций, входящих в исходную ДНФ логической функции. В результате минимизации по таким критериям могут быть получены кратчайшие и/или минимальные тупиковые дизъюнктивные нормальные формы, обеспечивающие минимальную структурную сложность при реализации логической функции в элементных базисах И, ИЛИ, НЕ; И-НЕ; ИЛИ-НЕ и прочих.

При реализации системы логических функций на программируемой логической матрице наиболее эффективен метод групповой минимизации, который легко реализуется и гарантирует минимизацию площади ПЛМ, занимаемой на кристалле интегральной схемы.

Простейший метод групповой минимизации состоит в следующем: в системе логических уравнений для функций возбуждения и функций выходов отыскиваются группы одинаковых элементарных конъюнкций.

Для каждой группы одинаковых элементарных конъюнкций вводится фиктивная переменная с каким – либо индексом (например, Z1, … Zs). Далее все исходные логические уравнения переписываются в терминах фиктивных переменных.

Таблица 6 – Минимизация логических уравнений

| Переменная | Значение | Переменная | Значение |

| Z1 |  * *  * *  * *  * *

| Z13 |  * *  * *  * *  * *

|

| Z2 |  * *  * *  * *  * *

| Z14 |  * *  * *  * *

|

| Z3 |  * *  * *  * *  * *

| Z15 |  * *  * *  * *  * *  * *

|

| Z4 |  * *  * *  * *  * *

| Z16 |  * *  * *  * *  * *  * *

|

| Z5 |  * *  * *  * *  * *

| Z17 |  * *  * *  * *  * *

|

| Z6 |  * *  * *  * *  * *

| b1 |  * *  * *  * *

|

| Z7 |  * *  * *  * *  * *

| b2 |  * *  * *  * *

|

| Z8 |  * *  * *  * *  * *

| b3 |  * *  * *  * *

|

| Z9 |  * *  * *  * *  *1 *1

| b4 |  * *  * *  * *

|

| Z10 |  * *  * *  * *  * *

| b5 |  * *  * *  * *

|

| Z11 |  * *  * *  * *  * *

| b6 |  * *  * *  * *

|

| Z12 |  * *  * *  * *  * *  * *

| b7 |  * *  * *  * *

|

f0=z1+z2+z3+z5+z12+z14

f1=z1+z5+z7+z10

f2=z1+z3+z7+z13

f3=z2+z5+z7+z9+z13+z15

y1=z9+b5+b6

y2=b2+b3+z9+b6+z14

y3=b1+b6+z14

y4=b2+b3+z9+z14

y5=b1+z9+b6+b7

y6=b4+b5+b6+b7

y7=b1+b3+b4+z14+b7

4 РАЗРАБОТКА И ОФОРМЛЕНИЕ СХЕМЫ ЭЛЕКТРИЧЕСКОЙ ФУНКЦИОНАЛЬНОЙ СИНТЕЗИРОВАННОГО СИНХРОННОГО УА

|

|

|

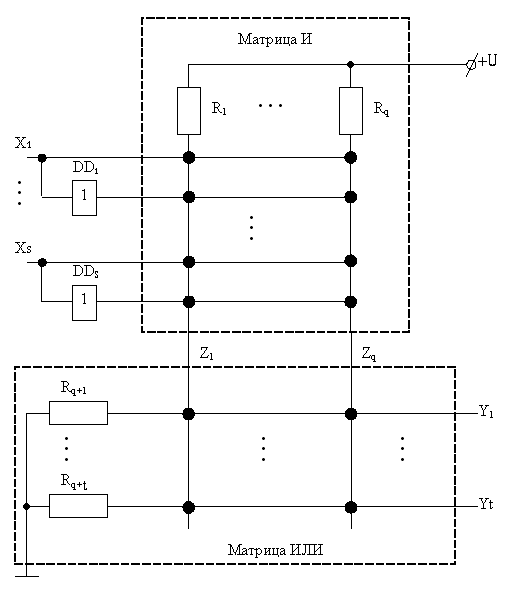

Схема электрическая функциональная синтезируемого СУА состоит из объединенных схем функциональных блока памяти и логического преобразователя, реализованного на двухуровневой программируемой логической матрице.

Рисунок 4.1

Как видно из рисунка 4.1 ППЛМ состоит из блока инверторов (DD1...DDS) входных логических переменных (X1...XS) и двух матриц. Матрица И реализует на шинах Z1...Zq элементарные конъюнкции с любым набором прямых и инверсных значений логических переменных X1...XS, а матрица ИЛИ реализует элементарные дизъюнкции с элементарными конъюнкциями, сформированными на шинах Z1...Zq. Результат операций дизъюнкции формируется на выходных шинах Y1...Yt. Матрицы И и ИЛИ представляют собой систему ортогональных проводников, в узлах пересечения которых располагаются полупроводниковые элементы, реализующие с резисторами нагрузки операции И и ИЛИ. Операцию И реализуют при помощи диодов, а операцию ИЛИ – при помощи триодов.

Электрическое подключение диодов и триодов к соответствующим ортогональным проводникам осуществляется через специальные перемычки Pi (Pj), некоторые из которых при программировании ППЛМ удаляются (пережигаются) в соответствующих узлах.

Схема электрическая функциональная синтезированного СУА представлена в ПРИЛОЖЕНИИ.

ЗАКЛЮЧЕНИЕ

В результате выполнения курсового проекта был проведен синтез синхронного управляющего автомата, включающий: разметку ГСА, кодирование внутренних состояний, выбор количества триггеров, составление таблицы структурных кодов СУА, структурный синтез ЛП, реализация блоков СУА на ПЛМ и триггерах и вычерчивание схемы электрической функциональной.

Заданный автомат реализован полностью, при этом была использована модель управляющего автомата Мура и двухтактные синхронные D-триггеры в качестве элементов памяти. Использовано второе эффективное кодирование внутренних состояний.

|

|

|

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

Воробьев Н.И. Проектирование электронных устройств: Учебное пособие. – М.: Высш. шк., 1989. – 223 с.

|

|

|