|

Мультиплексоры и демультиплексоры

|

|

|

|

Мультиплексор (MX) (другие названия – селектор данных, коммутатор) – это комбинационное логическое устройство, предназначенное для управляемой передачи данных, которые поступают по нескольким входам, на один выход. Выбор того или иного входа осуществляется в соответствии с поступающим кодом адреса. Согласно определению, мультиплексор имеет две группы входов (информационные и адресные) и один выход. Код, подаваемый на адресные входы, определяет, какой из информационных входов в данный момент подключен к выходному выводу. Если число адресных входов равно n, то число информационных входов может быть равно 2n .

Рис. 102.

На рис. 144 приведена схема мультиплексора К561КП2. Это восьмивходовой мультиплексор-демультиплексор. Микросхема имеет три адресных входа 1, 2 и 4, восемь информационных входов Х0-Х7 и вход стробирования S, с помощью которого выход мультиплексора отключается от входов и переходит, в так называемое, третье состояние (верхний и нижний ключи выходного каскада микросхемы находятся в закрытом состоянии). Для получения третьего состояния на вход S необходимо подать лог.1. При подаче на адресные входы 1, 2 и 4 двоичного кода адреса, а на вход S лог. 0 выход мультиплексора соединяется с входом, номер которого равен двоичному коду адреса. В этой микросхеме соединение входов с выходом организуется с помощью двунаправленного ключа на КМОП-транзисторах. Передаваемый через мультиплексор сигнал может быть как аналоговым, так и цифровым, он может передаваться как с входов на выход (режим мультиплексора), так и с выхода распределяться по входам (режим демультиплексора).

Мультиплексор может применяться для опроса различных датчиков цифровых и аналоговых сигналов и передачи этой информации на вход одного приемника (для усиления, преобразования, индикации).

|

|

|

Демультиплексор – это комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько информационных каналов. Согласно определению, демультиплексор в общем случае имеет один информационный вход, n адресных входов и 2n выходов. Демультиплексор может применяться для распределения сигнала, принятого по одному проводу, по различным потребителям.

9.6

Шифраторы, дешифраторы и преобразователи кодов

Шифраторы, дешифраторы и преобразователи кодов

Схемы, предназначенные для преобразования цифровой информации из десятичной системы счисления в двоичную, обычно называются шифрирующими, а для обратного преобразования - дешифрирующими. Схемы, предназначенные для преобразования различных кодов в двоичной системе, называют преобразователями кода. Все эти схемы относятся к узлам комбинационного типа.

Шифраторы. Составление таких схем основано на комбинационной таблице. Здесь показан пример разработки схемы преобразования десятичных цифр 0÷9 в код 8421.

Таблица 13.1 - Комбинационная таблица шифратора

| цифра | Код «1 из 10» | Код 8421 | ||||||||||||

| D | С | B | А | |||||||||||

| о |

Из таблицы (и на рисунке 13.1) видно, что двоичным цифрам 1 в столбике А соответствуют десятичные цифры 1, 3, 5, 7 и 9, т. е. можно написать: А=1 + 3 + 5 + 7+9. Это алгебраическое выражение логического сложения. Точно так же справедливо, что: В = 2 + 3 + 6 + 7; С = 4 + 5 + 6 + 7; D = 8 + 9. На рисунке 13.1 представлен пример реализации схемы на элементах ИЛИ-НЕ. В состоянии покоя на всех входах низкий уровень. Подобным образом можно составить схемы преобразования десятичных цифр в любой код.

|

|

|

в базисе ИЛИ-НЕ

Рисунок 103 - Шифратор цифр 0÷9 в код 8421

Дешифраторы. При разработке различного рода цифровых управляющих устройств часто необходимо решать задачу, когда управляющее воздействие определяется значениями входных сигналов только в данный момент времени и не зависит от их значений в предыдущие моменты времени. Иными словами, выходной сигнал, характеризующий управляющее воздействие, здесь зависит только от наличия соответствующей комбинации сигналов на входах устройства. Примером таких комбинационных схем являются дешифраторы.

Дешифратором называют комбинационную логическую схему, в которой каждой из комбинаций сигналов на входах соответствует сигнал только на одном из его выходов. Они находят применение в управляющих системах для выдачи управляющих воздействий в те или иные цепи в зависимости от комбинации сигналов на входах.

Значения сигналов а, b, с, d на выходах счетчика и требуемые при этом показания дешифратора могут быть использованы для определения элементов схемы дешифратора. Так, при нулевом показании счетчика сигнал «1» присутствует на инверсных выходах его триггеров (см. таблицу 13.2), в связи с чем реализуемая каналом  функция будет:

функция будет:  .

.

Таблица - Состояния дешифратора

| Число входных импульсов | Триггеры счётчика | Выходы дешифратора | ||||||||||||

| Тр4 (d) | Тр3 (с) | Тр2 (b) | Тр1 (а) | x0 | x1 | x2 | x3 | x4 | x5 | x6 | x7 | x8 | x9 | |

| о |

Аналогично для канала  имеем:

имеем:  ; а для канала

; а для канала  :

:  . Логические функции могут быть реализованы с помощью четырехвходовых логических элементов И.

. Логические функции могут быть реализованы с помощью четырехвходовых логических элементов И.

|

|

|

Однако без предварительной минимизации составленные непосредственно из таблицы дешифрируемые функции нецелесообразно использовать для схемной реализации. Это привело бы к заведомому усложнению схемы дешифратора. Табличное выражение дешифрируемой функции для цифры 9 (канала  ) имеет вид

) имеет вид  . Вместе с тем, только для этого канала характерна комбинация выходных сигналов триггеров счетчика, при которой

. Вместе с тем, только для этого канала характерна комбинация выходных сигналов триггеров счетчика, при которой  . В связи с этим для выделения сигнала (логической «1») по каналу цифры 9 можно воспользоваться функцией

. В связи с этим для выделения сигнала (логической «1») по каналу цифры 9 можно воспользоваться функцией  . Иными словами, канал

. Иными словами, канал  можно реализовать не на четырёхвходовом, а на двухвхо-довом логическом элементе И.

можно реализовать не на четырёхвходовом, а на двухвхо-довом логическом элементе И.

Минимизацию функций дешифратора удобно проводить по карте Карно, которая составляется в данном случае для четырех переменных.

Электронная промышленность выпускает дешифраторы в виде интегральных схем, например, в серии 1533 интегральные схемы КР1533ИДЗ, КР1533ИД6. ИХ условное графическое обозначение приведено на рисунке 104.

1533ИД3 1533ИД6

Рисунок 104 - Интегральные схемы дешифраторов серии 1533

Преобразователи кодов. Преобразователем кодов называется логическое устройство, предназначенное для изменения кода информации, передаваемой и обрабатываемой цифровыми устройствами. Существующее множество кодов предназначено для обеспечения удобства перевода чисел из десятичной системы в двоичную, простоты выполнения арифметических операций и контроля результатов вычислений. Выбор кода влияет также на аппаратные затраты реализуемых схем цифровых устройств и на надежность выполнения ими заданных алгоритмов.

|

|

|

Рассмотрим синтез комбинационных преобразователей кодов на примерах преобразования двоично-десятичного кода 8421 в широко применяемый в цифровых устройствах двоично-десятичный код 2421. Алгоритм преобразования двоично-десятичного кода 8421 в код 2421 может быть представлен таблицей истинности (таблица 13.3).

Таблица 13.3 - Таблица истинности преобразователя кода 8421 в код 2421

| Десятичное число | Код | |||||||

| х4 | x3 | x2 | x1 | F4 | F3 | F2 | F1 | |

| б | ||||||||

Счётчики импульсов

Подсчет числа импульсов является наиболее распространенной операцией в устройствах цифровой обработки информации. В устройствах цифровой обработки информации измеряемый параметр (угол поворота, перемещение, скорость, частота, время, температура и т. д.) преобразуется в импульсы напряжения, число которых в соответствующем масштабе характеризует значение данного параметра. Эти импульсы подсчитываются счетчиками импульсов и выражаются в виде цифр.

По целевому назначению счетчики подразделяют на простые и реверсивные. Простые счетчики, в свою очередь, подразделяют на суммирующие и вычитающие. Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т. е. для сложения. С приходом очередного счетного импульса на вход счетчика его показание увеличивается на единицу. Вычитающий счетчик служит для осуществления счета в обратном направлении, т. е. для вычитания. Каждый счетный импульс, поступающий на вход вычитающего счетчика, уменьшает его показание на единицу.

Реверсивные счетчики предназначены для выполнения операции счета как в прямом, так и в обратном направлении, т. е. они могут работать в режиме сложения и вычитания. Основными параметрами счетчиков являются модуль счета (коэффициент счета К) и быстродействие. Коэффициент счета определяет число импульсов, которое может быть сосчитано счетчиком.

Быстродействи е счетчика характеризуется максимальной частотой  следования счетных импульсов и связанным с ней временем

следования счетных импульсов и связанным с ней временем  установки счетчика. Величина

установки счетчика. Величина  определяет максимальное время протекания переходных процессов во всех разрядах счетчика с поступлением на вход очередного счетного импульса. Счетчики импульсов выполняются на основе триггеров. Счет числа поступающих импульсов производится с использованием двоичной системы счисления.

определяет максимальное время протекания переходных процессов во всех разрядах счетчика с поступлением на вход очередного счетного импульса. Счетчики импульсов выполняются на основе триггеров. Счет числа поступающих импульсов производится с использованием двоичной системы счисления.

|

|

|

Двоичные суммирующие счетчики с непосредственной связью: они производят счет поступающих импульсов в двоичной системе счисления. Основным узлом двоичного счетчика (служащим также его разрядом) является триггер со счетным запуском, осуществляющий подсчет импульсов по модулю 2.

Многоразрядные двоичные суммирующие счетчики с непосредственной связью выполняются путем последовательного соединения счетных триггеров. Принцип действия двоичного счетчика с непосредственной связью рассмотрим на примере четырехразрядного счетчика, показанного на рисунке 14.1. Схема выполнена на счетных Т,-триггерах с внутренней задержкой. Работу схемы иллюстрируют временные диаграммы, приведенные на рисунке 105, и таблица 14.1.

Рисунок 105 - Двоичный четырёхразрядный счётчик

По окончании 15-го импульса все разряды счетчика устанавливаются в состояние «1», а 16-й импульс переключает первый разряд счетчика в «0». В соответствии с рисунком 105 и таблицей, установка в исходное состояние «0» двух последовательно включенных триггеров (DD1 и DD2) осуществляется четвертым счетным импульсом, трех триггеров (DD1-DD3) - восьмым и четырех триггеров - 16-м счетным импульсом. Из этого следует, что модуль счета двухразрядного, трехразрядного и четырехразрядного двоичных счетчиков равен соответственно 4, 8 и 16. Модуль счета двоичного счетчика находят из соотношения  , где N - число разрядов счетчика.

, где N - число разрядов счетчика.

В процессе работы двоичного счетчика частота следования импульсов на выходе каждого последующего триггера уменьшается вдвое по сравнению с частотой его входных импульсов. Это свойство схемы используют для построения делителей частоты. При использовании схемы в качестве делителя частоты входной сигнал подают на счетный вход первого триггера, а выходной снимают с последнего триггера.

Выходная и входная частоты связаны соотношением  . Максимальное время установки

. Максимальное время установки  в двоичных счетчиках с непосредственной связью характеризуется суммарной задержкой в последовательной передаче информации от младшего к старшему разряду счетчика. Другими словами, параметр определяется временем перехода счетчика из кода

в двоичных счетчиках с непосредственной связью характеризуется суммарной задержкой в последовательной передаче информации от младшего к старшему разряду счетчика. Другими словами, параметр определяется временем перехода счетчика из кода  в код 00...0. Его находят из соотношения

в код 00...0. Его находят из соотношения  , где

, где  - задержка переключения

- задержка переключения  -триггера после окончания счетного импульса.

-триггера после окончания счетного импульса.

Таблица 14.1 - Состояние триггеров счётчика

| Число импульсов | Триггер 1 | Триггер 2 | Триггер 3 | Триггер 4 |

| I | ||||

Время установки возрастает с увеличением числа разрядов, что сказывается на быстродействии счетчика. Максимальная частота следования счетных импульсов ограничивается величиной:

.

.

При работе счетчика в режиме деления частоты его предельная частота определяется предельной частотой переключения триггера первого разряда:

.

.

Счетчики с коэффициентом счета  .

.

На практике часто возникает необходимость в счетчиках, коэффициент счета которых не соответствует указанному значению  . Такие счетчики выполняются на основе двоичных счетчиков. Общий принцип их построения основывается на исключении у счетчика с

. Такие счетчики выполняются на основе двоичных счетчиков. Общий принцип их построения основывается на исключении у счетчика с  соответствующего числа «избыточных» состояний. Число избыточных состояний s определяется разностью:

соответствующего числа «избыточных» состояний. Число избыточных состояний s определяется разностью:  , где

, где  - количество состояний двоичного счетчика;

- количество состояний двоичного счетчика;  - требуемый коэффициент счета. Число триггеров счётчика выбирают по минимуму величины s. Например, при построении счетчика с

- требуемый коэффициент счета. Число триггеров счётчика выбирают по минимуму величины s. Например, при построении счетчика с  на двух триггерах и счетчика с

на двух триггерах и счетчика с  на четырех триггерах следует исключить соответственно 1 и 6 состояний.

на четырех триггерах следует исключить соответственно 1 и 6 состояний.

Способы построения счетчиков с коэффициентом счета  достаточно разнообразны. Наибольшее распространение получили способ принудительной установки в состояние «0» всех разрядов двоичного счетчика и способ принудительного насчета. По первому способу реализуются счетчики с естественным порядком счета, по второму - счетчики с принудительным счетом.

достаточно разнообразны. Наибольшее распространение получили способ принудительной установки в состояние «0» всех разрядов двоичного счетчика и способ принудительного насчета. По первому способу реализуются счетчики с естественным порядком счета, по второму - счетчики с принудительным счетом.

В счетчиках с естественным порядком счета порядок счета такой же, как в двоичных счетчиках. Отличие заключается в том, что путем введения дополнительных связей счет заканчивается раньше значения  . У счетчика с

. У счетчика с  переход разрядов в состояние «0» будет происходить с приходом не 16-го, а 10-го счетного импульса («Система 16 - 6»).

переход разрядов в состояние «0» будет происходить с приходом не 16-го, а 10-го счетного импульса («Система 16 - 6»).

В счетчиках с принудительным насчетом исключение избыточных состояний двоичного счетчика достигается путем принудительной установки отдельных его разрядов в состояние «1» в процессе счета. Принудительный насчет осуществляется введением обратных связей со старших разрядов двоичного счетчика в младшие, благодаря чему соответствующие младшие разряды вне очереди переключаются в состояние «1».

Вследствие принудительного насчета показания рассматриваемых счетчиков не соответствуют двоичной системе счисления. По этой причине их относят к классу счетчиков с «произвольным» порядком счета. Способ реализации счетчиков с принудительным насчетом показан на примере функциональной схемы счетчика с  (рис.106).

(рис.106).

Рисунок 106 - Функциональная схема декадного счетчика с принудительным насчетом

До записи «1» в четвертый разряд, т. е. до прихода восьмого счетного импульса, счетчик работает как двоичный (таблица 14.2). С приходом восьмого счетного импульса «1» записывается в триггер  с осуществлением обратной связи на запись «1» во вторую и третью ячейки.

с осуществлением обратной связи на запись «1» во вторую и третью ячейки.

Таблица Состояние триггеров счётчика с принудительным счётом

| Число входных импульсов | Т4 | Т3 | Т2 | Т1 |

| ||||

Таким образом, после восьмого счетного импульса вследствие принудительного насчета в счетчик записывается число 8 + 6 = 14. Девятый счетный импульс устанавливает «1» в триггере Т1, а десятый счетный импульс возвращает счетчик в исходное нулевое состояние.

Счетчики с

Счетчики с  называют десятичными, или декадными. Они нашли широкое применение для регистрации числа импульсов с последующим визуальным отображением результата.

называют десятичными, или декадными. Они нашли широкое применение для регистрации числа импульсов с последующим визуальным отображением результата.

Десятичные счетчики часто включают последовательно (рис. 107).

Рис.107 - Последовательное соединение декадных счётчиков

Если в пределах всех декад счет ведется в двоичной системе счисления, то, например, числу 978 будет отвечать код 1001 0111 1000, характеризующий двоично-десятичную систему счисления.

Электронная промышленность выпускает широкую номенклатуру интегральных схем счётчиков. Типичным представителем является счётчик 531ИЕ16 - синхронный, реверсивный, декадный, двоично-десятичный счётчик. Эта ИС позволяет строить счётчики с предустановкой, строить комбинированные схемы счётчиков, управлять их коэффициентом счёта и управлять направлением счёта.

Современными счётчиками КМОП ИС являются микросхемы КР1554ИЕ6, ИЕ7, ИЕ10, ИЕ18 и ИЕ23, имеющие примерное время задержки распространения в диапазоне 9-22 нс. Развитие этой технологии - серии 5514 и 5554. Кроме счётчиков в сериях общего назначения имеются счётчики и в сериях сверхбыстродействующих ИС. Микросхемы серии 6500 (буферизированная полевая логика, материал GaAs) работают на максимальной частоте не менее 1000 МГц и имеют время задержки распространения 1‑2 нс. Так, 6500ИЕ4 - 4-разрядный двоичный счётчик с предустановкой. Напряжения питания ИС этой серии 4 В и минус 2,5 В. Выход - с открытым истоком, сопротивление внешней нагрузки - 50 Ом.

Особо стоит сверхбыстродействующая серия 193, используемая с закрытым входом (с разделительным конденсатором) и имеющая высокую чувствительность, но работающая от конечного значения нижней входной частоты. Так, счётчик К193ИЕ9 с коэффициентом счёта 4 работает на нижней частоте 150 МГц при напряжении 0,6 В и на верхней 1,3 ГГц, а при нескольких милливольтах на частоте 1150 МГц, Счётчик Н193ПЦ5 работает в диапазоне частот 1500-3000 МГц. В этой серии имеются микросхемы для построения сверхвысокочастотных делителей частоты с управляемым коэффициентом деления. У этих ИС есть управляющий вход, изменяющий коэффициент счёта дискретно: так, счётчик 193ИЕ8 имеет управляемый коэффициент счёта 20/22, а микросхема ИЕ2 - коэффициент 10/11

Регистры

Регистрами называют функциональные узлы, предназначенные для приёма, хранения, передачи и преобразования информации. В зависимости от способа записи информации (кода числа) различают параллельные, последовательные и параллельно-последовательные регистры. Параллельные регистры. В параллельных регистрах запись двоичного числа (слова) осуществляется параллельным кодом, т. е. во все разряды регистра одновременно. Их функция сводится только к приёму, хранению и передаче информации (двоичного числа).

Считывание кода из регистра может производиться многократно без разрушения информации. Параллельный N-разрядный регистр состоит из N-триггеров, каждый из которых имеет информационный вход, на которые и подаётся входная информация. Установка выходов регистра в состояния, соответствующие состояниям информационных входов, производится при воздействии импульса синхронизации (тактирующего) на соответствующий управляющий вход. Регистры могут иметь отдельный управляющий вход переустановки выходных состояний в нулевое значение («R», переустановка, обнуление).

При построении параллельных регистров наибольшее применение получили D‑триггеры (триггер-«защёлка»), позволяющие выполнять параллельные регистры на малом количестве элементов. Полупроводниковая элементная база, выпускаемая электронной промышленностью, имеет в своём составе многоразрядные параллельные регистры (рисунок 15.1) или позволяет изготавливать их на интегральных схемах малой степени интеграции.

| Входы | Выходы | ||

| С | D | O |

| I | |||

| X | Q0 | ||

| X | X | Z |

1533ИРЗЗ 8-разрядный параллельный регистр на D-триггерах

Таблица состояний

Рис.108 - Многоразрядный параллельный регистр с Z-состоянием

Такие регистры (например, ИС 1533ИР22, ИРЗЗ, ИР34) могут использоваться в качестве:

- регистра памяти;

- буферного регистра, способного работать на низкоомные нагрузки (20-100 Ом) и большие ёмкости нагрузки (до 50 пФ и более);

- регистра ввода-вывода и магистрального передатчика, что обеспечено

наличием в них режима большого выходного сопротивления («третье состояние», «Z-состояние»), за счёт чего они физически всегда подключены к линиям

шин магистрали микропроцессорной системы через сопротивления порядка не

скольких мегаом. А передача информации происходит только во время действия

управляющего импульса (вход ЕО на рисунке 15.1), когда управляющее устройство выводит регистр из Z-состояния.

Параллельные регистры имеются и в составе серий современных скоростных микромощных ИС (серии 1554, 1594, 5514 и 5554). Параметры таких регистров определяются параметрами D-триггеров, входящих в их состав. Это параметры, которые важно знать и при самостоятельном применении D-триггеров:

- время предустановки tПРУСТ показывает, насколько ранее должен быть подан сигнал на D-вход относительно момента поступления сигнала на на вход С;

- время удержания tУД отражает время удержания сигнала на D-входе после момента прихода сигнала на С-вход.

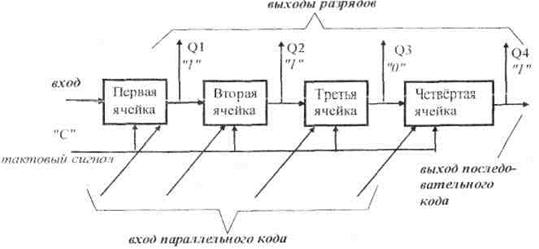

Последовательные регистры (регистры сдвига). Характеризуются записью числа последовательным кодом и, кроме операции хранения, осуществляют преобразование последовательного кода в параллельный, служат в качестве элементов временной задержки, выполняют арифметические и логические операции. Регистр состоит из последовательно соединенных ячеек памяти, состояния которых передаются (сдвигаются) на последующие ячейки под действием тактовых импульсов. Однотактные регистры сдвига выполняют по функциональной схеме (рис.109), показанной для четырех разрядов.

Рис.109 - Последовательный 4-разрядный однотактный регистр

Тактовые импульсы управляют работой регистра. Регистры сдвига могут управляться одной последовательностью тактовых импульсов. В этом случае регистры называют однотактными. Частота следования тактовых импульсов обычно неизменна. В многотактных регистрах последовательности тактовых импульсов следуют с взаимным фазовым сдвигом  , где т - количество последовательностей тактовых импульсов. Наиболее простая реализация регистра сдвига использует последовательное соединение D-триггеров таким образом, чтобы для некоторого n-го разряда выполнялось условие:

, где т - количество последовательностей тактовых импульсов. Наиболее простая реализация регистра сдвига использует последовательное соединение D-триггеров таким образом, чтобы для некоторого n-го разряда выполнялось условие:

;

;  .

.

Первая ячейка регистра относится к его младшему разряду, а четвертая - к старшему. При таком расположении разрядов запись числа в регистр производится начиная со старшего разряда числа. При обратном расположении разрядов в регистре запись числа должна начинаться с его младшего разряда. Тактовые импульсы подаются на все триггеры ячеек одновременно. Их воздействие направлено на переключение триггеров из состояния «1» в состояние «0» с записью единицы в триггер следующей ячейки.

Операция считывания информации из последовательного регистра может быть проведена в параллельном или последовательном коде. Для передачи информации в параллельном коде используют выходы разрядов регистра. Таким образом, последовательный регистр позволяет осуществить операцию преобразования последовательного кода в параллельный. Считывание информации в последовательном коде реализуется подачей серии тактовых импульсов.

В последовательном регистре записанное число может быть сдвинуто тактовыми импульсами на один или несколько (k) разрядов. Операции сдвига соответствуют умножению числа на  . Например, сдвиг кода 0010 числа 2 на один разряд дает код 0100 (число 4), на два разряда - код 1000 (число 8).

. Например, сдвиг кода 0010 числа 2 на один разряд дает код 0100 (число 4), на два разряда - код 1000 (число 8).

При построении модулей памяти на однотактных регистрах сдвига необходимо учитывать, что тактовые импульсы воздействуют на перевод в состояние «0» триггеров всех разрядов одновременно. Поэтому в однотактных регистрах должна быть решена задача разделения во времени (по меньшей мере на длительность тактовых импульсов  ) операций считывания единицы с триггера каждого разряда и ее переписи в триггер следующего разряда. В противном случае перепись единицы в следующий разряд не будет произведена.

) операций считывания единицы с триггера каждого разряда и ее переписи в триггер следующего разряда. В противном случае перепись единицы в следующий разряд не будет произведена.

Эта задача может быть решена включением в цепь передачи сигнала от одной ячейки к другой элемента задержки. Элемент задержки будет задерживать импульс записи единицы в последующую ячейку на время действия тактового импульса. Однако наличие элементов задержки обусловливает критичность работы схемы в отношении длительности тактовых импульсов. Кроме того, для элементов задержки, состоящих из реактивных элементов L и С, затруднено интегральное исполнение. В связи с указанным, разнесение во времени операций считывания и переписи единицы осуществляют схемными средствами, например выполнением ячеек на триггерах с внутренней задержкой ( ,

,  ,

,  -триггерах).

-триггерах).

Параллельно-последовательные и реверсивные регистры. В параллельно-последовательных регистрах сочетаются свойства регистров параллельного и последовательного действия. Они записывают информацию как в последовательном, так и параллельном коде, в связи с чем могут быть использованы для преобразования кодов из последовательного в параллельный и обратно. Эти регистры допускают однотактный (рис.110) и многотактный принципы построения.

Рис.110 - Параллельно-последовательный регистр

Для преобразования последовательного кода в параллельный серией тактовых импульсов в регистр записывается информация (число) последовательного кода. Выходы разрядов регистра при этом представляют ту же информацию в параллельном коде. Для обратного преобразования информация в регистр вводится по входам параллельного кода. Посредством серии тактовых импульсов с выхода последнего разряда регистра информация считывается в последовательном коде.

Реверсивные регистры предназначены для осуществления сдвига кода числа в сторону как старшего, так и младшего разрядов. Регистр содержит связи последовательной передачи информации в направлении от младших разрядов к старшим, а также от старших разрядов к младшим.

Прямой или обратный сдвиг кода осуществляют управляющим сигналом, вводящим в действие либо прямую, либо обратную связи между разрядами.

РАЗДЕЛ 5

Фотоэлектронные приборы

10

отоэлектрические приборы.

отоэлектрические приборы.

|

|

|