|

Разработка управляющих автоматов для процессорных элементов микро ЭВМ.

|

|

|

|

При синтезе управляющего автомата условимся о следующих допущениях – комбинаторный сумматор, использованный при синтезе операционного автомата формирует следующие признаки:

P – знак числа

Число больше нуля – P = “0”

Число меньше нуля – P = “1”

Z – признак нуля

Число равно нулю – Z = “1”

Число не равно нулю – Z = “0”

Для построения управляющего автомата произведем разметку ГСА (Рис. 6).

Рис. 6.1 Схема разметки ГСА.

Рис. 6.2 Схема разметки ГСА.

Рис. 6.3 Схема разметки ГСА.

|

|

|

|

|

|

|

| 000000 |

| 000001 | 1 | - | - |

| 000001 |

| 000010 | 1 |

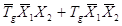

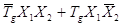

| D5 |

| 000010 |

| 000011 | 1 |

| D5 D6 |

| 000011 |

| 000100 | 1 |

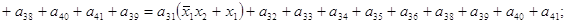

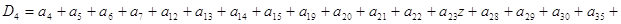

| D4 |

| 000100 |

| 000101 | 1 |

| D4 D6 |

| 000101 |

| 000110 | 1 |

| D4 D5 |

| 000110 |

| 000111 | 1 |

| D4 D5 D6 |

| 000111 |

| 001000 | 1 |

| D3 |

| 001000 |

| 001001 | 1 |

| D3 D6 |

| 001001 |

| 001010 | 1 |

| D3 D5 |

| 001010 |

| 001011 | 1 |

| D3 D5 D6 |

| 001011 |

| 001100 | 1 |

| D3 D4 |

|

| 001100 |

| 001101 |

|

| D3 D4 D6 |

| 001110 |

| D3 D4 D5 | |||

| 001101 |

| 001111 | 1 |

| D3 D4 D5 D6 |

| 001110 |

| 001111 | 1 |

| D3 D4 D5 D6 |

| 001111 |

| 010000 | 1 |

| D2 |

| 010000 |

| 010001 | 1 |

| D2 D6 |

|

| 010001 |

| 010011 |

|

| D2 D5 D6 |

| 010010 |

| D2 D5 | |||

| 010010 |

| 010100 | 1 |

| D2 D4 |

| 010011 |

| 010101 | 1 |

| D2 D4 D6 |

| 010100 |

| 010110 | 1 |

| D2 D4 D5 |

| 010101 |

| 010110 | 1 |

| D2 D4 D5 D6 |

|

| 010110 |

| 010111 |

|

| D2 |

| 010000 |

| ||||

| 010111 |

| 011000 | 1 |

| D2 D3 |

| 011000 |

| 011001 | 1 |

| D2 D3 D6 |

| 011001 |

| 011010 | 1 |

| D2 D3 D5 D6 |

| 011010 |

| 011011 | 1 |

| D2 D3 D4 |

| 011011 |

| 011100 | 1 |

| D2 D3 D4 D6 |

| 011100 |

| 011101 | 1 |

| D2 D3 D4 D5 |

| 011101 |

| 011110 | 1 |

| D2 D3 D4 D5 D6 |

|

| 011110 |

| 011111 |

|

| D1 |

| 100000 |

| D1 D6 | |||

| 100001 |

| D1 D5 D6 | |||

| 100011 |

| D1 D5 | |||

| 100010 |

| D1 D5 | |||

| 011111 |

| 100010 | 1 |

| D1 D5 |

| 100000 |

| 100010 | 1 |

| D1 D5 |

| 100001 |

| 100011 | 1 |

| D1 D5 D6 |

| 100010 |

| 100110 | 1 |

| D1 D4 D5 |

| 100011 |

| 100110 | 1 |

| D1 D4 D5 |

| 100100 |

| 011110 | 1 |

| D2 D3 D4 D5 |

| 100101 |

| 100100 | 1 |

| D1 D4 |

|

| 100110 |

| 100101 |

|

| D1 D4 D6 |

| 100111 |

| D1 D4 D5 D6 | |||

| 100111 |

| 101000 | 1 |

| D1 D3 |

| 101000 |

| 101001 | 1 |

| D1 D3 D6 |

|

| 101001 |

| 000000 |

|

| - |

| 001000 |

| D3 |

Обобщая полученные данные можно построить общую схему управляющего автомата (Рис. 7).

|

|

|

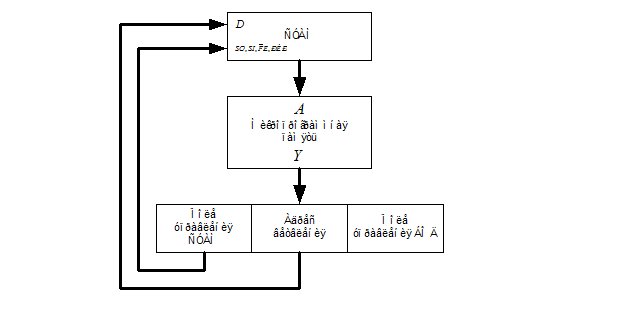

Рис. 7. Общая схема управляющего автомата.

Рис. 7. Общая схема управляющего автомата.

Разработка структурной схемы микро ЭВМ.

Эмуляция ОА в микропроцессорной среде с разрядно-модульной организацией.

Для достижения требуемой разрядности при использовании микропроцессорной секции К1804ВС1 необходимо объединить между собой шесть микропроцессорных секций. Функциональная схема объединения МПС приведена на рис. 8.

При эмуляции ОА в микропроцессорной среде будем использовать следующие соглашения:

| Номер РОН | Регистр в ОА |

| 1 | Рг.I |

| 2 | Рг.T |

| 3 | Рг.К |

| 4 | Рг.Х |

| 5 | Рг.Р |

| 6 | Рг.Чт. |

| 7 | Рг.Дт. |

| 8 | Рг.Сч. |

| 9 | Рг.Мн. |

| 10 | Рг.Мт. |

| 11 | Рг.LN |

| 12 | Рг.DM |

| 13 | Рг.СМ. |

Рис.8 Функциональная схема объединения МПС.

Сигналы, поступающие на МПС:

А(4 разр.), В(4), I(9), D(24),  (1)

(1)

Для реализации микроопераций ОА необходимо подать на МПС следующие наборы сигналов (в соответствии с форматом):

: :

| 0000 | 0001 | 010 | 000111 | 00..00 | 1 |

: :

| 0000 | 0010 | 010 | 000111 | 00..00 | 0 |

: :

| 0000 | 1011 | 010 | 000111 | 00..00 | 0 |

: :

| 0000 | 0011 | 010 | 000111 | 00..00 | 0 |

: :

| 0000 | 0100 | 010 | 000111 | X | 0 |

: :

| 0100 | 0100 | 010 | 001100 | 00..00 | 0 |

: :

| 0100 | 0101 | 010 | 000100 | 00..00 | 0 |

: :

| 0000 | 0110 | 010 | 000111 | 00..00 | 0 |

: :

| 0001 | 0111 | 010 | 000100 | 00..00 | 0 |

: :

| 0100 | 1100 | 010 | 000100 | 00..00 | 0 |

: :

| 0000 | 1000 | 010 | 000111 | 00..0010111 | 0 |

: :

| 0111 | 1100 | 010 | 001001 | 00..00 | 1 |

: :

| 0000 | 1110 | 010 | 000111 | 00..00 | 1 |

: :

| 0000 | 1110 | 010 | 000111 | 00..00 | 0 |

: :

| 0111 | 1100 | 011 | 000001 | 00..00 | 0 |

: :

| 0000 | 1100 | 110 | 000011 | 00..00 | 0 |

: :

| 0000 | 0110 | 110 | 000011 | 00..00 | 0 |

: :

| 0000 | 0110 | 010 | 000011 | 00..00 | 1 |

: :

| 0000 | 1000 | 010 | 001011 | 00..00 | 0 |

: :

| 0110 | 0010 | 010 | 000100 | 00..00 | 0 |

: :

| 0010 | 1011 | 010 | 000001 | 00..00 | 0 |

: :

| 0000 | 0001 | 010 | 000011 | 00..00 | 1 |

: :

| 0000 | 1101 | 010 | 000111 | 00..00 | 0 |

: :

| 0100 | 1001 | 010 | 000100 | 00..00 | 0 |

: :

| 0101 | 1010 | 010 | 000100 | 00..00 | 0 |

: :

| 0000 | 1000 | 010 | 000111 | 00..01101 | 0 |

: :

| 0000 | 1111 | 010 | 000111 | 00..00 | 0 |

: :

| 1001 | 1101 | 010 | 000001 | 00..00 | 0 |

: :

| 1001 | 0000 | 110 | 000100 | 00..00 | 0 |

| 0000 | 1101 | 010 | 000001 | 00..00 | 0 | |

: :

| 1001 | 1101 | 010 | 001001 | 00..00 | 1 |

: :

| 0000 | 1111 | 010 | 000111 | 00..00 | 1 |

: :

| 0000 | 1010 | 100 | 000011 | 00..00 | 0 |

| 0000 | 1010 | 100 | 000011 | 00..00 | 0 | |

: :

| 0000 | 1001 | 110 | 000001 | 00..00 | 0 |

: :

| 1101 | 0100 | 010 | 000100 | 00..00 | 0 |

: :

| 0000 | 0100 | 010 | 010011 | 00..00 | 1 |

: :

| 0000 | 0011 | 010 | 001011 | 00..00 | 0 |

Эмуляция УА в микропроцессорной СУАМ.

|

|

|

В микро ЭВМ функции управляющего автомата реализует блок микропроцессорного управления. Структурная схема БМУ представлена на рис. 9.

Рис. 9. Структурная схема БМУ.

Рис. 9. Структурная схема БМУ.

Принципом организации корректного функционирования микро ЭВМ является факт того, что при выполнении определенных команд, выполняется некоторая совокупность микроопераций в тело которым выходит весь набор управляющих сигналов для выполнения определенных действий.

Таким образом, для каждой команды (микрооперации) существует некоторый набор микроопераций, содержащих в своем теле все необходимые управляющие сигналы, последовательное выполнение которых приводит к выполнению команды в целом.

Данная система реализации команд получила название принципа микропрограммной реализации команд и достаточно широко используется при реализации конкретных вычислительных устройств благодаря своей гибкости и производительности.

Проектирование УУ микро ЭВМ.

|

|

|