|

Делитель частоты импульсов на 5 (на JK -триггерах)

|

|

|

|

Содержание

1. Делитель частоты импульсов на 5 (на JK-триггерах)

2. Синхронный недвоичный счетчик (на JK-триггерах)

3. Сдвигающий регистр (на D-триггерах)

4. Скремблер. Дескремблер

5. Генератор псевдослучайной последовательности

Литература

Делитель частоты импульсов на 5 (на JK -триггерах)

Делитель импульсов должен функционировать так, чтобы на его выходе формировался положительный импульс после поступления на вход каждого пятого импульса. Длительность выходных импульсов должна равняться длительности входных.

Проектируемое устройство описывается графом рис.1,а и имеет пять состояний. Кодировка состояний делителя значениями внутренних переменных производится таким образом, чтобы все они различались между собой представлением хотя бы одной переменной. Так как делитель имеет 5 состояний, то для их кодировки требуется

Проектируемое устройство описывается графом рис.1,а и имеет пять состояний. Кодировка состояний делителя значениями внутренних переменных производится таким образом, чтобы все они различались между собой представлением хотя бы одной переменной. Так как делитель имеет 5 состояний, то для их кодировки требуется  внутренних переменных, т.е.

внутренних переменных, т.е.  элементов памяти (триггеров). Варианты кодировки состояний могут быть различными. В данном случае с целью упрощения комбинационной схемы КС2 целесообразно закодировать одну из внутренних переменных (Q2) так, чтобы она принимала единичные значения в течение одного такта после каждого пятого импульса на входе (рис.1,б).

элементов памяти (триггеров). Варианты кодировки состояний могут быть различными. В данном случае с целью упрощения комбинационной схемы КС2 целесообразно закодировать одну из внутренних переменных (Q2) так, чтобы она принимала единичные значения в течение одного такта после каждого пятого импульса на входе (рис.1,б).

|

Такой вариант кодировки состояний делителя приведен в таблице на рис.2, где даны значения внутренних переменных ( ) для каждого из состояний, а также для последующего состояния (

) для каждого из состояний, а также для последующего состояния ( ), в которое переходит устройство после поступления входного импульса. Приведенная на рис.2 таблица состояний соответствует графу рис.1,б.

), в которое переходит устройство после поступления входного импульса. Приведенная на рис.2 таблица состояний соответствует графу рис.1,б.

После кодировки закон функционирования каждого элемента памяти (триггера) становится заданным, поэтому дальнейшее структурное проектирование сводится к проектированию комбинационной схемы КС1 (рис.21). Проектирование КС1 можно выполнить с помощью словарного метода.

После кодировки закон функционирования каждого элемента памяти (триггера) становится заданным, поэтому дальнейшее структурное проектирование сводится к проектированию комбинационной схемы КС1 (рис.21). Проектирование КС1 можно выполнить с помощью словарного метода.

|

|

|

В соответствии с этим методом получаем для каждого состояния функции переходов  для каждого элемента памяти. В качестве элементов памяти выберем JK-триггеры (рис.22,д), так как его словарь переходов (рис.1) содержит неопределенные требования к значениям информационных сигналов J и K в половине позиций, что существенно снижает сложность КС1 при ее реализации.

для каждого элемента памяти. В качестве элементов памяти выберем JK-триггеры (рис.22,д), так как его словарь переходов (рис.1) содержит неопределенные требования к значениям информационных сигналов J и K в половине позиций, что существенно снижает сложность КС1 при ее реализации.

Далее для полученных функций переходов с использованием словаря переходов JK-триггера получаем текущие значения логических функций управления информационными входами  и

и  , аргументами которых являются переменные

, аргументами которых являются переменные  , задающие код текущего состояния делителя. Таким образом, КС1 должна реализовать систему логических функций

, задающие код текущего состояния делителя. Таким образом, КС1 должна реализовать систему логических функций  ,

,  от переменных

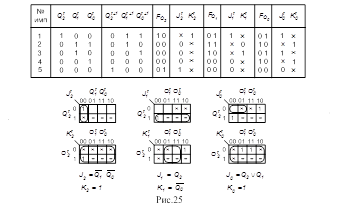

от переменных  . Минимизация этих функций с помощью карт Карно (в клетки карт для отсутствующих комбинаций переменных

. Минимизация этих функций с помощью карт Карно (в клетки карт для отсутствующих комбинаций переменных  поставлен знак факультативности –) приводит к простым структурным формулам (рис.2), позволяющим реализовать КС1.

поставлен знак факультативности –) приводит к простым структурным формулам (рис.2), позволяющим реализовать КС1.

Функции  ,

,  реализуются путем соединения входов триггеров с соответствующими выходами и источником единичного сигнала, а для реализации функции J0 требуется дополнительный двухвходовый ЛЭ ИЛИ. Неиспользуемые (избыточные) входы J и K триггеров оставлены неподключенными, реальные ИС это допускают (неиспользуемый вход в таких ИС работает как вход с пассивным уровнем сигнала).

реализуются путем соединения входов триггеров с соответствующими выходами и источником единичного сигнала, а для реализации функции J0 требуется дополнительный двухвходовый ЛЭ ИЛИ. Неиспользуемые (избыточные) входы J и K триггеров оставлены неподключенными, реальные ИС это допускают (неиспользуемый вход в таких ИС работает как вход с пассивным уровнем сигнала).

Полученная структурная схема делителя показана на рис.3,а. Анализ схемы дает временные диаграммы (рис.3,б), иллюстрирующие ее работу (на временных диаграммах  не показана задержка сигналов относительно входных импульсов

не показана задержка сигналов относительно входных импульсов  ).

).

Для получения на выходе делителя импульсов с длительностью, равной длительности входных импульсов, служит комбинационная схема КС2, реализующая логическую функцию  (логическая схема И).

(логическая схема И).

|

|

|

|

|

|