|

Элементы последовательной логики.

|

|

|

|

Раздел алгебры логики, описывающий работу цифровых автоматов, обладающих памятью, называется последовательной логикой.

Основной элемент последовательной логики – триггер. Триггер имеет два выхода: прямой Q и инверсный Q. Число входов зависит от выполняемых функций. По способу записи информации триггеры делятся на асинхронные и синхронизируемые (тактируемые).

Основной элемент последовательной логики – триггер. Триггер имеет два выхода: прямой Q и инверсный Q. Число входов зависит от выполняемых функций. По способу записи информации триггеры делятся на асинхронные и синхронизируемые (тактируемые).

1. В асинхронных информация может изменяться в любой момент времени при изменении входных сигналов.

2. В синхронизируемых информация на выходе может меняться только в определённые моменты времени, задаваемые дополнительным синхронизирующим сигналом.

Асинхронный RS триггер.

Он может быть построен на двух логических элементах ИЛИ-НЕ, либо И-НЕ. Элементы охвачены цепями ОС, для чего выход каждого элемента подключен к одному из входов другого элемента.

Триггер имеет два входа: S (set) – вход установки в единичное состояние;

R (reset) – вход сброса в нулевое состояние.

|

При S = 1 и R = 0 на выходах будет:

|  |  |  |  | |||||

Q = S + Q = 1 + Q = 1 = 0

запись 1

запись 1

Q = R + Q = 0 + Q = 0 + 0 = 0 = 1

Q = R + Q = 0 + Q = 0 + 0 = 0 = 1

При S = 0 и R = 1 имеем:

| |||||

|  | ||||

Q = R + Q = 1 + Q = 1 = 0

Q = R + Q = 1 + Q = 1 = 0

запись 0

запись 0

Q = S + Q = 0 + Q = 1

После исчезновения входных сигналов, т.е. при S = R = 0 (хранение) сохраняется выходной сигнал 1 или 0, в зависимости от того, на каком из входов (S или R) была перед этим единица 1.

S = R = 1 - запретная комбинация.

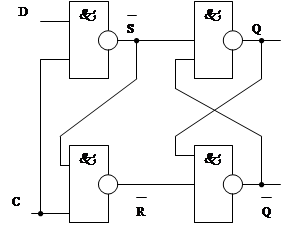

RS – триггер на элементах И-НЕ.

RS – триггер на элементах И-НЕ.

|

При S = 1 и R = 0 на выходах будет:

При S = 1 и R = 0 на выходах будет:

|  |  | ||||

|

Q = R . Q = 0 . Q = 0 = 1

Q = R . Q = 0 . Q = 0 = 1

запись 0

запись 0

|

|

|

Q = S . Q = 1 . 1 = 1 = 0

|  |

При S = 0 и R = 1 на выходах будет:

|  | |||||||||

| ||||||||||

|  |  |

Q = S . Q = 0 . Q = 0 = 1

Q = S . Q = 0 . Q = 0 = 1

запись 1

запись 1

Q = R . Q = 1 . 1 = 1 = 0

Q = R . Q = 1 . 1 = 1 = 0

Запретная комбинация R = S = 0.

Запретная комбинация R = S = 0.

Недостатки RS – триггеров:

1. Наличие запрещённой комбинации входных сигналов.

2. Подача информации по двум отдельным цепям R и S.

3. Низкая помехоустойчивость.

Синхронный D – триггер (статический).

Он образован из RS – триггера и входной комбинационной схемы на двух ЛЭ.

|

D – информационный вход, сюда поступают сигналы, которые необходимо записать в триггер;

С – вход синхронизации, который определяет, в какой момент будет происходить запись информации.

С С

| D | S = C . D | R = C . S | Q = R . Q | Q = S . Q | Режим работы |

0 0

| 0 . 0 = 1 | 0 . 1 = 0 = 1 | 1 .? | 1 .? | Хранение предыдущей информации | |

0 0

| 0 . 1 = 1 | 0 . 1 = 1 | ? | ? | Хранение | |

1 1

| 1 . 0 = 1 | 1 . 1 = 0 | 0 .? = 1 | 1 . 1 = 0 | Запись “0” | |

1 1

| 1 . 1 = 0 | 1 . 0 = 1 | 1 . 1 = 0 | 0 .? = 1 | Запись “1” |

Рассмотренный триггер называется статическим синхронным D-триггером.

D-триггер, как видно из таблицы, находится в режиме хранения при C=0 и в режиме записи при C=1.

D – delay – задержка. Этот триггер задерживает выходной сигнал до окончания того такта, в который он был записан.

Динамический D – триггер (синхронный).

В

динамическим управлением информация записывается только в момент перепада напряжения на входе синхронизации.

|  |  |  | ||||||

|

X1 = X3 . X2; Х2 = Х4 . D; Х3 = S = X1 . C; Х4 = Х2 . Х3 . С

|  |

Пока сигнал С = 0 Х3 = Х4 = 1 (S = R = 1), поэтому согласно таблице истинности это соответствует режиму хранения триггером информации, а сигналы на выходах D1 и D2 соответствуют входному информационному сигналу.

| |||||||

|  |  |

|

|

|

Х2 = D . 1 = D и X1 = D . 1 = D

Так как сигналы Х2 и Х1 инверсны по отношению друг к другу, то при С = 1 только один из них разрешает прохождение синхроимпульса через D3 или D4.

| |||||

|  | ||||

С = 1 D = 1: S = X3 = C . X1 = C . D = 1 . 1 = 0

С = 1 D = 1: S = X3 = C . X1 = C . D = 1 . 1 = 0

|

R = X4 = X2 . C . X3 = D . C . S = 0 . 1 . 0 = 1

R = X4 = X2 . C . X3 = D . C . S = 0 . 1 . 0 = 1

|

C = 1 D = 0: S = X3 = C . X1 = C . D = 1 . 0 = 1

C = 1 D = 0: S = X3 = C . X1 = C . D = 1 . 0 = 1

|  |

R = X4 = X2 . C . X3 = D . C . S = 0 . 1 . 1 = 0

R = X4 = X2 . C . X3 = D . C . S = 0 . 1 . 1 = 0

|

|

|

Динамический D-триггер состоит из трёх статических RS-триггеров. D1, D3 и D2, D4 производят подготовку информации. D5, D6 – записывают предварительно логически обработанную первыми двумя триггерами информацию.

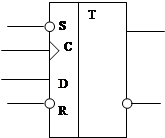

Универсальный D – триггер.

Универсальный D – триггер получается небольшим усложнением предыдущей схемы. Вместо двухвходовых схем И-НЕ используют трёхвходовые.

|

|

|