|

Реализация последовательного умножающего устройства

|

|

|

|

Цель работы

Исследование общих методов и схемотехнических решений реализации операционных устройств, осуществляющих операции умножения чисел в двоичных кодах, а также особенностей множительных устройств на СБИС ПЛ фирмы Altera.

Реализация последовательного умножающего устройства

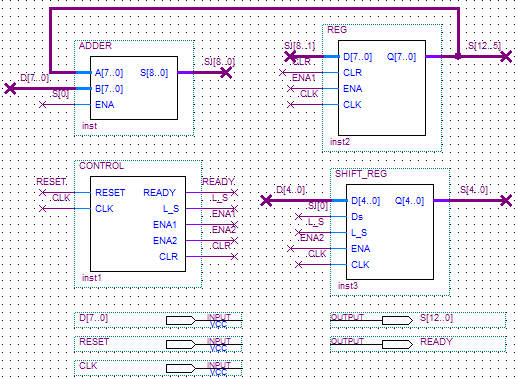

На рис. 1. представлена схема последовательного умножающего устройства с разрядностью операндов, заданной в индивидуальном задании:

Таблица 1. Данные для индивидуального задания

| Номер варианта | Разр. A | Разр. B | Код A | Код B | Код S | Порт A | Порт B |

| прям | обр | доп | пар | посл |

Рис. 1. Структурная схема последовательного умножающего устройства

Умножитель состоит из:

1) комбинационного сумматора “adder”, который в зависимости от сигнала S0, соответствующего анализируемому разряду bi, осуществляет либо сложение данных на входных портах, либо передачу на выход данных с порта A[7..0];

2) регистров “REG” и “SHIFT_REG”, в которых накапливается сумма частичных произведений (в “ SHIFT_REG ”, кроме того, при начальной установке хранится операнд В);

3) управляющего устройства “CONTROL”, осуществляющего выдачу необходимых управляющих сигналов на перечисленные операционные узлы. При подаче сигнала RESET регистр REG устанавливается в 0, а в регистр SHIFT_REG с шины D[4..0] загружается операнд В. После окончания начальной установки на шине D[7..0] устанавливается операнд А и начинается накопление произведения, которое завершается через 8 тактов. Когда произведение получено, устанавливается сигнал READY.

Все блоки последовательного умножающего устройства были описаны на языке VHDL:

Блок REG:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY REG IS

|

|

|

PORT(

D: IN STD_LOGIC_VECTOR (7 downto 0);

CLR, ENA, CLK: IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR (7 downto 0)

);

END REG;

ARCHITECTURE RTL OF REG IS

BEGIN

PROCESS(CLK, CLR)

BEGIN

IF CLR = '1' THEN

Q <= (OTHERS => '0');

ELSE

IF CLK'event and CLK = '1' THEN

IF ENA = '1' THEN

Q <= D;

ELSE null;

END IF;

END IF;

END IF;

END PROCESS;

END RTL;

Блок SHIFT_REG:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY SHIFT_REG IS

PORT(

D: IN STD_LOGIC_VECTOR (4 downto 0);

Ds, L_S, ENA, CLK: IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR (4 downto 0)

);

END SHIFT_REG;

ARCHITECTURE RTL OF SHIFT_REG IS

SIGNAL rg_sh: STD_LOGIC_VECTOR (4 downto 0);

BEGIN

Q <= rg_sh;

PROCESS(CLK)

BEGIN

IF CLK'event and CLK = '1' THEN

IF ENA = '1' THEN

IF L_S = '1' THEN

rg_sh <= D;

ELSE

rg_sh <= Ds&rg_sh(4 downto 1);

END IF;

ELSE null;

END IF;

END IF;

END PROCESS;

END RTL;

Блок ADDER:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_unsigned.all;

ENTITY ADDER IS

PORT(

A, B: IN STD_LOGIC_VECTOR (7 downto 0);

ENA: IN STD_LOGIC;

S: OUT STD_LOGIC_VECTOR (8 downto 0)

);

END ADDER;

ARCHITECTURE RTL OF ADDER IS

BEGIN

PROCESS(ENA, A, B)

BEGIN

IF ENA = '1' THEN

S <= ('0'&A)+('0'&B);

ELSE S <= '0'&A;

END IF;

END PROCESS;

END RTL;

Блок CONTROL:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY CONTROL IS

PORT(

RESET, CLK: IN STD_LOGIC;

READY, L_S, ENA1, ENA2, CLR: OUT STD_LOGIC

);

END CONTROL;

ARCHITECTURE RTL OF CONTROL IS

SIGNAL timer: INTEGER RANGE 0 to 6;

SIGNAL time_ready:INTEGER RANGE 0 to 1;

SIGNAL time_ena2:INTEGER RANGE 0 to 1:=0;

BEGIN

PROCESS(CLK, RESET)

BEGIN

IF CLK'event and CLK = '1' THEN

IF RESET = '1' THEN

L_S <= '1';

CLR <= '1';

ENA1 <= '0';

timer <= 0;

time_ready <= 0;

READY <= '0';

time_ena2 <= time_ena2+1;

IF time_ena2 < 1 THEN

ENA2 <= '1';

ELSE

ENA2 <= '0';

time_ena2 <= 1;

END IF;

ELSE

timer <= timer+1;

IF timer < 5 THEN

ENA1 <= '1';

ENA2 <= '1';

CLR <= '0';

L_S <= '0';

READY <= '0';

time_ready <= 0;

ELSE

time_ready <= time_ready+1;

timer <= 6;

ENA1 <= '0';

ENA2 <= '0';

L_S <= '0';

CLR <= '0';

IF time_ready < 1 THEN

READY <= '1';

time_ena2 <= 0;

ELSE

READY <= '0';

time_ready <=1;

END IF;

END IF;

END IF;

END IF;

END PROCESS;

END RTL;

Далее была выполнена компиляция проекта, в результате которой были получены аппаратурные затраты и временные характеристики синтезированного устройства.

На рис. 2. представлены аппаратурные затраты.

Рис. 2. Аппаратурные затраты

На рис. 3. представлены временные характеристики последовательного умножающего устройства.

Рис. 3. Временные характеристики

|

|

|

На рис. 4 представлен критический путь, ограничивающий тактовую частоту работы устройства.

Рис. 4. Критический путь

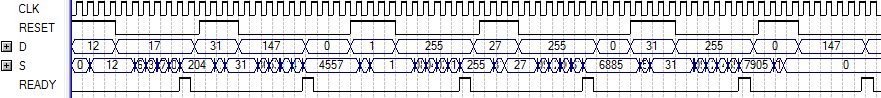

Ниже на рис. 5 приведены результаты тестирования последовательного умножающего устройства.

Рис. 5. Результат тестирования последовательного умножающего устройства

Как видно результат на выходе устройства верный.

|

|

|