|

Приложение 2. Модифицированное последовательное умножающее устройство.

|

|

|

|

Блок REG:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY REG IS

PORT(

D: IN STD_LOGIC_VECTOR (3 downto 0);

CLR, ENA, CLK: IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR (3 downto 0)

);

END REG;

ARCHITECTURE RTL OF REG IS

BEGIN

PROCESS(CLK, CLR)

BEGIN

IF CLR = '1' THEN

Q <= (OTHERS => '0');

ELSE

IF CLK'event and CLK = '0' THEN

IF ENA = '1' THEN

Q <= D;

ELSE null;

END IF;

END IF;

END IF;

END PROCESS;

END RTL;

Блок SHIFT_REG:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY SHIFT_REG IS

PORT(

D: IN STD_LOGIC_VECTOR (7 downto 0);

Ds, L_S, ENA, CLK: IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR (7 downto 0)

);

END SHIFT_REG;

ARCHITECTURE RTL OF SHIFT_REG IS

SIGNAL rg_sh: STD_LOGIC_VECTOR (7 downto 0);

BEGIN

Q <= rg_sh(7 downto 0);

PROCESS(CLK)

BEGIN

IF CLK'event and CLK = '0' THEN

IF ENA = '1' THEN

IF L_S = '1' THEN

rg_sh <= D;

ELSE

rg_sh(7) <= rg_sh(7);

rg_sh(6 downto 0) <= Ds&rg_sh(6 downto 1);

END IF;

ELSE null;

END IF;

END IF;

END PROCESS;

END RTL;

Блок ADDER:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_unsigned.all;

ENTITY ADDER IS

PORT(

A: IN STD_LOGIC_VECTOR (3 downto 0);

B, sign, ENA, ENA_MUL, L_M, CLK: IN STD_LOGIC;

S: OUT STD_LOGIC_VECTOR (4 downto 0);

sign_out:OUT STD_LOGIC

);

END ADDER;

ARCHITECTURE RTL OF ADDER IS

SIGNAL B_VECTOR: STD_LOGIC_VECTOR (4 downto 0);

SIGNAL time_sign: INTEGER RANGE 0 to 1:= 0;

SIGNAL sig: STD_LOGIC;

BEGIN

-- инициализация счетчика, выделяющего знаковый разряд

PROCESS(CLK)

BEGIN

IF CLK'event and CLK = '1' THEN

IF ENA = '1' THEN

IF time_sign < 1 THEN

time_sign <= time_sign + 1;

ELSE

time_sign <= time_sign;

END IF;

ELSE

time_sign <= 0;

END IF;

END IF;

END PROCESS;

PROCESS(CLK)

BEGIN

IF CLK'event and CLK = '1' THEN

IF ENA = '1' THEN

IF time_sign < 1 THEN

sig <= sign;

ELSE null;

END IF;

IF L_M = '1' THEN

B_VECTOR <= B&B_VECTOR (4 downto 1);

ELSE

IF (sig = '1' and B_VECTOR (4) = '0') or (sig = '0' and B_VECTOR (4) = '1') THEN

sign_out <= '1';

ELSE

sign_out <= '0';

END IF;

IF ENA_MUL = '1' THEN

IF B_VECTOR (4) = '1' THEN

S <= ('0'&A)+('0'&(B_VECTOR(3 downto 0) xor "1111"));

ELSE

S<= ('0'&A)+('0'&B_VECTOR(3 downto 0));

END IF;

ELSE

S <= ('0'&A);

END IF;

END IF;

ELSE null;

END IF;

END IF;

END PROCESS;

END RTL;

Блок CONTROL:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY CONTROL IS

PORT(

RESET, CLK: IN STD_LOGIC;

READY, L_S, L_M, ENA, ENA1, ENA2, CLR: OUT STD_LOGIC

);

END CONTROL;

ARCHITECTURE RTL OF CONTROL IS

SIGNAL timer_load: INTEGER RANGE 0 to 6:= 0;

SIGNAL timer_mult: INTEGER RANGE 0 to 8:= 0;

|

|

|

SIGNAL start: STD_LOGIC;

BEGIN

-- определение работы счетчиков

PROCESS(CLK)

BEGIN

IF CLK'event and CLK = '1' THEN

IF start = '1' THEN

IF timer_load < 6 THEN

timer_load <= timer_load + 1;

ELSE

timer_load <= timer_load;

IF timer_mult < 8 THEN

timer_mult <= timer_mult +1;

ELSE

timer_mult <= timer_mult;

END IF;

END IF;

ELSE

timer_load <= 0;

timer_mult <= 0;

END IF;

END IF;

END PROCESS;

-- определение управляющих сигналов

PROCESS(RESET, timer_mult)

BEGIN

IF RESET'event and RESET = '1' THEN

start <= '1';

else null;

END IF;

IF timer_mult = 8 THEN

start <= '0';

ELSE null;

END IF;

END PROCESS;

PROCESS(CLK)

BEGIN

IF CLK'event and CLK = '1' THEN

IF start = '1' THEN

IF timer_load < 6 THEN

CLR <= '1';

IF timer_load < 5 THEN

L_M <= '1';

ELSE

L_M <= '0';

END IF;

IF timer_load = 0 THEN

ENA2 <= '1';

L_S <= '1';

ELSIF timer_load = 1 THEN

ENA2 <= '0';

L_S <= '0';

ELSE null;

END IF;

ELSE

L_M <= '0';

CLR <= '0';

END IF;

IF timer_mult < 7 THEN

IF timer_load = 6 THEN

ENA1 <= '1';

ENA2 <= '1';

END IF;

IF timer_mult < 6 THEN

ENA <= '1';

ELSE

ENA <= '0';

END IF;

ELSE

ENA1 <= '0';

ENA2 <= '0';

READY <= '1';

END IF;

ELSE

READY <= '0';

END IF;

END IF;

END PROCESS;

END RTL;

Блок CORRECTION:

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_unsigned.all;

ENTITY CORRECTION IS

PORT(

D_IN: IN STD_LOGIC_VECTOR (11 downto 0);

D_OUT: OUT STD_LOGIC_VECTOR (11 downto 0)

);

END CORRECTION;

ARCHITECTURE RTL OF CORRECTION IS

BEGIN

PROCESS(D_IN)

BEGIN

IF D_IN (11) = '1' THEN

D_OUT <= (D_IN(11)&(D_IN(10 downto 0) xor "11111111111") + 1);

ELSE

D_OUT <= D_IN;

END IF;

END PROCESS;

END RTL;

На рис. 6. представлена схема модифицированного последовательного умножающего устройства.

Рис. 6. Структурная схема модифицированного последовательного умножающего устройства

Принцип работы данного устройства:

1) При подаче сигнала начальной установки RESET управляющий блок CONTROL формирует на 1 такт сигналы разрешения работы ENA2 и L_S = 1 (режим загрузки) для регистра SHIFT_REG, тем самым в этот регистр загружается параллельный прямой код А[7..0] (8-разрядный операнд А) в течении одного такта;

2) Параллельно с этим на 5 тактов формируется сигнал L_M = 1 (режим загрузки) а также сигнал разрешения работы ENA для блока ADDER, тем самым за пять тактов последовательно (младшими разрядами вперёд) загружается обратный код В (5-разрядный операнд В).

|

|

|

3) Помимо этого, для правильной работы изначально очищается с помощью асинхронного сигнала CLR регистр REG, хранящий частичные суммы.

4) После того, как были загружены оба операнда, управляющий блок CONTROL переводит блок ADDER в режим умножения L_M = 0, а также разрешает работу регистра REG для приема частичных сумм и переводит регистр SHIFT_REG в режим сдвигающего регистра (L_S = 0), для того чтобы выдвигать и анализировать биты операнда А.

5) Во время умножения на вход sign блока ADDER подаётся знаковый разряд операнда А, который, анализируясь вместе со знаковым разрядом операнда В,формирует знак результата S[11] (0 - результат положителен, 1 – результат отрицателен). Помимо этого, если операнд В оказывается отрицательным числом, тогда обратный код, в котором записан операнд В, преобразуется в прямой код, иначе остаётся без изменений, т.к. обратный код положительного числа является прямым кодом. Таким образом, при формировании частичных сумм, блок ADDER оперирует с прямыми кодами операндов, поэтому результат умножения тоже представлен в прямом коде.

6) Т.к. результат умножения представлен в прямом коде, а необходим доп. код, поэтому в устройстве используется блок коррекции результата CORRECTION. Если знаковый разряд выходного результата равен 0, то результат положителен, тогда код не изменяется, т.к. прямой код положительного числа является также и доп. кодом. В противном случае выходной код преобразуется в доп. код.

7) После того, как результат сформирован, на 1 такт появляется сигнал готовности READY.

Далее была выполнена компиляция проекта, в результате которой были получены аппаратурные затраты и временные характеристики синтезированного устройства.

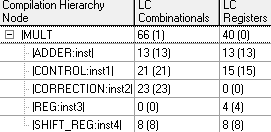

На рис. 7. представлены аппаратурные затраты.

Рис. 7. Аппаратурные затраты модифицированного устройства

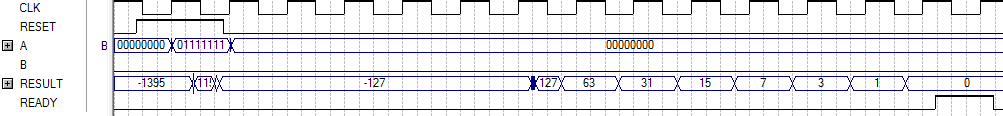

На рис. 8. представлены временные характеристики модифицированного последовательного умножающего устройства.

Рис. 8. Временные характеристики модифицированного устройства

На рис. 9 представлен критический путь, ограничивающий тактовую частоту работы устройства.

Рис. 9. Критический путь для модифицированного устройства

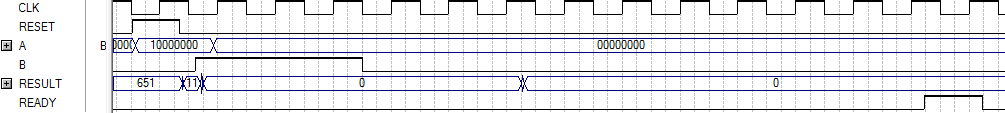

Ниже на рис. 10 - 16 приведены результаты тестирования модифицированного последовательного умножающего устройства.

|

|

|

Рис. 10. Умножение числа А=1.1011101пр = -9310 пр на В=0.0111обр = 710 пр

Рис. 11. Умножение числа А=0.0111010пр = 5810 пр на В=1.1100обр = -310 пр

Рис. 12. Умножение числа А=1.1011101пр = -9310 пр на В=1.1111обр = -010 пр

Рис. 13. Умножение числа А=1.1011101пр = -9310 пр на В=0.1111обр = 1510 пр

Рис. 14. Умножение числа А=0.1111111пр = 12710 пр на В=0.0000обр = 010 пр

Рис. 15. Умножение числа А=0.1011101пр = 9310 пр на В=0.0111обр = 710 пр

Рис. 16. Умножение числа А=1.0000000пр = -010 пр на В=0.0111обр = 710 пр

Из результатов тестирования видно, что синтезированное устройство успешно прошло все предложенные наборы тестов.

|

|

|