|

Контроллер прямого доступа в память К580ВТ57

|

|

|

|

Микросхема К580ВТ57 предназначена для управления передачей информации между ВУ о ЗУ в режиме ПДП. Основное назначение контроллера - формирование последовательности адресов и управляющих сигналов.

Контроллер ПДП имеет четыре независимых канала обмена. Блок управления каждого канала включает два 16-разрядных регистра: регистр начального адреса РА и регистр управления РУ, причем РУ[13:0] хранит длину передаваемого массива (количество передаваемых байт), а РУ[15:14] - режим работы канала. Структурная схема контроллера и схема подключения его к МПС показана на рис. 6.2.

Рис. 6.2. Контроллер прямого доступа в память

Контроллер включает в себя, помимо четырех каналов ПДП, схему управления, обеспечивающую связь с системной шиной, разрешение конфликтных ситуаций в соответствии с заданной системой приоритетов и управление работой контроллера в различных режимах.

Схема управления содержит два восьмиразрядных регистра, общие для всех каналов - регистр режимов РгР и регистр состояний РгС, причем РгР доступен процессору только по записи, а РгС только по чтению. Форматы регистров РгР и РгС показаны на Рис. 6.3.

| Рг Р: | AL | TCS | EW | RP | EN3 | EN2 | EN1 | EN0 |

| Рг С: | UF | TC3 | TC2 | TC1 | TC0 |

Рис. 6.3. Форматы регистров режима и состояния

В регистре режимов разряды имеют следующий смысл:

Ø AL - автозагрузка;

Ø TCS - отключение канала;

Ø EW - расширенная запись;

Ø RP - циклический приоритет;

Ø EN[3:0] - разрешение работы каналов 3..0.

В регистре состояния:

Ø UF - флаг обновления;

Ø TC[3:0] - конец счета в каналах 3..0.

Выводы контроллера можно разделить на две группы: (а) линии связи с ВУ и (б) линии связи с системной шиной МПС.

|

|

|

а)

DRQ[0:3] - запросы от ВУ (каналов) на прямой доступ в ЗУ;

DACK[0:3]\ - разрешения на ПДП внешним устройствам;

TC - конец счета, сигнал H-уровня на этом выходе отмечает последний цикл передачи блока данных;

MARK - маркер - сигнал H-уровня указывает, что до конца передаваемого блока необходимо выполнить число циклов обмена, кратное 128.

б) Линии связи с системной шиной передают стандартные сигналы управления, которые используются традиционно: RESET, READY (контроллер анализирует состояние готовности и при необходимости, как и МП, вставляет такты ожидания Tw), RDM\, WRM\, RDIO\, WRIO\, HRQ, HLDA. Контроллер синхронизируется внешним системным синхросигналом, в качестве которого чаще всего используется Ф2ттл. Сигнал ADSTB не поступает на системную шину и служит для "защелкивания" старшего байта адреса, передаваемого по шине данных в режиме ПДП (см. ниже). Сигнал AEN отмечает время действия цикла ПДП и может быть использован в системе для предотвращения захвата шины другими устройствами. Вход CS\ обеспечивает выбор микросхемы при адресной селекции.

Перед началом работы контроллера по сигналу RESET очищаются регистры всех каналов и регистр режимов РгР. Очистка РгР приводит к запрету работы всех каналов во всех режимах и предотвращает конфликты на шинах при подаче напряжения питания. Разрешение работы каналов не должны включаться, пока в регистры адресов и управления соответствующих каналов не будут загружены необходимые числа. В противном случае запрос DRQ от ВУ может вызвать циклы ПДП и порчу данных в памяти.

Контроллер ПДП может работать в двух режимах: в режиме программирования и в режиме ПДП.

В режиме программирования контроллер является пассивным устройством и процессор осуществляет с ним связь как с обычным ВУ. При этом линии A[3:0] и RDIO\, WRIO\ являются входными. Линии адреса A[2:1] при A[3] = 0 используются для селекции канала (код соответствует номеру канала), а тип регистра в канале идентифицируется разрядом A[0]: "0" - РгA, "1" - РгУ. Поскольку РгА и РгУ - двухбайтовые регистры, их загрузка осуществляется двумя циклами записи по одному адресу, причем в первом цикле передается младший байт.

|

|

|

При A[3:0] = 1000 осуществляется запись в РгР или чтение из РгС.

Разряды 0..3 регистра режимов РгР разрешают или запрещают работу соответствующих каналов ("1" - разрешено, "0" - запрещено).

Разряд РгР[4] устанавливает тип приоритета работы каналов. При РгР[4] = 0 установлен фиксированный приоритет (канал 0 -высший, канал 3 - низший). При РгР[4] = 1 устанавливается циклический приоритет каналов. В этом режиме после каждого цикла ПДП (но не запроса) приоритет каждого канала изменяется. Канал, который только что был обслужен, получает низший приоритет, а остальные каналы - по кольцу 0 - 1 - 2 - 3 - 0 -.

Циклический сдвиг приоритетов предотвращает монополизацию одного канала; последовательность циклов ПДП будет обслуживать различные каналы, если их работа не запрещена. Все операции начинаются с присвоения каналу 0 высшего приоритета.

Разряд РгР[5] = 1 определяет режим опережающей записи. В этом случае длительность сигналов WRM\ и WRIO\ увеличивается за счет более ранней их активизации в цикле ПДП. Это в некоторых случаях позволяет обойтись без тактов ожидания Tw.

Состояние "1" в разряде РгР[6] определяет режим автоматического отключения канала по сигналу TC. Этот сигнал возникает когда РгУi[13:0] = 0; в этом случае сбрасывается бит разрешения работы активного канала и запустить его вновь в работу можно только путем программной перезагрузки РгР. При РгР[6] = 0 появление TC не запрещает дальнейшую работу канала.

При наличии "1" в РгР[7] устанавливается режим автозагрузки, позволяющий каналу 2 многократно передавать массив данных без программного вмешательства. При программировании канала 2 в этом режиме его параметры (РгА и РгУ) автоматически дублируются в соответствующих регистрах канала 3 и по сигналу TC переписываются из канала 3 в канал 2, восстанавливая первоначальное значение РгА2 и РгУ2, причем эта передача сопровождается установкой флага обновления UF в РгС[4]. Заметим, что возможности режима TCS (отключение каналов) не распространяются на канал 2 в режиме автозагрузки.

|

|

|

Если не запретить работу канала 3 в режиме автозагрузки, то он может работать как обычно при отсутствии запроса DRQ2. Однако, следует помнить, что работа канала 3 изменит значения параметров, которые должны передаваться в канал 2.

Перед началом работы каждый канал программируется путем занесение в РгА начального адреса массива, в РгУ[13:0] - количества передаваемых байт, а в РгУ[15:14] - режима работы канала (00 контроль, 01 - запись в ЗУ, 10 - чтение из ЗУ).

Режим контроля может использоваться ВУ для контроля принятых данных, т.к. в этом режиме не производится передача данных (не вырабатываются сигналы RDM\, RDIO\, WRM\, WRIO\), а все остальные функции ПДП сохраняются.

В режим ПДП контроллер переходит при поступлении запроса DRQ незамаскированного канала. Он вырабатывает запрос микропроцессору HRQ на захват шины и, получив подтверждение HLDA, передает сигнал активизации DACK\ выбранному ВУ и начинает циклы ПДП.

В цикле ПДП контроллер выдает содержимое РгА на линии A[7:0] (младший байт) и линии D[7:0] (старший байт в сопровождении строба ADSTB) и, в зависимости от режима работы канала, одну из пар управляющих сигналов RDM\ + WRIO\ или RDIO\ + WRM\ (в режиме контроля управляющие сигналы не выдаются). Режим ПДП завершается при снятии сигнала DRQ.

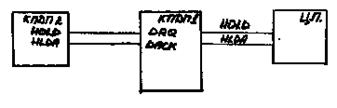

Каскадирование КПДП

Рис. 6.4. Каскадирование КПДП

Организация ПДП в IBM PC

В современных машинах используются дополнительные контроллеры ПДП, один из которых 16-ти разрядный, но также есть и 8-ми разрядные.

При программировании контроллера указываются адреса, приоритеты, регистр страниц ПДП.

Рис. 6.5. Организация ПДП в IBM PC

|

|

|