|

Разработка регистровой схемы

|

|

|

|

Рассмотрим разработку четырехразрядного сдвигающего регистра, обеспечивающего преобразование последовательного кода в параллельный и имеющего информационный вход DIN, вход синхронизации CLK и выход DOUT[3/0]. Ввод проекта и описание схемы на языке VHDL производится в соответствии с правилами, описанными в разделе 2.2. Тип микросхемы - ПЛИС типа FPGA xc2s15-vq100-5. Описание интерфейса данной схемы будет выглядеть следующим образом.

Рис. 2.15. Задание интерфейса разрабатываемой схемы

В качестве шаблона можно использовать пункт Serial to Parallel Shift Register из группы сдвигающих регистров Shift Registers. Окончательный вид описания регистра будет следующим:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity rg is

Port (DIN: in std_logic;

CLK: in std_logic;

DOUT: out std_logic_vector(3 downto 0));

end rg;

architecture Behavioral of rg is

signal REG: STD_LOGIC_VECTOR(3 downto 0);

begin

process (CLK)

begin

if CLK'event and CLK='1' then

REG(3 downto 0) <= DIN & REG(3 downto 1);

end if;

DOUT <= REG;

end process;

end Behavioral;

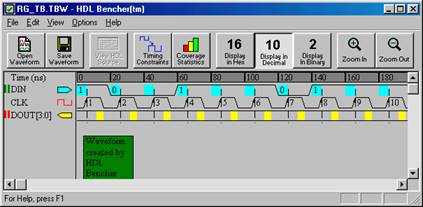

Внешние сигналы с помощью редактора ограничений задаются на следующие контакты: din - P40, clk - P39, dout[3/0] - P41, P43, P4, P45. Для моделирования с помощью программы Test Behcher задаются временные диаграммы сигналов din и clk, которые показаны на рис. 2.16.

Рис. 2.16. Входные сигналы

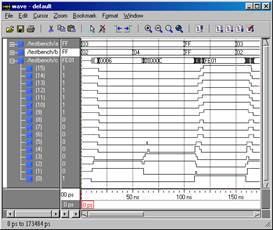

На этих временных диаграммах заданы следующие параметры: длительности единичного и нулевого значения синхросигнала – по 10 нс, время установки входных воздействий перед фронтом тактового сигнала и время задержки выходных значений по 6 нс. Моделирование производится на основе данных сигналов с применением программы ModelSim. Результаты функционального моделирования показаны на рис. 2.17.

Рис. 2.17. Результаты моделирования

В отчете о размещении схемы показано, что для реализации схемы используются 4 триггера в двух секциях, что отражено следующими строками:

|

|

|

Number of SLICEs 2 out of 192 1%

Number of Slice Flip Flops: 4 out of 384 1%.

Для реализации внешних связей требуется 5 обычных блоков ввода-вывода и один специализированный для синхросигнала с использованием глобального буфера GCLK:

Number of External IOBs 5 out of 60 8%

Number of External GCLKIOBs 1 out of 4 25%

Number of GCLKs 1 out of 4 25%

Распределение внешних сигналов по контактам, полностью совпадающее с заданным выше, отражается следующим фрагментом:

Resolved that GCLKIOB <clk> must be placed at site P39.

Resolved that IOB <din> must be placed at site P40.

Resolved that IOB <dout<0>> must be placed at site P41.

Resolved that IOB <dout<1>> must be placed at site P43.

Resolved that IOB <dout<2>> must be placed at site P44.

Resolved that IOB <dout<3>> must be placed at site P45.

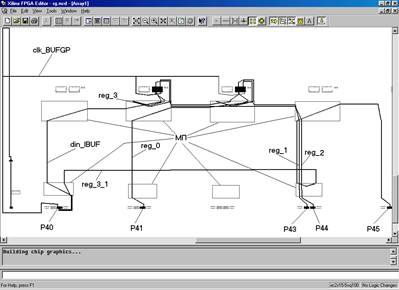

На рис. 2.18 приведен фрагмент ПЛИС, полученный с помощью программы FloorPlanner. Из этого рисунка видно, что для проектируемой схемы системой САПР ISE отведены 2 секции в блоках ПЛБ, расположенных по адресам R8C8 и R8C9. Данные секции выделены темным цветом.

Рис. 2.18. Размещение узлов схемы в ПЛИС

Информация о величине задержек схемы отражена в следующих строках:

The Average Connection Delay for this design is: 0.853 ns

The Maximum Pin Delay is: 1.564 ns

The Average Connection Delay on the 10 Worst Nets is:) 0.637ns

Listing Pin Delays by value: (ns)

d<1.00 <d< 2.00 <d< 3.00 <d< 4.00 <d< 5.00 d>= 5.00

8 4 0 0 0 0

Полная информация о задержках приведена в таблице:

-------------------------------

| Max Delay (ns) | Netname |

-------------------------------

1.564 reg_3_1

1.540 reg_2

1.209 reg_0

1.202 reg_1

0.853 reg_3

0.721 din_IBUF

0.469 clk_BUFGP

0.007 clk_BUFGP/IBUFG

---------------------------------

На рис. 19 показан фрагмент ПЛИС, на котором размещена проектируемая схема. Данный рисунок получен с помощью программы редактора FPGA (FPGA Editor).

Рис. 2.19. Окончательное размещение узлов и связей

На этом рисунке приведены контакты P40, P41, P43, P44 и P45, которые соответствуют входному сигналу DIN и выходным сигналам DOUT[0], DOUT[1], DOUT[2] и DOUT[3]. На рисунке показаны также внутренние сигналы reg_0, reg_1, reg_2 и reg_3. Название последних присвоила сама система, и их имена соответствуют индексам сигналов DOUT[0] … DOUT[3]. В схеме продублирован внутренний сигнал reg_3, его аналог имеет наименование reg_3_1 и используется для формирования сигнала DOUT[3] на контакте P45, сам сигнал reg_3 используется для формирования сигнала reg_2 при сдвиге. Указанное дублирование вызвано тем, что в системе задан режим оптимизации по быстродействию, и система обеспечивает максимальное быстродействие, пусть и за счет усложнения схемы.

|

|

|

Фрагмент секции CLB_R8C8.S0, где формируются два младших разряда, показан на рис. 2.20.

Рис. 2.20. Блок ввода-вывода

На рис. 2.21 показан фрагмент блока ввода-вывода (IOB) P40, который обеспечивает прохождение входного сигнала DIN. Сигнал поступает на входной контакт PAD, затем проходит через ряд буферных схем. Во внутреннюю логику ПЛИС поступает сигнал din_IBUF, а также сигнал reg_3_1, который вырабатывается на выходе D –триггера, находящегося в блоке ввода-вывода.

Рис. 2.21. Программируемый логический блок

Таким образом, разработчику достаточно ввести описание схемы на языке VHDL, а все остальное выполняет система проектирования.

Разработка умножителя

Пусть требуется разработать комбинационный умножитель 16х16 разрядов. Выходной код в этом случае должен иметь 32 разряда. Необходимо отметить, что в ряде современных семейств ПЛИС имеются встроенные умножители, однако в настоящем разделе используется ПЛИС типа FPGA XC2S15-VQ100, в которой таких блоков нет.

Описание умножителя на языке VHDL имеет следующий вид:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity mult is

Port (a: in std_logic_vector(7 downto 0);

b: in std_logic_vector(7 downto 0);

c: out std_logic_vector(15 downto 0));

end mult;

architecture Behavioral of mult is

signal d: std_logic_vector (15 downto 0);

begin

d <= a*b;

c <= d;

end Behavioral;

Схема занимает 32 блока ввода-вывода и 36 секций для реализации логических функций. Об этом свидетельствуют строки из отчета о размещении и трассировке:

Number of External IOBs 32 out of 60 53%

Number of SLICEs 36 out of 192 18%.

Распределение длительностей связей будет выглядеть следующим образом:

d<1.00 <d<2.00 <d<3.00 <d<4.00 <d<5.00 d>=5.00

65 137 27 5 0 0.

Распределение сигналов по контактам:

Signal Name | Pin |Signal Name | Pin |Signal Name | Pin |

a<0> | P20 | a<1> | P19 | a<2> | P10 |

a<3> | P8 | a<4> | P9 | a<5> | P5 |

|

|

|

a<6> | P4 | a<7> | P98 |

b<0> | P22 | b<1> | P97 | b<2> | P21 |

b<3> | P6 | b<4> | P31 | b<5> | P71 |

b<6> | P72 | b<7> | P93 |

c<0> | P30 | c<1> | P18 | c<2> | P17 |

c<3> | P16 | c<4> | P59 | c<5> | P32 |

c<6> | P60 | c<7> | P62 | c<8> | P65 |

c<9> | P66 | c<10> | P69 | c<11> | P7 |

c<12> | P95 | c<13> | P96 | c<14> | P15 |

c<15> | P13

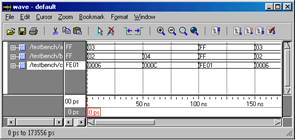

На рис. 2.22 показаны результаты функционального моделирования (рис. 2.22 а) и временного моделирования (рис. 2.22 б), полученного после реализации схемы.

а

б)

Рис. 2.22. Результаты моделирования

Разработанный умножитель является комбинационной схемой, поэтому для разработчика в данном случае представляют интерес задержки распространения сигнала от входа до выхода (Pad to Pad). Удобным средством для получения этих данных является программа временного анализатора Timing Analyzer, который позволяет получить самую разнообразную информацию о задержках. На рис. 2.23 показано окно анализатора Timing Analyzer, в котором приведен фрагмент отчета о задержках от входа до выхода (Pad to Pad).

Рис. 2.23.

Ниже приведены максимальные задержки от входа до выхода.

---------------+---------------+---------+

Source Pad |Destination Pad| Delay |

---------------+---------------+---------+

a<0> |c<13> | 19.177|

a<5> |c<13> | 19.110|

b<0> |c<13> | 19.033|

b<5> |c<10> | 19.149|

b<5> |c<11> | 19.109|

b<5> |c<12> | 19.122|

b<5> |c<13> | 19.381|

---------------+---------------+---------+

Еще одним способом задания нужных временных параметров типа Pad to Pad является задание временных ограничений с помощью программы редактора ограничений (Constraints Edior). Окно этой программы приведено на рис. 2.5, временные ограничения типа Pad to Pad задаются на вкладке Global. Например, для данной схемы может быть задано максимальное значение задержки величиной 20 нс. В файле ограничений пользователя это будет задано строкой:

TIMESPEC "TS_P2P" = FROM "PADS" TO "PADS" 20 ns.

Если система САПР не сможет обеспечить требуемое быстродействие, то об этом будет сообщено разработчику, и он должен предпринять соответствующие меры, например, взять микросхему с более высоким быстродействием.

|

|

|