|

Разработка структурной схемы

|

|

|

|

Разрабатываемое АЛУ будет иметь восьмиразрядный вход данных X, восьмиразрядный вход данных Y, шестнадцатиразрядный выход результата Z, вход начала вычисления START, выход готовности результата READY, вход принудительного сброса R и тактовый вход C (рис.2.1).

Рисунок 2.1 Условное графическое изображение АЛУ.

При разработке структурной схемы необходимо обратить внимание на уменьшение количества применяемых элементов, что в свою очередь приведет к снижению потребляемой мощности. Одновременно с этим необходимо обеспечить время вычисления менее заданного. Также необходимо уделить внимание предотвращению гонок в схеме.

Исходными данными для разработки структурной схемы является алгоритм вычисления. В соответствии с заданным алгоритмом вычисления для его реализации как минимум потребуются два регистра для хранения и сдвига операндов. Для реализации счётчика потребуется три триггера. Для определения окончания вычисления необходима схема сравнения J с 0.

Для реализации математических вычислений потребуется восьмиразрядный сумматор.

Разработанная структурная схема показана на рис. 2.2. В этой схеме множитель Y и результат Z хранятся в одном сдвиговом 16-ти разрядном регистре RgY. Регистры RgХ и RgY имеют как прямые, так и инверсные выходы, что позволяет уменьшить количество элементов в сумматоре.

Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел.

Рисунок 2.2 Структурная схема АЛУ для умножения двоичных чисел.

Как видно из схемы активный уровень сигналов управления - высокий, и устройство управления тактируется по фронту импульса, а исполнительные устройства - по спаду, что позволяет избежать гонок в схеме.

Синтез Компонентов

Синтез сумматора

|

|

|

Так как построить сумматор сразу для восьми разрядов достаточно сложно, сумматор будем выполнять по схеме последовательного соединения полных одноразрядных сумматоров.

Таблица истинности полного двоичного сумматора приведена в табл.3.1, где а и b - слагаемые, S - сумма, P - перенос из предыдущего разряда. Рn – перенос в следующий разряд.

Таблица 3.1

| а | B | P | S | Рn |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

По таблице истинности строим карты Карно (рис.3.1) и проводим минимизацию логических выражений, описывающих работу полного сумматора.

S Pn

|

|

|

|

|

|

|

| |||

| 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | |

| P | 1 | 0 | 1 | 0 | P | 0 | 1 | 1 | 1 | |

a a

|

|

|

|

|

|

|

|

Рисунок 3.1 Карты Карно для полного сумматора.

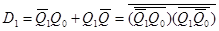

(3.1)

(3.1)

(3.2)

(3.2)

Полученные выражения (3.1) и (3.2) приводим к заданной элементной базе:

(3.3)

(3.3)

(3.4)

(3.4)

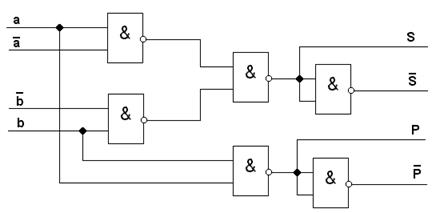

По полученным выражениям строим схему полного сумматора (рис.3.2).

Рисунок 3.2 Принципиальная схема полного сумматора.

Нулевой разряд сумматора для экономии элементов построим по схеме полусумматора. Таблица истинности полусумматора представлена в табл.3.2.

Таблица 3.2

| А | B | S | Ро |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

По таблице истинности получаем логические выражения:

(3.5)

(3.5)

(3.6)

(3.6)

По полученным выражениям строим принципиальную схему (рис.3.3).

Рисунок 3.3 Принципиальная схема полусумматора.

Потребляемую схемой мощность найдем по формуле:

. (3.7)

. (3.7)

где N – количество логических элементов в схеме;

– мощность, потребляемая одним элементом.

– мощность, потребляемая одним элементом.

Количество элементов в схеме равно 83 а мощность элемента –  . Подставляя данные в формулу (3.7) получим:

. Подставляя данные в формулу (3.7) получим:

|

|

|

.

.

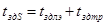

Время вычисления будет максимально в случае формирования переноса последовательно в семи младших разрядах сумматора. Таким образом, время счета будет определяться как сумма времени формирования переноса в семи младших разрядах и времени формирования выходного сигнала в старшем разряде:

, (3.8)

, (3.8)

где  – время срабатывания одного логического элемента;

– время срабатывания одного логического элемента;

– максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

– максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

– максимальный путь формирования результата в старшем разряде (3 элемента).

– максимальный путь формирования результата в старшем разряде (3 элемента).

Время срабатывания равно 4  . Пути

. Пути  для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

.

.

Синтез регистров

Для хранения и сдвига множителя Y и суммы S необходим шестнадцатиразрядный регистр сдвига. Для хранения множимого понадобится один восьмиразрядный регистр RgX.

Структурная схема регистра сдвига показана на рис.3.4, из которого видно, что необходимо синтезировать одну комбинационную схему. Таблица истинности для этой схемы представлена в табл. 3.3, где значение управляющего сигнала W/S равное нулю соответствует режиму записи, а равное единице - режиму сдвига на один бит вправо за такт.

Рисунок 3.4 Структурная схема регистра сдвига.

Таблица 3.3

| D | Q | S | J |

| X | 0 | 0 | 0 |

| X | 1 | 0 | 1 |

| 0 | X | 1 | 0 |

| 1 | X | 1 | 1 |

По приведенной таблице истинности находим логические выражения, описывающие работу синтезируемой схемы, и приводим их к заданному базису.

(3.9)

(3.9)

Рисунок 3.5 Схема управления сдвигом.

Принципиальная схема, построенная по выражению (3.9), приведена на рис.3.5.

Восьмиразрядный регистр для хранения Х будет представлять собой восемь JK – триггеров с объединенными тактовыми входами.

Мощность, потребляемую регистрами, определим по формуле

, (3.10)

, (3.10)

где  ,

,  – количество триггеров в регистрах RgX и RgY соответственно;

– количество триггеров в регистрах RgX и RgY соответственно;

– мощность, потребляемая триггером (12 мВт).

– мощность, потребляемая триггером (12 мВт).

- мощность, потребляемая схемой управления сдвигом (8 мВт).

- мощность, потребляемая схемой управления сдвигом (8 мВт).

Подставив численные значения в формулу (3.10), получим:

.

.

Время предустановки регистра равно времени предустановки триггера  , а время задержки – времени задержки триггера

, а время задержки – времени задержки триггера  .

.

|

|

|

Синтез счётчика

По принципу формирования выходных сигналов счетчики бывают последовательные и параллельные. У первых каждый разряд счётчика устанавливается последовательно вслед за предыдущим. В параллельных счётчиках переключение происходит параллельно всех разрядов. Таким образом, последовательные счётчики имеют задержку кратную разрядности, поэтому могут применяться в устройствах не критичных к быстродействию.

Разрабатываемая схема не позволяет применить последовательный счётчик, поэтому будет применяться параллельный (синхронный) счётчик. Так как необходимо считать до восьми, то счетчик будет трёхразрядным. Такой счётчик можно синтезировать как цифровой автомат с кольцевым последовательным перемещением. В этом режиме при поступлении тактового сигнала на триггеры записывается информация с комбинационных схем, преобразующих предыдущее состояние счётчика в последующее. Состояния счётчика приведены в таблице 3.4.

Таблица 3.4

| N | Q2 | Q1 | Q0 | D2 | D1 | D0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 1 | 1 | 0 | 0 |

| 4 | 1 | 0 | 0 | 1 | 0 | 1 |

| 5 | 1 | 0 | 1 | 1 | 1 | 0 |

| 6 | 1 | 1 | 0 | 1 | 1 | 1 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 |

(3.11)

(3.11)

(3.12)

(3.12)

(3.13)

(3.13)

Приводим данные выражения к заданному базису:

(3.14)

(3.14)

(3.15)

(3.15)

(3.16)

(3.16)

Схема такого счётчика показана на рис. 3.6.

Рисунок 3.6 Схема параллельного счетчика.

Мощность, потребляемую схемой, определим по формуле

. (3.17)

. (3.17)

Подставляя численные значения, получим:

.

.

Максимальное время задержки счетчика в параллельном режиме будет равно сумме времени задержки КС и времени задержки триггера:

. (3.18)

. (3.18)

Максимальный путь сигнала в КС – 2 элемента. Тогда по формуле (3.18):

.

.

В режиме счета быстродействие счетчика будет определяться только параметрами триггера ( и

и  ) и логических элементов (

) и логических элементов ( ), что в сумме меньше полученного ранее результата. Следовательно, в дальнейших расчетах будем использовать значение

), что в сумме меньше полученного ранее результата. Следовательно, в дальнейших расчетах будем использовать значение  .

.

|

|

|

|

|

|