|

Standard (Types: Bit, Boolean, Integer, Real, Time. Все функции для поддержки типов данных)

|

|

|

|

Иерархическое представление объектов на языке VHDL. Пример проекта.

ИЕРАРХИЧНОСТЬ ОПИСАНИЯ

Создание экземпляров компонент делает возможным создание иерархии проекта по аналогии с тем, как вставляются чипы в печатную плату.

Иерархическое представление объекта

Иерархическое представление объекта

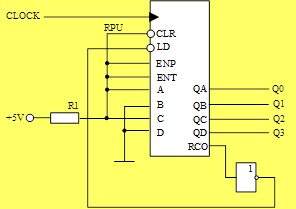

Счетчик по модулю 11 с последовательностью

счета 5 – 15, 5 – 15

|

|  | |||

| ||||

Cтруктура проекта на языке VHDL

Cтруктура проекта на языке VHDL

| ARCHITECTUREArch_D OF CompD IS component Nand2 port(x1, x2: in std_logic; y: out std_logic); end component; signal a1, a2, a3: std_logic; BEGIN Ela1: Nand2 port map(D, D, a1); Ela2: Nand2 port map(D, C, a2); Ela3: Nand2 port map(C, a1, a3); ElQ: Nand2 port map(a2, NQ, Q); ElNQ: Nand2 port map(Q, a3, NQ); END Arch_D; |

ENTITY CompD IS

port (D, C: in std_logic;

Q, NQ: inout std_logic);

end CompD;

| |||||||

| |||||||

| |||||||

| |||||||

Настроечная константа generic. Пример применения.

Настроечная константа generic кодирует определенное свойство объекта проекта.

Она используется, например, для задания разрядности линий связи, задержки и др.

Упрощенный синтаксис:

\объявление настроечных констант\::= generic(\объявление настроечной константы\ {; \объявление настроечной константы\}); \объявление настроечной константы\::= \идентификатор\:\тип\[:=\начальное значение\]

ПРИМЕР

generic (T1: Time:= 20ns; T2: Time:= 5 ns; numb: integer:= 12);

Из примера видно, что в декларации port перечисляются формальные сигналы, а в port map - фактические сигналы. При этом последовательность перечисления в обоих местах должна быть согласована.

entity schema is

port (a,b,c,d,e: in BIT; y: out BIT);

end schema;

architecture str of schema is

component AND_OR

generic (delay1: Time);

port (i1,i2,i3,i4: in BIT; a: out BIT);

end component AND_OR;

component OR2

generic (delay2: Time);

port (i1,i2: in BIT; a: out BIT);

end component OR2;

signal z1,z2: BIT;

begin

E1: AND_OR

|

|

|

generic map (delay1:= 4 ns);

port map (a,c,b,c,z1);

E2: AND_OR

generic map (delay1:= 5 ns);

port map (d,c,e,c,z2);

E3: OR2

generic map (delay2:= 3 ns);

port map (z1,z2,y);

end str;

Сигнал. Примеры применения. Сравнение операторов присваивания и назначения сигнала.

Сигнал

Сигналом является объект, который переносит значение от одного процесса к другому и вместе с ним - синхронизирующее воздействие. История сигнала может быть запомнена и воспроизведена в симуляторе в виде графика или таблицы. Объявление сигнала выглядит как:

Signal \идентификатор\{,\идентификатор\}:=[\начальное значение\];

где - \начальное значение\ - выражение, представляющее константу, значение которой принимает сигнал перед первым запуском процесса.

Пример объявления сигнала:

signal reg: BIT_VECTOR:= ‘1001100101’;

signal R1: std_logic:=‘0’;

Сравнение операторов присваивания:=

и назначения сигнала <=

Особенность оператора <= в том, что присвоение значений сигналам всегда происходит с задержкой, большей нуля.

Поэтому использование операторов присваивания и назначения сигналов в одной и той же ситуации может дать разные результаты.

ПРИМЕР:

A:= B or X;

C:= A and Z;

Пусть В = 0, Z=1 и в рассматриваемый момент времени Х переключается из 0 в 1. После выполнения этих двух операторов С равно 1.

В случае

A <= B or X;

C <= A and Z; -- используется старое значение А.

Если старое значение А есть 0, то сигнал С в данный момент времени равен 0.

Типы STD_LOGIC. Алфавит моделирования.

STD_LOGIC

Entity AOI is

port (A, B, C, D: in STD_LOGIC;

F: out STD_LOGIC);

end AOI;

Ø Тип данных порта определяет множество значений, которые могут проходить через порт.

Ø Порты объявлены типа STD_LOGIC, который находится в пакете STD_LOGIC_1164 библиотеки IEEE.

Ø Пакет STD_LOGIC_1164 является стандартом IEEE для представления логических сигналов в VHDL.

Алфавиты моделирования

TYPE std_ulogic IS

('U', -- Uninitialized

-- (начальная неопределенность)

'X', -- Forcing Unknown (сильная

-- неопределенность)

'0', -- Forcing 0 (сильный «0»)

|

|

|

'1', -- Forcing 1 (сильная «1»)

'Z', -- High Impedance (высокий

-- импеданс)

'W', -- Weak Unknown (слабая

-- неопределенность)

'L', -- Weak 0 (слабый «0»)

'H', -- Weak 1 (слабая «1»)

'-' -- Don't care (безразлично)

);

CONSTANT resolution_table: stdlogic_table:= (

-- ---------------------------------------------------------

-- | U X 0 1 Z W L H - | |

-- ---------------------------------------------------------

('U', 'U', 'U', 'U‘, 'U', 'U', 'U', 'U', 'U'), -- | U |

('U', 'X', 'X', 'X‘, 'X‘, 'X', 'X', 'X', 'X'), -- | X |

('U', 'X', '0', 'X', '0‘, '0', '0', '0', 'X'), -- | 0 |

('U', 'X', 'X', '1', ‘1‘, '1', '1', '1', 'X'), -- | 1 |

('U', 'X', '0', '1', 'Z‘, 'W', 'L', 'H', 'X'), -- | Z |

('U', 'X', '0', '1', 'W‘,'W', 'W', 'W', 'X'),-- | W |

('U', 'X', '0', '1', 'L', 'W', 'L', 'W', 'X'), -- | L |

('U', 'X', '0', '1', 'H', 'W‘, 'W', 'H', 'X'), -- | H |

('U', 'X', 'X', 'X', 'X', 'X', 'X', 'X', 'X') -- | - |

);

Алфавиты моделирования

CONSTANT and_table: stdlogic_table:= (

-- ----------------------------------------------------

-- | U X 0 1 Z W L H - | |

-- ----------------------------------------------------

('U', 'U', '0', 'U', 'U', 'U', '0', 'U', 'U'), -- | U |

('U', 'X', '0', 'X', 'X', 'X', '0', 'X', 'X'), -- | X |

('0', '0‘, '0', '0', '0', '0', '0', '0', '0'), -- | 0 |

('U', 'X', '0', '1', 'X', 'X', '0', '1', 'X'), -- | 1 |

('U', 'X', '0', 'X', 'X', 'X', '0', 'X', 'X'), -- | Z |

('U', 'X', '0', 'X', 'X', 'X', '0', 'X', 'X'), -- | W |

('0', '0‘, '0', '0‘, '0', '0', '0', '0', '0'), -- | L |

('U', 'X', '0', '1‘, 'X', 'X', '0‘, '1', 'X'), -- | H |

('U', 'X', '0', 'X', 'X', 'X', '0', 'X', 'X') -- | - |

);

CONSTANT or_table: stdlogic_table:= (

-- ----------------------------------------------------

-- | U X 0 1 Z W L H - | |

-- ----------------------------------------------------

('U', 'U', 'U', '1', 'U', 'U', 'U', '1', 'U'), -- | U |

('U', 'X', 'X', '1', 'X', 'X', 'X', '1', 'X'), -- | X |

('U', 'X', '0', '1', 'X', 'X', '0', '1', 'X'), -- | 0 |

('1', '1‘, '1', '1', '1', '1‘, '1', '1', '1'), -- | 1 |

('U', 'X', 'X', '1', 'X', 'X', 'X', '1', 'X'), -- | Z |

('U', 'X', 'X', '1', 'X', 'X', 'X', '1', 'X'), -- | W |

('U', 'X', '0', '1', 'X', 'X‘, '0', '1', 'X'), -- | L |

('1', '1‘, '1', '1', '1', '1‘, '1‘, '1', '1'), -- | H |

('U', 'X', 'X', '1', 'X', 'X', 'X', '1', 'X') -- | - |

);

CONSTANT not_table: stdlogic_1d:=

-- -------------------------------------------------

-- | U X 0 1 Z W L H - |

-- -------------------------------------------------

('U', 'X', '1', '0', 'X', 'X', '1', '0', 'X');

Библиотека LIBRARY STD

содержит следующие встроенные пакеты:

Standard (Types: Bit, Boolean, Integer, Real, Time. Все функции для поддержки типов данных)

TEXTIO (File operations)

*****Они не требует объявления в проекте VHDL!!!

|

|

|