|

Нахождение проверочного многочлена

|

|

|

|

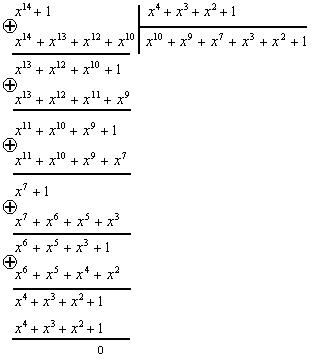

В качестве образующего многочлена выберем многочлен четвертой степени:  . Это неприводимый многочлен и деление на него многочлена х14+1 будет без остатка:

. Это неприводимый многочлен и деление на него многочлена х14+1 будет без остатка:

Таким образом получим проверочный многочлен:

Тогда структурная схема разрабатываемого кодирующего устройства будет выглядеть следующим образом:

Рисунок 2 - Структурная схема кодера с последовательной загрузкой

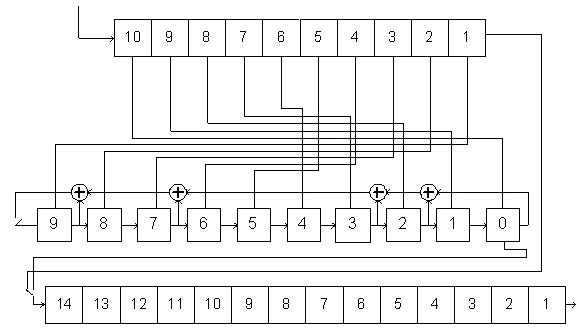

Также одним из возможных вариантов схемы кодера может быть схема, использующая параллельную загрузку информационной последовательности, проиллюстрированная на рисунке 3. Использование такой схемы улучшает быстродействие, но усложняет схемотехническую часть.

Рисунок 3 - Структурная схема кодера с параллельной загрузкой

4. Функциональное описание кодера

4. Функциональное описание кодера

В первую очередь опишем логические схемы, которые в определённые такты будут активизировать (отключать) нужные элементы схемы. То есть создадим схему управления. За один цикл кодирования одного 10 разрядного слова по описанной выше схеме проходит 24 такта: за 10 тактов происходит запись во входные регистры, далее в течение ещё 10 тактов начинается одновременная выдача информационных разрядов и подсчет проверочных символов. Затем за оставшиеся 4 такта на выход подаются проверочные символы, и на последнем такте происходит сброс содержимого регистров и восстановление схемы в исходное состояние.

Для отсчета тактов будем использовать счетчик, сигнал с которого поступает на вход Т-триггера. На выходе триггера, таким образом, поддерживается высокий постоянный уровень в течение первых 10 тактов и низкий уровень последующие 14 тактов, затем опять высокий уровень в течении 10 тактов Импульс переполнения счетчика переводит триггер в состояние, обратное предыдущему. Выходной сигнал триггера подается на адресный вход А мультиплексора. К первому входу данных мультиплексора подключена цепь обратной связи, этот вход будет активен при низком уровне на входе А мультиплексора. На второй вход поступает информационная последовательность, этот вход будет активен при высоком уровне на входе А мультиплексора.

|

|

|

Рассмотрим работу кодера построив временную диаграмму при подаче на вход последовательности 1000101010.

№ такта № такта

| Инф. | Символ в ячейке № | Вых. | Сигнал на входе А мультиплексора | |||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | |||||||||||||

| - | * | ||||||||||||

| - | * | * | |||||||||||

| - | * | * | * | ||||||||||

| - | * | * | * | * | |||||||||

| - | * | * | * | * | * | ||||||||

| - | * | * | * | * | * | * | |||||||

| - | * | * | * | * | * | * | * | ||||||

| - | * | * | * | * | * | * | * | * | |||||

| - | * | * | * | * | * | * | * | * | * | ||||

| - | * | * | * | * | * | * | * | * | * | * |

|

|

|

* - Значение в ячейке регистра несущественно (не влияет на выходной сигнал) кодера

5. Разработка принципиальной схемы.

5. Разработка принципиальной схемы.

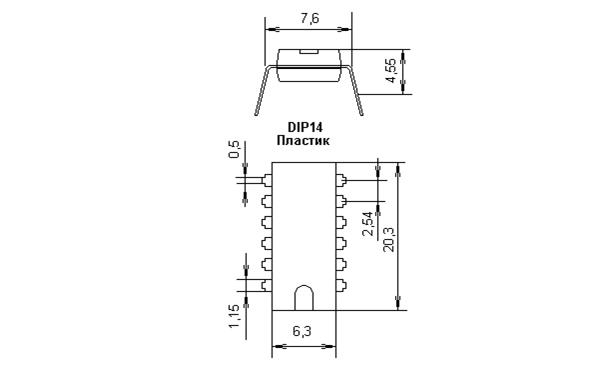

При разработке кодирующего устройства использовались микросхемы, изготовленные по технологии ТТЛ. Их основные преимущества – высокое быстродействие, экономичность, хорошая помехоустойчивость.

Так как мы используем микросхемы одной серии, то это решает проблему совместимости по входам и выходам и обеспечивает достаточную взаимную нагрузочную способность.

Используемые микросхемы.

1.В качестве сумматоров по модулю 2 будем использовать применение микросхемы К555 ЛП12, которая содержит четыре двухвходовых сумматора по модулю 2 Основные параметры – в таблице. Микросхема графически приведена на рисунке 4.

| Pпот, мВт | tзад, нс (при С=150пФ) | I0вых, мА | I1вых, мА | Число выводов | Напряжения питания, В | Диапазон рабочих Температур С° |

30,4 30,4

| 18,5 | 0,4 | 4,75…5,25 | -60..+125 |

Рисунок 4 - Микросхема исключающее ИЛИ

2. К555 ИЕ7 – двоичный 4-разрядный синхронный счётчик с предустановкой, построенный на основе J-K триггеров. Особенностью

счетчиков является их построение по синхронному принципу, по которому все триггеры схемы переключаются одновременно от одного счетного импульса. Направление счета в счетчиках определяется состоянием на счетных входах триггера. Условное обозначение и нумерация выводов на рисунке 5. Параметры микросхемы описаны в таблице.

| Pпот, мВт | tзад, нс | fраб, МГц | Число выводов | Напряжение питания, В | Icc, мА | Диапазон рабочих Температур, С° | tзад, нс (при 0 и1) |

| 25/35 | 4,75…5,25 | 0…70 | 16 и18 |

|

рисунок 5 - Счетчик К555 ИЕ7

Назначение входов ИЕ7 следующее:

Назначение входов ИЕ7 следующее:

L– вход параллельной загрузки;

CU – прямой счет;

СD – обратный счет;

R – инверсный статический вход обнуления (Сброс происходит при R = 0).

PU − инверсный выход переполнения (пока счетчик не переполнился, на выходе высокий уровень).

3. Регистр на 10 разрядов собран из трех четырехразрядных сдвиговых регистров. Микросхема К555ИР16 (рис. 6) – четырехразрядный сдвигающий регистр с возможностью асинхронной параллельной записи и последовательным считыванием. Микросхема имеет вход DR для подачи информации при последовательной записи, четыре входа D1 – D4 для подачи информации при параллельной записи, вход для подачи тактовых импульсов (вывод 9), вход параллельной записи L и прямой и инверсный выходы последнего разряда сдвигающего регистра. Сдвиг данных вправо на 1 позицию происходит согласно каждому положительному перепаду тактового импульса на входе С. Режим работы регистра определяется сигналом, поданным на вход L - при логическом 0 на нем происходит сдвиг информации, поступающей на вход DR, при логической 1 на входе L происходит параллельная запись информации со входов D1 – D4 в триггеры регистра.

3. Регистр на 10 разрядов собран из трех четырехразрядных сдвиговых регистров. Микросхема К555ИР16 (рис. 6) – четырехразрядный сдвигающий регистр с возможностью асинхронной параллельной записи и последовательным считыванием. Микросхема имеет вход DR для подачи информации при последовательной записи, четыре входа D1 – D4 для подачи информации при параллельной записи, вход для подачи тактовых импульсов (вывод 9), вход параллельной записи L и прямой и инверсный выходы последнего разряда сдвигающего регистра. Сдвиг данных вправо на 1 позицию происходит согласно каждому положительному перепаду тактового импульса на входе С. Режим работы регистра определяется сигналом, поданным на вход L - при логическом 0 на нем происходит сдвиг информации, поступающей на вход DR, при логической 1 на входе L происходит параллельная запись информации со входов D1 – D4 в триггеры регистра.

|

|

|

| Pпот, мВт | tзад(при 0и1) нс | fраб, МГц | Число выводов | Напряжение питания, В | Icc, мА | Диапазон рабочих Температур С° |

| 30 и28 | >20 | 4,75…5,25 | 0…70 |

Рисунок 6 - Микросхема К555ИР16.

4. Мультиплексор К555КП11 − двухканальный четырехразрядный мультиплексор, управляется сигналом адресного входа А. При низком уровне напряжения OE на выходы передается информация с соответствующих входов. Представлен на рисунке 7.

| Pпот, мВт | tзад(при 0и1) нс | Число выводов | Напряжение питания, В | Icc, мА | Диапазон рабочих температур С° |

| 30 и 27 | 4,75…5,25 | 0…70 |

Рисунок 7 - Микросхема К555КП11.

Рисунок 7 - Микросхема К555КП11.

Назначение контактов микросхемы:

2,3,5,6,10,11,13,14 - Входы

4,7,9,12 - Соответствующие выходы

А - Общий адресный вход

OE - Вход управления третьим состоянием

6. Список литературы.

6. Список литературы.

1. Дмитриев В.И. Прикладная теория информации: Учеб. Для студ. вузов. – М.: Высшая школа, 1989 г.

2. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. – М.: Радио и связь, 1990 г.

3. Бирюков С.А. - Применение интегральных микросхем серий ТТЛ, приложение к журналу «Радио», Выпуск 5. – М.: Патриот, 1992г.

4. Шило В.Л. Популярные цифровые микросхемы: Справочник. – 2-е изд., исправленное. – М.: Радио и связь, 1989 г.

|

|

|

Приложение А

Приложение А

|

|

|