|

Программируемые логические интегральные схемы

|

|

|

|

Развитие технологии ПЛМ привело к созданию программируемых логических интегральных схем (ПЛИС). Реализованные ими функции можно многократно изменять, нередко для этого даже не нужно вытягивать микросхему из устройства, в котором она работает.

Кристалл ПЛИС содержит большое число однотипных логических элементов. Соединяют элементы в нужном порядке с помощью перемычек — ключей на полевых транзисторах. А в каждом логическом элементе есть переключатели (мультиплексоры), программируя которые, можно изменять выполняемые функции.

Почти все внешние выводы ПЛИС универсальные. Они могут служить входом или выходом. Некоторые выводы имеют дополнительные функции, например, служат для программирования конфигурации микросхемы, которая, однако, не исключает их использование как обычного входа или выхода.

По внутренней структуре и способу запоминания конфигурации ПЛИС фирмы XILINX можно разделить на два вида:

FPGA (field programmable gate array — матрица вентилей, программируемых электрическим полем);

CPLD (complex programmable logic device — сложная программируемая логическая матрица).

К FPGA относят микросхемы серий ХС2000, ХСЗ000, ХС4000, ХС5200, ХС6000 и SPARTAN. Подобно ОЗУ, они сохраняют заданную конфигурацию только при включенном питании и "забывают" ее после выключения. Каждый раз, включив питание, такую ПЛИС необходимо программировать заново. Программу обычно сохраняют в установленном на одной плате с ПЛИС загрузочном ПЗУ, который может быть последовательным одноразрядным или обычным восьмиразрядным. Способ загрузки конфигурации задают логическими уровнями на управляющих входах. Процедура перезаписи выполняется автоматически, после чего ПЛИС переходит в рабочий режим.

|

|

|

В одном ПЗУ допускается сохранять информацию для нескольких ПЛИС. Одна из них служит ведущей (master) и, закончив собственную загрузку, руководит записью данных в ведомые (slave) микросхемы. Назначение ведущей или ведомой никак не влияет на логические функции, выполняемые ПЛИС после загрузки.

Специально для общей работы по ПЛИС фирма XILINX разработала и выпускает серию однократно программируемых последовательных ПЗУ ХС1700 информационной емкостью, достаточной для всех ПЛИС структуры FPGA, что выпускает эта фирма.

К CPLD относят микросхемы серий ХС7000 и ХС9500. Они сохраняют конфигурацию независимо от наличия напряжения питания. У микросхемы ХС7000 конфигурацию заносят с помощью устройства для программирования, а стирают ультрафиолетовым излучением. Такие ПЛИС устанавливают, как правило, в уже налаженные устройства. Для отладки новых изделий они неудобны из-за продолжительной (около часа) процедуры очистки.

Микросхемы серии ХС9500, выполненные по технологии FLASH, можно неоднократно программировать, не изымая из устройства, в которое они установлены. Для этого в них предусмотрен специальный порт JTAG. Чтобы записать исходную конфигурацию или внести в нее изменения, выводы этого порта через несколько буферных микросхем соединяют кабелем с портом LPT персонального компьютера.

Порт JTAG полезен не только для программирования. Через него компьютер может получить информацию о логических уровнях на всех выводах ПЛИС и в контрольных точках внутри нее. Возможность организовать такой порт предусмотрена и в ПЛИС структуры FPGA последних серий. Выводы микросхемы, занятые портом JTAG, могут служить и обычными входами/ выходами.

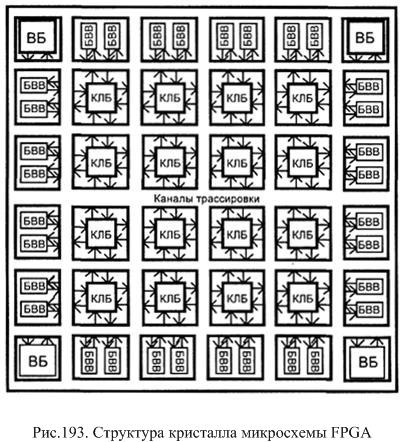

На рисунке 9.7 схематично показана структура кристалла микросхемы FPGA. Его центральную часть занимает матрица конфигурации логических блоков (КЛБ), а по периметру находятся блоки ввода/вывода (БВВ), соединенные с контактными площадками.

|

|

|

Рисунок 9.7

Представление о сложности современных ПЛИС дает таблица 9.3, где приведены сведения о числе КЛБ и БВВ, которые имеются в FPGA серии ХС4000. Вентили и триггеры в данном случае не самостоятельные элементы, а входят в состав указанных блоков (КЛБ), а по периметру находятся блоки ввода/вывода (БВВ), соединенные с контактными площадками.

Таблица 9.3 - Сведения о структуре серии ХС4000

| Микросхема | На кристалле находятся | Длина программы, бит | |||

| КЛБ | БВВ | Вентили | Триггеры | ||

| ХС4005 | 151 910 | ||||

| ХС4010 | 10 000 | 283 376 | |||

| ХС4013 | 13 000 | 393 580 | |||

| ХС4020 | 20 000 | 521 832 | |||

| ХС4028 | 28 000 | 668 132 | |||

| ХС4036 | 36 000 | 832 480 | |||

| ХС4044 | 44 000 | 1 014 876 | |||

| ХС4052 | 52 000 | 1 215 320 | |||

| ХС4062 | 62 000 | 1 433 812 | |||

| ХС4085 | 85 000 | 1 924 940 |

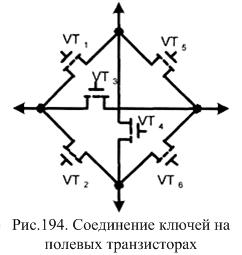

Любой из БВВ способен быть входным или выходным, а связанный с ним внешний вывод микросхемы - входом (IPAD), выходом (OPAD) или быть двунаправленным (IOPAD). По углам кристалла расположены вспомогательные узлы. Свободную от логических элементов площадь занимают каналы трассирования, где проложено большое число проводников, на пересечениях которых находятся программируемые ключи. Каждый ключ состоит из шести полевых транзисторов, соединенных, как показано на рисунок 9.8.

Рисунок 9.8

Задавая открытое или закрытое состояние каждого транзистора, можно соединить КЛБ между собою и с УВВ нужным образом.

К сожалению, такая структура не всегда позволяет реализовать необходимую конфигурацию. В сложных устройствах с большим числом длинных нерегулярных связей удается использовать не более половины ресурсов кристалла.

Схема простейшего УВВ (он применяется в микросхемах серии ХС5200) показана на рисунке 9.9.

Рисунок 9.9

Контактная площадка кристалла соединена с выходом управляемого буфера DD1 и с входом буфера DD2. Предусмотрена возможность задать выходной логический уровень на входе, связывая контактную площадку с общим проводом через резистор R1 или с шиной питания через резистор R2.

Программируемые переключатели S1, S2 обеспечивают прямую или инверсную связь УВВ с матрицей КЛБ. С помощью переключателя S3 при необходимости инвертируют входной сигнал.

|

|

|

Линия задержки U1 служит для выравнивания времен распространения сигналов по разным цепям ПЛИС.

Буфер DDJ снабжен устройством программирования продолжительности фронта выходного сигнала. Пологий фронт, не снижая внутреннего быстродействия ПЛИС, спасает от помех при плохом согласовании внешних нагрузок УВВ.

УВВ микросхем FPGA других серий более сложное (рисунок 9.10) и дополнительно имеет два D-триггера, с помощью которых можно запоминать значения входных и выходных сигналов. В некоторых случаях предусмотрена настройка на логические сигналы, характерные для микросхем структуры КМОП или ТТЛ.

Рисунок 9.10

КЛБ микросхемы серии ХС5200 состоит из четырех микроустройств, выполненных по схеме, приведенной на рисунке 9.11.

Рисунок 9.11

Каждое устройство содержит генератор произвольной логической функции четырех переменных DD1 (РПЗУ на 16 бит) и триггер DD2. Все четыре триггера одного КЛБ имеют общие входы сигналов асинхронного сбрасывания (CLR), синхронизации (СК) и разрешения (СИЕ).

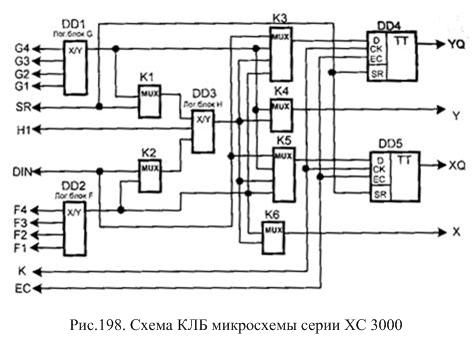

В состав КЛБ микросхем FPGA серий ХСЗ000, ХС4000 и Spartan (рисунок 9.12) входят по два логических блока (DD1, DD2) и D-триггер (DD4, DD5). Выходные сигналы блоков DD1 и DD2 могут быть дополнительно обработаны логическим блоком DD3.

Рисунок 9.12

В сравнении с FPGA, структура CPLD более «крупнозернистая». Рассмотрим ее на примере микросхем серии ХС9500, структурная схема которых приведена на рисунке 9.13, а сведения о составе — в таблице 9.4. Указанные там же максимальные частоты относятся к 16-разрядным двоичным счетчикам, которые реализованы на таких ПЛИС. Счетчики из элементов других ПЛИС способны работать на частотах до 350 МГц.

Рисунок 9.13

Таблица 9.4 - Данные о структуре серии ХС9500

| Микросхема | На кристалле находится | Максимальная частота счету, МГц | |

| Макроячейки | Вентили | ||

| ХС9536 | |||

| ХС9572 | |||

| ХС95108 | |||

| ХС95144 | |||

| ХС95216 | 111,1 | ||

| ХС95288 | 111,1 |

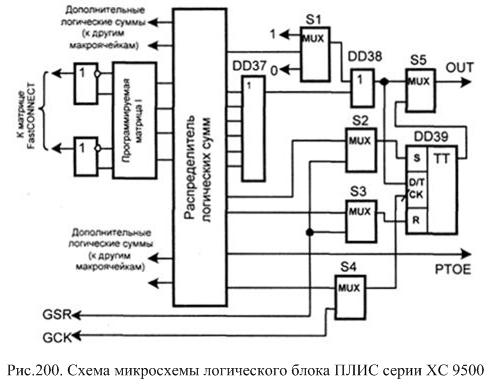

Схема макроячейки логического блока ПЛИС серии ХС9500 приведена на рисунке 9.14.

Рисунок 9.14

С помощью программируемой матрицы И формируют до пяти логических произведений 36-ти переменных, еще два произведения - можно взять от соседних макроячеек. На выходе ИЛИ элемента (DD37) образуется логическая сумма этих произведений, которая поступает на вход переключателя 55 и триггера DD39 в прямом или инвертированном виде в зависимости от положения программируемого переключателя S1. В одном из положений последнего инверсией управляет сигнал, сформированный в распределителе логических произведений. Тактовые сигналы из других выходов распределителя устанавливают и сбрасывают триггер DD39. Изменив положения переключателей S2—S4, эти функции можно выполнять с помощью глобальных сигналов синхронизации и сброса, которые поступают непосредственно из выводов ПЛИС.

|

|

|

В составе УВВ ПЛИС серии ХС9500 имеются только буферы ввода и вывода, триггеров в них нет. Перевести выход УВВ в активное состояние можно с помощью сигнала РТОЕ, который поступает от макроячейки, или одного из глобальных сигналов GOE1—GOE4, сформированных специальным программируемым логическим блоком из входных сигналов ПЛИС. Цепи OUT и РТОЕ каждой макроячейки ПЛИС CPLD связаны только с одним блоком ввода/вывода, который в свою очередь соединен с определенным внешним выводом. В FPGA такой жесткой связи нет.

Соединение функциональных блоков между собою и с входными цепями УВВ реализуют с помощью программируемой коммутационной матрицы, фирменное название которой FastCONNECT можно перевести как «быстрое соединение».

Матрица имеет структуру, которая обеспечивает одинаковую задержку распространения всех сигналов и, самое главное, гарантирует трассирование всех необходимых связей. Последнее позволяет произвольным образом распределять по выводам ПЛИС внешние цепи разрабатываемого устройства.

Приступая к проектированию устройства на ПЛИС, следует подготовить его схему с помощью любого из известных схемных редакторов, например, поулярного ORCAD.

Контрольные вопросы:

1. Какое назначение имеют ПЛМ?

2. Объяснить принцип работы ПЛМ.

3. Как осуществляется программирование ПЛМ?

4. Имеется ли возможность изменения старой информации на новую в ПЛМ?

5. Построить на ПЛМ схему устройства преобразующего двоичный код в десятичный.

6. Построить на ПЛМ схему мультиплексора с восьмью входами.

7. Привести пример условного графического обозначения ИМС ПЛМ и объяснить назначение всех выводов.

8. Область использования ПЛМ.

|

|

|