|

Передовые рубежи

|

|

|

|

Несмотря на все вышеизложенное, прямо сейчас уровень проектных норм, на котором ведутся разработки вычислительных платформ для космоса — это 65-45-22 нм. По 45 нм уже выпущен в серийное производство американский комплект микросхем RAD5500, по 28 нм в следующем году должен выйти европейский процессор DAHLIA, по 65 нм в бельгийском IMEC сейчас активно создается рассчитанная на долгосрочное применение платформа для разработки ASIC. Не отстают и российские разработчики — в дорожной карте НИИСИ РАН на будущий год значится выход радстойкого процессора на 65 нм, а публикации на эту тему говорят о создании платформы разработки, то есть у этих проектных норм большое будущее не только в Европе, но и в России.

И даже на этом уровне проектных норм развитие радстойкой электроники не останавливается — если посмотреть в свежие номера IEEE Transactions on Nuclear Science, там можно найти достаточно работ по изучению транзисторов с проектными нормами 20-16-14 нм, подготавливающих почву для новых поколений космических микропроцессоров. На таких проектных нормах разработчиков ожидает много нового и интересного: во-первых, нельзя сделать кольцевые транзисторы, во-вторых, в FinFET совсем другая геометрия канала и изоляции, в-третьих, есть FDSOI-технологии, в которых тоже достаточно специфики.

Уменьшение проектных норм, безусловно, влияет на радиационную стойкость изготавливаемых на них микросхем, но вовсе не обязательно в худшую сторону. Общий тренд состоит в том, что со снижением проектных норм влияние полной дозы уменьшается, а одиночных эффектов увеличивается. Сдвиг порогового напряжения в проектных нормах 180 нм и ниже измеряется в единицах или десятках милливольт даже для больших доз: подзатворный оксид такой тонкий, что накапливающийся в нем заряд туннелирует в канал вместо того, чтобы накапливаться. Переходной слой в технологиях с изоляцией STI достаточно компактный, что позволяет во многих случаях обеспечить низкие утечки при полной дозе в несколько десятков или даже сотен крад(Si). А если применить в глубоко субмикронной объемной технологии кольцевые транзисторы и охранные кольца, то мы разом избавимся от всех дозовых проблем.

|

|

|

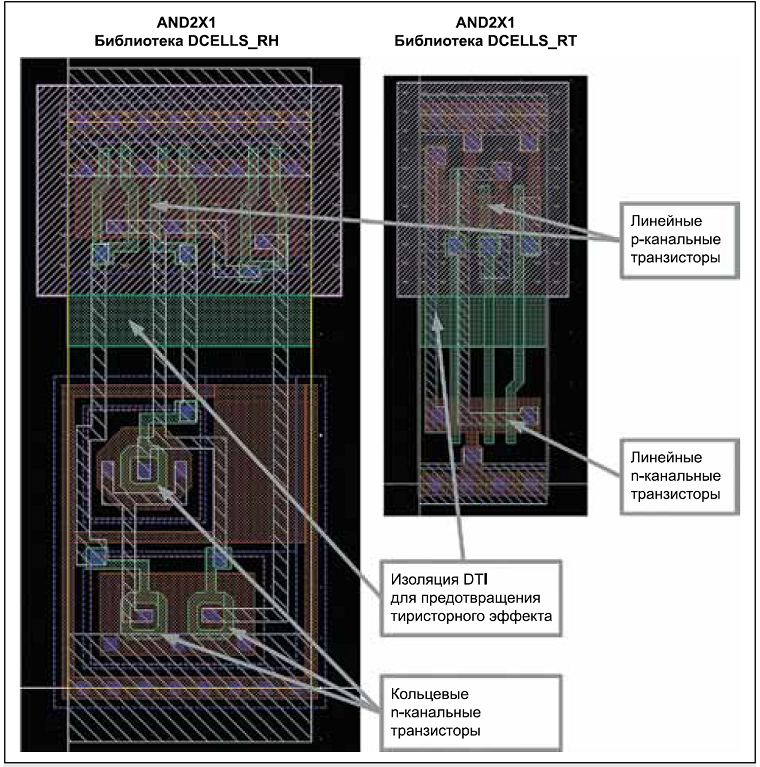

Рисунок 8. Примеры радиационностойких элементов AND разработки компании «Миландр» на технологии SOI BCD.

На рисунке 8 — два варианта реализации одного и того же логического элемента AND для разных условий. Слева мы видим полный фарш — кольцевые транзисторы в индивидуальных охранных кольцах. Справа — вариант попроще, для низкой полной дозы: транзисторы линейные, вместо охранных колец только хорошие контакты в земле. И в обоих случаях диэлектрическая изоляция n-канальных транзисторов от p-канальных, чтобы обезопасить микросхему от тиристорного эффекта. В объемной технологии эту функцию выполняют охранные кольца. При этом надо отметить, что для многих космических применений вполне достаточно стойкости к полной дозе на уровне 50-100 крад(Si), и линейные транзисторы прекрасно с этим справляются, не требуя существенно ухудшать функциональные параметры схемы ради достижения стойкости.

С одиночными сбоями ситуация такая: приблизительный диаметр области, из которой идет сбор заряда при попадании одиночной частицы — порядка одного микрона, то есть больше размеров ячейки памяти, выполненной по глубоко субмикронным проектным нормам. И действительно, экспериментально обнаруживаются так называемые множественные сбои, когда одна частица вызывает переключение сразу нескольких бит. Более того, с уменьшением проектных норм уменьшается и энергия, необходимая для переключения бита памяти, то есть к сбоям приводит большее количество попаданий, чем для чипов, выполненных по более грубым проектным нормам. В том числе — попадание альфа-частиц из радиоактивных примесей в конструкционных материалах.

|

|

|

Рисунок 9. Сравнение количества сбоев от попадания одиночной частицы для двух разных вариантов 6T SRAM в технологии с проектными нормами 65 нм. Источник — А. Балбеков и др., «Вопросы применимости СБИС по 65 нм КМОП технологии в условиях воздействия факторов космического пространства».

На рисунке 9 изображены экспериментальные данные по одиночным сбоям в объемной технологии 65 нм. Слева — обычная 6T-SRAM. Десять сбоев от одного попадания! От такого код Хэмминга вас не защитит. Так что, если мы говорим о коммерческих микросхемах, то на грубых проектных нормах с одиночными сбоями все будет несколько лучше, чем на тонких. По крайней мере, они останутся одиночными, и их будет реально исправить при помощи кодирования. Но если микросхема специально создается для космических применений, то в арсенале разработчика есть огромное количество архитектурных, схемных и топологических решений, способных обеспечить высокую стойкость одновременно с высокой производительностью. В правой части рисунка — тоже 6T-SRAM, с точно такой же электрической схемой, но с другой топологией. Цена улучшений, убирающих множественные сбои, тиристорный эффект и повышающих стойкость к полной дозе — четырехкратный рост площади. Звучит не очень приятно, но никто не говорил, что будет легко. Тем не менее, Radiation Hardening by Design работает и позволяет достигать заранее заданных показателей стойкости на маленьких проектных нормах на любой объемной технологии.

Почему заранее заданных? Потому что достижение разных уровней стойкости требует применения разных методов ее повышения, и для каждой технологии и технического задания нужный набор методов свой. Тогда почему бы не применять все сразу, чтобы точно было хорошо? Потому что достижение радиационной стойкости всегда происходит за счет ухудшения функциональных параметров (энергопотребления, площади кристалла, скорости и т. д. ), а они являются первым приоритетом. Именно поэтому нужны четкие требования технического задания, как по функциональности, так и по стойкости. Правда, микросхемы не так часто делаются для решения одной-единственной задачи, особенно радстойкие, у которых тираж для каждого из имеющихся применений может составлять несколько десятков штук. Но все же хорошее понимание требований позволяет, например, не использовать кольцевые транзисторы, сильно увеличивающие площадь и ток потребления, и получать в итоге более конкурентоспособные продукты.

|

|

|

Глаз внимательного читателя наверняка зацепился за слово «объемной» во фразе «заранее заданных показателей стойкости на маленьких проектных нормах на любой объемной технологии». Не лишнее ли оно там? Всем же известно, что радстойкие микросхемы нужно делать на технологии «кремний на изоляторе» или «кремний на сапфире».

Кремний на изоляторе

За технологией «кремний на изоляторе» давно и прочно закрепилась слава радиационностойкой. Корни этого популярного заблуждения уходят в седую древность, когда предшественник КНИ, кремний на сапфире, активно использовался для военных разработок. Почему? Транзисторы в такой технологии электрически отделены друг от друга и, что более важно, от подложки. Это означает, что область сбора радиационно-индуцированного заряда при кратковременном воздействии на чип излучения с высокой мощностью дозы, будет маленькой. Это, в свою очередь, существенно уменьшает время потери работоспособности — то, что нужно для работы в условиях атомной войны. И действительно, никакого другого метода снижения времени потери работоспособности, кроме полной диэлектрической изоляции, не существует.

Вторая важная часть мифа «КНИ = радстойкость» — это устойчивость к тиристорному эффекту, в том числе при воздействии с высокой мощностью дозы. Тиристорный эффект или «защелка» — чуть ли не главная головная боль разработчиков микросхем и приборов для космоса, и неудивительно, что технология, позволяющая от него избавиться, заслужила славу радиационностойкой. Но на самом деле ситуация опять несколько сложнее.

|

|

|

Рисунок 10. Сечение объемной КМОП-технологии с паразитным тиристором.

Причина возникновения тиристорного эффекта — паразитная тиристорная структура, присутствующая внутри элементов объемной КМОП-технологии. Если сопротивления Rs и Rw достаточно велики, то эта тиристорная структура при попадании заряженной частицы может открыться и закоротить землю чипа с питанием, что, сами понимаете, нехорошо. Насколько велики эти сопротивления в реальных микросхемах? Ответ на этот вопрос довольно прост: контакт к подложке или карману — это лишняя площадь, поэтому их количество стараются минимизировать. А это, в свою очередь значит, что по умолчанию тиристорный эффект в «обычной» микросхеме скорее будет, чем нет. Правда, тиристорный эффект может случиться не только от радиации, но и при воздействии, например, электростатического разряда или даже просто от повышенной температуры и большой плотности тока при неудачной топологии. В «обычных» применениях с тиристорным эффектом сталкиваются производители силовой и автомобильной электроники.

В значительной части космических систем вполне допустима перезагрузка в случае непредвиденных обстоятельств, то есть можно попробовать применить подверженный «защелке» чип, поставив в линию питания схему контроля тока потребления и сброса питания при превышении нормы. Это, собственно, регулярно и делается в ситуациях, когда очень надо применить высокопроизводительную коммерческую микросхему, а чипы защиты от тиристорного эффекта (Latchup Current Limiter) — довольно популярный радстойкий продукт. Но у такого решения есть много ограничений. Сбросить питание можно не везде и не всегда, перезагрузка в процессе выполнения важного маневра способна поставить крест на длительной миссии. Ток потребления современной микросхемы может различаться во много раз в зависимости от режима ее работы, то есть потребление в режиме «ничего не происходит и есть защелка» может быть меньше, чем в случае штатной работы в другом режиме. На какой уровень ставить ограничение тока? Тоже непонятно. Время, за которое нужно успеть отключить питание и предотвратить разрушение чипа, зависит от множества факторов, в том числе от конкретной микросхемы. Где-то можно никуда не спешить и сбрасывать питание столько раз, сколько будет нужно, а где-то уже после первого-второго раза чип все равно необратимо сгорает.

В микросхеме, выполненной по технологии КНИ, тиристорного эффекта не может быть в принципе, потому что все транзисторы электрически разделены. И самое лучшее — то, что для достижения стойкости к тиристорному эффекту не надо делать вообще ничего. То есть, коммерческие микросхемы, выполненные по технологии КНИ, тоже абсолютно устойчивы к нему, что сильно облегчает их применение в космосе. Так, например, коммерческий КНИ процессор будет управлять новым американским космическим кораблем «Орион».

|

|

|

Рисунок 11. Радиационно-индуцированные утечки в объемной КМОП-технологии. Источник — J. Schwank et. al., «Radiation effects in MOS oxides», IEEE TNS, Vol. 55, No. 4, 2008

В чем проблема? В том, что, кроме эффектов мощности дозы и «защелки», есть еще одиночные сбои и полная поглощенная доза, с которыми у КНИ-технологии все далеко не так радужно. На рисунке показаны два пути утечки в объемной КМОП-технологии. Оба этих пути легко закрываются при правильном топологическом проектировании — один использованием кольцевых n-канальных транзисторов, второй — при помощи охранных колец. Эти решения имеют недостатки с точки зрения функционирования схемы (ограничения на минимальный размер кольцевого транзистора, потери площади при использовании охранных колец), но с точки зрения обеспечения радиационной стойкости они очень эффективны.

Рисунок 12. Дополнительный механизм утечки в КНИ технологии.

В технологии КНИ есть еще один путь утечки из истока в сток по границе кремния и скрытого оксида. Скрытый оксид намного толще подзатворного, а значит, в нем может накопиться много положительного заряда. Если мы рассмотрим «нижний» транзистор (правая часть рисунка 12), для которого скрытый оксид является подзатворным, то увидим, что в нормальной ситуации напряжение «исток-затвор» этого транзистора — ноль, а его пороговое напряжение — несколько десятков вольт, то есть ток через этот транзистор не течет. При облучении в скрытом оксиде накапливается положительный заряд (на этот процесс влияет геометрия основного транзистора, в частности — толщина приборного слоя кремния), и пороговое напряжение «нижнего» n-канального транзистора падает. Как только оно падает ниже нуля, ток начинает свободно течь через транзистор по неуправляемому нижнему каналу. Таким образом, с точки зрения полной поглощенной дозы технология КНИ принципиально строго хуже объемной технологии. Но, может быть, есть способ как-то исправить положение?

Обычно подложка микросхемы заземлена, но ведь в КНИ нам ничего не мешает подать на нее не землю, а отрицательное напряжение и таким образом закрыть нижний транзистор? С одной стороны, идея здравая и она активно используется. Причем в случае с полностью обедненным КНИ (FDSOI) и нормами 45-28 нм контроль потенциала под скрытым оксидом используется и при нормальном функционировании. С другой стороны, электрическое поле в скрытом оксиде не только закрывает паразитный транзистор, но и ускоряет накопление положительного заряда в скрытом оксиде. В итоге, в зависимости от параметров техпроцесса и величины приложенного отрицательного напряжения, дозовая стойкость микросхемы с поданным на подложку отрицательным напряжением может не только не улучшиться, но и стать хуже! Дальше, как это обычно водится, есть тонкости, но принципиально ситуация состоит в том, что топологические и схемотехнические методы на объемной технологии позволяют добиться практически любых разумных уровней стойкости к полной дозе, и под «разумными уровнями» я здесь понимаю, скажем 100 Мрад(Si). На КНИ же существуют фундаментальные ограничения, и уровень стойкости конкретного техпроцесса может быть достаточно низким. Обойти эти ограничения без вмешательства в технологию (обычно недоступного из коммерческих соображений) никак нельзя, и узнать параметры дозовой стойкости без дорогостоящих испытаний тоже не получится.

Ничуть не менее интересна и ситуация с одиночными сбоями в КНИ. С одной стороны, в КНИ гораздо меньше объем, из которого собирается выделившийся при попадании ионизирующей частицы заряд (хотя насчет точной формы этого объема много лет идут споры между ведущими учеными). С другой стороны, подзатворная область («тело») КНИ МОП транзистора настолько мала, что попадание в нее даже небольшого заряда способно существенно поднять напряжение в ней. Если напряжение поднимется достаточно высоко для открывания pn-перехода исток-тело, то включится паразитный биполярный транзистор исток-тело-сток, и заряд, внесенный ионизирующей частицей, умножится на коэффициент усиления этого транзистора. На практике это означает падение пороговой ЛПЭ до уровней ниже 1 МэВ*см^2/(мг), то есть к сбою приводит попадание в микросхему чего угодно. Конечно же, с паразитным тиристорным эффектом в КНИ можно справиться — присоединив подзатворную область к истоку транзистора или к земле/питанию. Но, во-первых, этого никто не делает в коммерческих микросхемах (потому что нет необходимости), а во-вторых, контакт к телу — это потеря площади, особенно чувствительная для ключей, где он должен быть независимым. В каждой ячейке кэш-памяти как минимум два ключа, что приводит к значительному росту площади кэша и кристалла в целом. В то же самое время в объемной технологии для подавления тиристорного эффекта и паразитного биполярного эффекта может быть достаточно одного контакта на 4-8 ячеек памяти, да и даже охранные кольца можно сделать с меньшими потерями площади, чем на контакты к телу транзистора в КНИ. Важным преимуществом КНИ в глубоко субмикронных технологиях является то, что диэлектрическая изоляция предотвращает распространение заряда и множественные сбои с большой кратностью, которые могут появляться в объемной технологии. Однако, размер трека ионизирующей частицы сравним с размерами ячейки памяти, и двойные сбои в КНИ вполне себе регистрируются.

Итого ситуация с радиационной стойкостью технологии «кремний на изоляторе» выглядит таким образом, что она не «радиационно стойкая сама по себе», а имеет ряд преимуществ и ряд недостатков относительно объемной технологии. Часть недостатков КНИ можно обойти при помощи специальных приемов проектирования, но то же самое можно сделать и в объемной технологии. Поэтому при выборе коммерческой микросхемы для использования в условиях воздействия радиации нельзя полагаться на КНИ как на панацею, а при выборе технологии для разработки специализированной радстойкой СБИС надо тщательно взвешивать все «за» и «против» КНИ и объемной технологии для решения конкретной задачи и обеспечения требуемых уровней стойкости к различным радиационным эффектам.

Заключение

Над обеспечением радиационной стойкости интегральных микросхем работают сотни тысяч специалистов по всему миру, и объять необъятное одной научно-популярной статьей невозможно. Да это и тема не для статьи и даже не для диссертации. Во всяком случае, не для кандидатской диссертации. В силу специфики формата, коллеги-специалисты найдут здесь достаточно упрощений, неточностей и может даже фактических ошибок. Хотелось бы, чтобы нет, но сообщения о необходимых правках принимаются в личку. Не претендуя на полноту и новизну, я надеюсь, что справился с тем, чтобы наглядно описать самые популярные связанные с радиационной стойкостью вопросы и заблуждения, а также донести до читателя мысль, что микроэлектроника вообще и космическая микроэлектроника в частности — одна из самых быстро прогрессирующих областей науки и техники, поэтому проверенные временем знания и стереотипы на поверку часто оказываются устаревшими, неполными или неправильными, а простые и очевидные рецепты никто не использует, потому что на самом деле их не существует.

Теги:

|

|

|