|

Метод принудительного задания коэффициентом пересчета в вычитающем счетчике

|

|

|

|

Пусть состояния вычитающего счетчика изменяется от (N-1) до 0, тогда очевидно, что его коэффициент пересчета равен N. Коэффициент пересчета можно уменьшить до значения M< N, если после появления нулевой комбинации на выходе записывать в вычитающий счетчик код М-1.

Рассмотрим особенности реализации на вычитающих счетчиках с последовательным и параллельным переносом.

Алгоритм построения ДПКД на вычитающем счетчике с последовательным переносом:

1. Разрабатывают вычитающий счетчик с коэффициентом пересчета M< N.

2. Разрабатывают узел детектирования единичного состояния счетчика для формирования сигнала установки.

3. Контролируют отсутствие паразитных импульсов в сигнале установки. При наличии паразитных импульсов анализируют времена задержки распространения сигналов, поступающих на входы узла детектирования нулевого состояния, и затем устанавливают элементы задержки по критическим цепям.

4. Заводят сигнал установки на входы R тех триггеров, которые необходимо перевести в единичное состояние. На входы S этих триггеров заводят сигнал установки в начальное состояние.

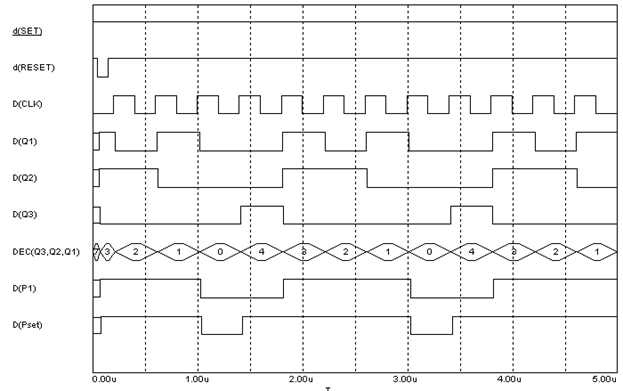

На рисунках 1.13 и 1.14 показаны ДПКД с коэффициентом пересчета 6 и временные диаграммы его работы.

Рисунок 1.13 – Схема ДПКД с коэффициентом пересчета 5 на вычитающем счетчике

Рисунок 1.14 – Временные диаграммы работы ДПКД на вычитающем счетчике

К особенностям такого ДПКД можно отнести следующее:

- узел детектирования нулевого состояния наиболее просто реализовать на элементах ИЛИ, поскольку в этом случае в выходном сигнале отсутствуют паразитные импульсы;

- длительность сигнала Pset незначительна и зависит от параметров примененной элементной базы, что в ряде случаев может привести к сбоям в работе ДПКД.

|

|

|

Для обеспечения надежности работы ДПКД импульс Pset следует формировать с помощью дополнительного RS-триггера. В этом случае длительность сигнала Pset равна половине периода сигнала синхронизации.

В вычитающих счетчиках с параллельным переносом детектируют нулевое состояние, и сигнал Pset подают на входы R тех триггеров, состояния которых не должно измениться по приходу очередного синхросигнала. На входы S этих триггеров заводят сигнал установки в начальное состояние (см. рисунок 1.15).

Из анализа временных диаграмм следует, что длительность сигнала Pset равна периоду входного сигнала синхронизации (см. рисунок 1.16).

Рисунок 1.15 – Схема ДПКД с коэффициентом пересчета 5 на вычитающем счетчике с параллельным переносом

Рисунок 1.16 – Временные диаграммы работы ДПКД на вычитающем счетчике с параллельным переносом

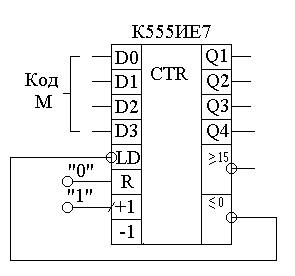

Схемы счетчиков-делителей на реверсивных счетчиках отличаются простотой, а также удобством формирования кода, подаваемого на входы предварительной установки.

Наиболее простой реализацией характеризуются ДПКД на основе стандартной микросхемы К555ИЕ7 (см. рисунок 1.17).

Рисунок 1.17 – Схема счетчика-делителя на реверсивном счетчике

Синтез счётчиков на JK-, D- и T-триггерах

Этот метод основан на теории цифровых автоматов и предполагает выполнение следующих операций.

|

1. Составляют структурную модель счетчика, которая в общем случае имеет вид, приведенный на рисунке 1.18.

Рисунок 1.18 – Структурная модель счётчика

2. Составляют расширенную таблицу истинности.

3. Получают выражение для выходного сигнала комбинационной схемы, при необходимости, и входных сигналов триггеров.

4. Реализуют полученные выражения с помощью известных логических элементов.

|

|

|