|

Часы, счетчики времени, календари

|

|

|

|

Часы, счетчики времени, секундомеры, таймеры календари обычно выполняются на базе счетчиков, считающих в заданных пределах. Например, для счетчика минут нужны счетчики считающие от 0 до 5 и от 0 до 9, а для счетчика часов соответственно двоично-десятичный счетчик считающий от 0 до 23. Для управления работой устройств (установки, сброс, пуск и т.д.) используются дополнительные схемные узлы, управляющие работой счетчиков.

Рассмотрим несложную схему часов, описание которой на языке AHDL представлено ниже

SUBDESIGN WATCHMH

(CLK, CLKU, RN, MIN, HOURS:INPUT;

Q[6..0],H[5..0]:OUTPUT;

)

Variable

ME[3..0],RP: DFF;

MD[2..0]: DFF;

HE[5..0]: DFF;

BEGIN

RP.CLK=!CLK;

ME[].CLK=CLK&!MIN&!HOURS # CLKU&MIN;

MD[].CLK=!ME[3].Q;

ME[].CLRN=RN;

MD[].CLRN=RN;

HE[].CLRN=RN;

HE[].CLK=!RP&!HOURS # CLKU&HOURS;

CASE ME[].Q IS

WHEN 9 => ME[].D=0;

WHEN OTHERS => ME[].D=ME[].Q+1;

END CASE;

CASE MD[].Q IS

WHEN 5 => MD[].D=0; RP.D=B"1";

WHEN OTHERS => MD[].D=MD[].Q+1; RP.D=B"0";

END CASE;

CASE HE[].Q IS

WHEN 9 => HE[].D=H"10";

WHEN H"19" => HE[].D=H"20";

WHEN H"23" => HE[].D=0;

WHEN OTHERS => HE[].D=HE[].Q+1;

END CASE;

Q[6..4] = MD[].Q;

Q[3..0] = ME[].Q;

H[] = HE[].Q;

END;

. содержащую регистр минут и регистр часов.

Схема имеет следующие входные и выходные сигналы.

СLK - тактовый вход минут, имеющий частоту 1/60 Гц;

CLKU - тактовый вход установок, имеющий частоту 1 Гц;

MIN - вход установки минут;

HOURS - вход установки часов;

RN -вход сброса;

Q[6..0] - выходы двоично-десятичного счетчика минут;

H[5..0] - выходы двоично-десятичного счетчика часов.

В рабочем режиме на входы MIN и HOURS поданы сигналы «0». При нажатии кнопки MIN, работа часов приостанавливается и начинается меняться показание минут в темпе частоты коррекции CLKU. Аналогичным образом, при нажатии кнопки HOURS происходит установка текущего значения часов.

Информация о текущем значении минут хранится в регистрах ME[3..0 ] – единицы минут, MD[2..0] - десятки минут. Информация о текущем значении часов хранится в регистре HE[5..0]. HE[3..0] – единицы часов, HE[5..4] – десятки часов.

|

|

|

В рассматриваемом описании часов на базе вышеуказанных регистров организованы двоично-десятичные счётчики. Счётчик на базе регистра ME[3..0 ]

считает от 0 до 9, счетчик на базе регистра MD[2..0] считает от 0 до 5 а счетчик на базе регистра HE[5..0] обеспечивает двоично-десятичный счёт от 0 до 23.

Для обеспечения правильного счёта во всём диапазоне значений и отработки режимов установки для управляющих тактовых сигналов используются достаточно сложные логические выражения:

ME[].CLK=CLK&!MIN&!HOURS # CLKU&MIN;

MD[].CLK=!ME[3].Q;

HE[].CLK=!RP&!HOURS # CLKU&HOURS;

Логическое выражение для ME[].CLK обеспечивает счёт минут от стандартного генератора CLK в рабочем режиме и от генератора установки CLKU в режиме установки минут (при нажатии кнопки MIN).

Логическое выражение для HE[].CLK обеспечивает счёт часов от входа переноса счётчика минут RP в стандартном режиме работы и от генератора установки CLKU в режиме установки часов (при нажатии кнопки HOURS).

Логическое выражение для MD[].CLK обеспечивает счёт десятков минут от выхода переноса счётчика единиц минут ME[3].Q.

Ниже, на рисунке 4.5.1. приведён фрагмент временной диаграммы работы часов.

Рис 4.5.1. Фрагмент временной диаграммы работы часов.

На временной диаграмме, представленной на рис 4.5.1. показан момент окончания установки минут (сигнал MIN переходит из состояния “1” в состояние “0”), один рабочий такт (момент 750.0 ns) и начало установки часов (сигнал HOURS переходит из состояния “0” в состояние “1”).

Схемы секундомеров проектируются аналогичным образом. Они, обычно, не имеют сигналов установки, но имеют кнопки «старт» и «стоп». При подаче единичного сигнала на вход «старт» регистры времени сбрасываются в «0» и начинается отсчет времени. При подаче единичного сигнала на вход «стоп» отсчет времени прекращается.

|

|

|

Схемы таймеров позволяют отсчитывать заданные интервалы времени. Они работают в реверсивном режиме (считают время в обратном порядке) имеют входы установки заданного времени, вход начала работы. По окончании отсчета времени они подают «1» на исполнительный вывод, определяющий окончание отсчета временного интервала.

Рассмотрим несложную схему таймера минут, описание которой приведено ниже:

SUBDESIGN TIMER

(CLK, CLKU, UST, START, RN:INPUT;

Q[6..0], SQ,S:OUTPUT;

)

Variable

ME[3..0]: DFF;

MD[2..0]: DFF;

WT: DFF;

WM: DFF;

BEGIN

WT.D=VCC;

WT.CLK=START;

WM.CLK=CLK;

WM.CLRN=RN;

WT.CLRN=RN&!WM.Q;

ME[].CLK=CLK &!UST & SQ # CLKU & UST;

MD[].CLK=ME[3].Q;

ME[].CLRN=RN;

MD[].CLRN=RN;

SQ=WT.Q;

S=WM.Q;

IF WT.Q==1 THEN

CASE ME[].Q IS

WHEN B"0000" => ME[].D=9;

WHEN OTHERS => ME[].D=ME[].Q-1;

END CASE;

MD[].D=MD[].Q-1;

END IF;

IF WT.Q==0 THEN

CASE ME[].Q IS

WHEN 9 => ME[].D=0;

WHEN OTHERS => ME[].D=ME[].Q+1;

END CASE;

CASE MD[].Q IS

WHEN 5 => MD[].D=0;

WHEN OTHERS => MD[].D=MD[].Q+1;

END CASE;

END IF;

IF ME[].Q==1 & MD[].Q==0 & WT.Q==1 THEN

WM.D=B"1";

ELSE WM.D=B"0";

END IF;

Q[6..4] = MD[].Q;

Q[3..0] = ME[].Q;

END;

Схема таймера имеет следующие входные и выходнын сигналы.

СLK - тактовый вход минут, имеющий частоту 1/60 Гц;

CLKU - тактовый вход установок, имеющий частоту 1 Гц;

UST – кнопка установки таймера;

START – кнопка запуска таймера;

RN -вход сброса;

S -выход сигнала на исполнительный механизм;

SQ -выход триггера управления (вспомогательный выход);

Q[6..0] - выходы двоично-десятичного счетчика минут;

Представленный таймер имеет в своём составе регистр счётчика минут, который может считать импульсю как по возрастанию (режим установки) так и по убыванию (режим счёта).

Для управления режимами работы служит триггер WT. В режиме ожидания триггер WT находится в нулевом состоянии. В этом режиме при нажатии кнопки UST счетчик минут начинает считать в прямом порядке импульсы с частотой CLKU, тем самым происходит установка начального значения таймера. При приходе положительного фронта сигнала START триггер перебрасывается в состояние «1», поскольку на вход этого триггера постоянно подаётся напряжение высокого логического уровня. Перейдя в состояние логической единицы триггер WT переводит схему в режим счёта импульсов по убыванию с частотой СLK.

После того, как счётчик досчитает до кода «000000», в выходной триггер WM записывается сигнал «1», а триггер WT перебрасывается в состояние «0» и схема опять переходит в режим ожидания.

|

|

|

Управление режимами счёта организовано с помощью условного оператора IF THEN. Внутри операторов находятся вложенные операторы CASE, которые и организовывают двоично-десятичный счёт минут.

Операторы

WT.CLK=START;

WM.CLK=CLK;

определяют тактовые сигналы, которые подаются на входы триггеров управления WT и WM.

Оператор

WT.CLRN=RN&!WM.Q;

определяет условия сброса триггера WT.

Операторы

ME[].CLK=CLK &!UST & SQ # CLKU & UST;

MD[].CLK=ME[3].Q;

определяют правила подачи тактовых сигналов на младшие ME[].CLK и старшие MD[].CLK разряды счётчика минут. Из этих выражений видно, что на тактовый вход ME[].CLK поступают импульсы CLKU при сигнале UST равном логической единице и соответственно импульсы CLK при сигнале UST равном логическому нулю и сигнале SQ равному логической единице.

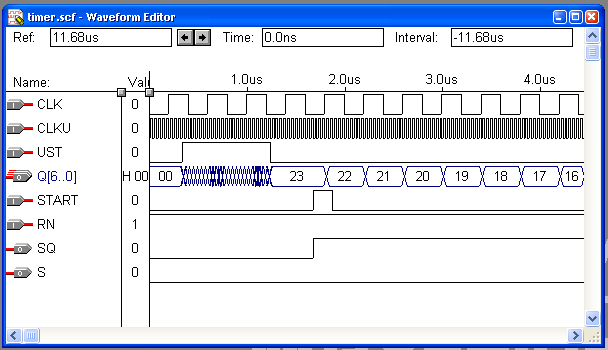

Примеры временной диаграммы работы таймера приведён на рис 4.5.2. и 4.5.3.

Рис 4.5.2. Примеры временной диаграммы работы таймера (установка начального значения и начало счёта).

На рисунке 4.5.2. показа первая фаза работы таймера. При подаче единичного сигнала на вход UST таймер с частой CLKU досчитывает до числа 23. Затем при подаче логической единицы на вход START таймер переходит в режим рабочего счёта.

Рис 4.5.3. Примеры временной диаграммы работы таймера (окончание счёта).

На рисунке 4.5.3. показа вторая фаза работы таймера. Досчитав до нулевого значения таймер выдаёт единичный сигнал на выход управления исполнительным механизмом S и переводит таймер в режим ожидания (сигнал SQ сбрасывается в логический «0»)

Схемы календарей строятся аналогично схемам часов. Они, обычно имеют регистры дней, месяцев, лет. Для этих регистров, как правило, предусматривается раздельная установка значений. Для обеспечения правильного отсчета дней применяются двоично десятичные счетчики с достаточно сложным управлением, поскольку разные месяцы имеют различное количество дней.

Частотомеры

|

|

|

Достаточно широко распространённым узлом микросхем являются частотомеры, позволяющие измерять частоту входного сигнала. Одним из возможных вариантов таких схем являются частотомеры, работающие по принципу сравнения частоты входного сигнала с опорной, эталонной частотой.

Существует несколько подходов к построению частотомеров. В частности при интегральном методе, опорная частота выбирается очень низкой, например, 0.5Гц и подсчитывается число периодов, входной частоты, укладывающихся в один полупериод опорной частоты. Такой подход позволяет построить наиболее простые схемы, представляющие собой фактически счётчики с несложным управлением.

Недостатками такого подхода являются: невысокая точность для входных сигналов с небольшой частотой и относительно большое время работы. Этот метод может применятся для измерения очень высоких частот – фактически на пределе срабатывания счётных триггеров. Для работы с очень высокими частотами опорная частота может быть также увеличена Так, например, для измерения частот в сотни мегагерц можно с успехом применять опорную частоту в десять килогерц, что обеспечит погрешность определения частоты менее 0.01%.

При интегральном подходе измеряемая частота Fv определяется соотношением

Fv= n, где n число периодов входной частоты, укладывающейся в

полупериод опорной.

Для определения частот низкочастотных сигналов иногда применяется метод измерения периода. При таком подходе опорная частота выбирается очень высокой и подсчитывается число импульсов опорной частоты, укладывающихся в полупериоде входной частоты.

Если опорная частота равна F, а число импульсов, укладывающихся в полупериоде входной частоты равно n. Тогда значение входной частоты Fv определяется выражением:

Fv=F/n

Для определения Fv требуется операция деления, что приводит к достаточно громоздким схемотехническим решениям. Однако современные библиотеки САПР обычно имеют готовые модули, реализующие операцию деления. Так что это не является сложной проблемой.

Интегральные частотомеры.

Это наиболее простой и широко распространённый тип частотомеров.

Рассмотрим схему интегрального измерителя частот, представленную на

рис 4.6.1.

Рис. 4.6.1. Структурная схема интегрального частотомера.

Схема частотомера имеет следующие входные и выходные сигналы.

СLKOP - тактовый импульсы опорной частоты равной 1 кГц;

CLKIN – вход неизвестной, измеряемой частоты;

RH[3..0] – старшие разряды регистра частоты;

RS[3..0] – средние разряды регистра частоты;

RM[3..0] – младшие разряды регистра частоты.

|

|

|

.Опорная частота выбрана равной 1 МГц, поэтому входные частоты будут измеряться в мегагерцах.

Интегральный частотомер состоит из трех тетрадного двоично десятичного счетчика count3 и схемы управления, реализованной на элементе 2И сбрасывающей и запускающей счётчик при положительном фронте входной частоты и останавливающей при отрицательном.

Для индикации показаний в схеме введен двенадцати разрядный регистр, состоящий из трех четырехразрядных регистров reg4. Этот регистр фиксирует отсчитанные значения измеряемой частоты, давая возможность выводить показания на выходной цифровой индикатор. Наличие этого регистра позволяет выдавать на выходной индикатор конечные значения отсчитанной частоты, полученные по окончании каждого отсчёта. В его отсутствие на выходном индикаторе происходила бы очень быстрая схема показаний, так что человеку было бы практически невозможно отслеживать полученные результаты.

Двоично-десятичный счетчик count3, выполняющий функции подсчёта числа импульсов измеряемой частоты,разработан на языке AHDL. Для обеспечения непосредственной выдачи результатов расчёта, например, на жидкокристаллический или светодиодный индикатор, работа счётчика организована по двоично-десятичной схеме, при которой мы сразу имеем все десятичные цифры для индикации.

Описание счётчика count3 имеет следующий вид:

SUBDESIGN COUNT3

(CLK, RN:INPUT;

M[3..0], S[3..0], H[3..0]:OUTPUT;

)

Variable

MT[3..0]: DFF;

ST[3..0]: DFF;

HT[3..0]: DFF;

BEGIN

MT[].CLK=CLK;

ST[].CLK=!MT[3].Q;

HT[].CLK=!ST[3].Q;

MT[].CLRN=RN;

ST[].CLRN=RN;

HT[].CLRN=RN;

CASE MT[].Q IS

WHEN 9 => MT[].D=0;

WHEN OTHERS => MT[].D=MT[].Q+1;

END CASE;

CASE ST[].Q IS

WHEN 9 => ST[].D=0;

WHEN OTHERS => ST[].D=ST[].Q+1;

END CASE;

CASE HT[].Q IS

WHEN 9 => HT[].D=0;

WHEN OTHERS => HT[].D=HT[].Q+1;

END CASE;

M[] = MT[].Q;

S[] = ST[].Q;

H[] = HT[].Q;

END;

Схема счётчика имеет следующие входные и выходные сигналы.

СLK – входная частота;

RN – асинхронный сброс;

H[3..0] – выходы старшей тетрады частоты;

S[3..0] – выходы средней тетрады счётчика;

M[3..0] – выходы младшей тетрады счётчика.

В состав счетчика входит регистр младшей тетрады MT[3..0], средней тетрады MS[3..0], и старшей - MH[3..0 ].

Условия двоично-десятичного счёта отрабатываются с помощью группы операторов CASE, расписанных отдельно для каждой тетрады.

Нижеприведённые операторы обеспечивают отработку сигналов переноса между тетрадами:

MT[].CLK=CLK;

ST[].CLK=!MT[3].Q;

HT[].CLK=!ST[3].Q;

Младшая тетрада считает импульсы непосредственно входной частоты, средняя – импульсы переноса младшей, а старшая – импульсы переноса средгнй.

Регистр для хранения результатов подсчёта частоты реализован на базе триггеров DFF. Схема четырехразрядного регистра представлена на рис 4.6.2.

Рис 4.6.2. Схема четырехразрядного буферного регистра.

Схема регистра имеет следующие входные и выходные сигналы.

СLK – входной тактовый сигнал записи данных;

D0[3..0] – входные сигнала регистра;

Q0[3..0] – выходные сигналы регистра;

По положительному фронту входного тактового сигнала СLK регистр записывает входные данные, заданные на шине D0[3..0] и хранит их вплоть до прихода очередного импульса тактового сигнала.

Временная диаграмма работы частотомера приведена на рис 4.6.3

Рис 4.6.3. Временная диаграмма работы частотомера.

На рисунке 4.5.3. представлен пример работы частотомера при измерении входной частоты 50 Мгц. Во втором цикле измерения из входного потока «вырезали» три рабочих такта, поэтому в результате получилась частота 47 МГц.

|

|

|