|

With(lpm_widtha, lpm_widthb, lpm_widthp,

|

|

|

|

LPM_WIDTHS, LPM_REPRESENTATION,

LPM_PIPELINE, LATENCY, INPUT_A_IS_CONSTANT,

INPUT_B_IS_CONSTANT)

RETURNS (RESULT[LPM_WIDTHP-1)..0]);

Пример непосредственного обращения к модулю

RESULT[7..0]= lpm_mult(.dataa[]=a[],(.datab[]=b[])

WITH

(LPM_WIDTHA=4, LPM_WIDTHB=4, LPM_WIDTHS=8);

Модуль MULT.

MULT – это модуль верхнего уровня в иерархии описаний умножителя, выводы этого модуля соответствуют выводам умножителя.

Рекомендации по порядку разработки схемы.

Разработку схемы умножителя рекомендуется вести помодульно, тщательно отрабатывая схемотехнику каждого узла.

Для отработки каждого модуля необходимо подготовить сценарий, разработать временную диаграмму, обеспечивающую перебор всех вариантов работы аппаратуры. Провести логическое моделирование, тщательно проанализировать временную диаграмму.

После отработки схемотехники отдельных модулей можно приступать к созданию проекта головной схемы и его логическому моделированию.

Проектирование схем с магистральным вводом выводом данных

В настоящее время одной из серьёзных проблем при разработке аппаратуры является проблема уменьшения количества выводов БИС и упрощения разводки печатных плат. Особенно остро эта проблема стоит в случае работы с много разрядными шинами данных, размерность которых нередко достигает 64, 128 а иногда и 256 разрядов.

Одним из возможных путей решения этой проблемы является использование магистральной передачи данных, при которой к одной, много разрядной шине подключаются несколько приёмников и источников а передача данных между ними осуществляется в различные моменты времени.

Правила работы с магистралью, арбитр.

Работу с магистралью обычно осуществляют с помощью специальных узлов - шинные приёмо-передатчиков, которые собственно и позволяют организовать передачу и приём информации между несколькими источниками и приёмниками по общей шине данных.

|

|

|

В каждый момент времени на общей шине данных может быть активен только один источник сигнала. Управлением работой шинных формирователей осуществляет специальное логическое устройство, называемое арбитром.

При разработке шинных приёмо-передатчиков приходится иметь дело с выводами, которые в одни моменты времени являются входами, а в другие – выходами. Такие выводы называются двунаправленными, в САПР MAX+PLUSII эти выводы имеют тип BIDIR.

Работа с двунаправленными выводами в САПР MAX+PLUSII организуется с помощью элемента TRI, имеющего вход, выход и сигнал управления. Условное обозначение элемента приведено на рис 5.1.1.

OE

|

|

|  |

IN OUT

Рис 5.1.1. Схемотическое обозначение магистрального элемента TRI.

Элемент TRI имеет следующую логику работы. Если сигнал OE равен логической единице, то информация с входа IN проходит на выход OUT. Если сигнал OE равен логическому нулю, то независимо от информации на входе IN выход OUT находится в высокоимпедансном состоянии (отключен). Такое состояние обозначается как «Z».

Рассмотрим несложный пример приёмопередатчика, работающего с магистралью, представленный на рис 5.1.2.

|

Рис 5.1.2. Пример приёмопередатчика, работающего с магистралью,

Представленный приёмопередатчик имеет следующие входные и выходные сигналы:

IN[2..1] – входная шина данных;

DB[2..1 – двунаправленная шина данных;

CS – вход разрешения работы

ADR – вход выбора направления передачи;

OUT[2..1] -выходная шина данных.

Данная схема имеет следующую логику работы.

При CS=0 работа запрещена, выходная шина OUT[2..1] и двунаправленная шина DB[2..1] находятся в состоянии «Z».

|

|

|

При CS=1 работа разрешена, состояние шина OUT[2..1] и DB[2..1] определяется сигналом на входе ADR.

При CS=1 и ADR=0 данные передаются с шины DB[2..1] на шину OUT[2..1].

При CS=1 и ADR=1 данные передаются с шины IN[2..1] на шину DB[2..1].

Схему, представленную на рис 5.1.2. можно, естественно, описать на поведенческом уровне на языке AHDL. При этом описание будет иметь следующий вид.

SUBDESIGN SHIN2

(IN[2..1],CS,ADR: INPUT;

OUT[2..1]: OUTPUT;

DB[2..1]:DIDIR;

)

VARIABLE

TRI_B[2..1]:TRI;

TRI_OUT[2..1]:TRI;

BEGIN

CASE (CS,ADR) IS

WHEN B”10” => TRI_OUT[].OE=VCC;

WHEN B”11” => TRI_B[].OE=VCC;

END CASE;

TRI_B[].IN=IN[];

TRI_OUT[].IN=DB[];

DB[]=TRI_B[].OUT;

OUT[]=TRI_OUT[].OUT;

END

В приведённом текстовом описании выводы группы DB[2..1] имеют тип BIDIR.

В разделе VARIABLE объявлены две переменные TRI_B и две переменные TRI_OUT каждая из которых обозначает примитив буфера с тремя состояниями TRI.

Таким образом, компилятору явно указывается, что на соответствующих выводах БИС следует использовать буферы с тремя состояниями.

Выводы CS и ADR образуют временную группу, оцениваемую в операторе CASE. Заметим, чтопри CS=0 и произвольном сигнале на входе ADR, значения логических функций TRI_B[] и TRI_OUT[] явно не определены.

По умолчанию их значения на данных наборах аргументов – логический нуль. Поэтому при CS=0 все буферы TRI будут находится в состоянии «Z».

Комбинационная схема, имеющая управляющие входы CS и ADR и управляющая логикой работы с магистралью фактически является арбитром.

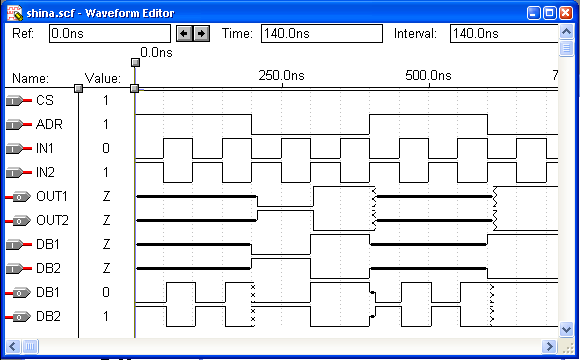

Результаты моделирования приёмопередатчика приведены на рис 5.1.3.

|

Рис 5.1.3. Результаты моделирования работы приёмопередатчика.

|

|

|