|

Технология Hyper-Threading

|

|

|

|

Технология Intel Hyper-Threading (HT) поддерживается специфичными членами семейств Intel Xeon (Nocona) и Intel Pentium (Prescott). Технология позволяет приложениям пользоваться преимуществами параллелизма, представляемыми на уровне заданий или потоков несколькими логическими процессорами внутри одного физического. В своей первой реализации в процессоре Intel Xeon, НТ представляла один физический процессор как два логических. Эти два логических процессора имеют полный набор архитектурных регистров, разделяя ресурсы одного физического процессора. Имея архитектуру двух процессоров, НТ встроенная в процессор выглядит как два процессора для приложений, операционных систем и программного кода.

При помощи распределения ресурсов, при пиковых запросах, между двумя логическими процессорами, НТ хорошо подходит для многопроцессорных систем, производя дополнительное увеличение мощности по сравнению с обычными многопроцессорными системами.

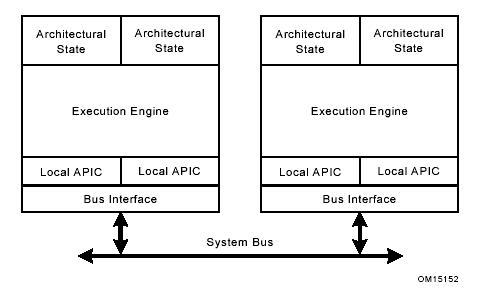

Рисунок 6 показывает типичную шинно-основанную симметричную многопроцессорную систему (SMP), основанную на процессорах поддерживающих технологию НТ. Каждый логический процессор может выполнять программный поток, позволяя двум потокам выполняться одновременно в одном физическом процессоре.

В технологии НТ физические ресурсы делятся, а архитектурная модель дублируется для каждого логического процессора. Это минимизирует потери от мертвых зон, при достижении целей много потоковых приложений или многозадачных платформ.

Рисунок 5. Технология Hyper-Threading на SMP

Производительный потенциал НТ основывается:

· на факте, что операционная система и пользовательские приложения могут закреплять потоки или процессы за логическими процессорами каждого из физических процессоров.

|

|

|

· Возможности к использованию исполнительных ресурсов кристалла на более высоком уровне, чем когда один поток потребляет все исполнительные ресурсы

Ресурсы процессора и технология Hyper-Threading

Большинство микроархитектурных ресурсов физического процессора делятся между логическими процессорами. Только некоторые небольшие структуры данных дублируются для каждого логического процессора. В этом разделе описывается, как ресурсы разделяются, делятся или реплицируются.

Реплицированные ресурсы

Архитектурная модель дублируются для каждого логического процессора. Архитектурная модель состоит из регистров используемых операционной системой и программного кода контролирующего взаимодействие программ и хранение данных для вычислений. Эта модель включает восемь регистров специального назначения, контролирующие регистры, регистры отладки и т.д. За исключением MTRRs – регистров (memory type range registers) и ресурсов мониторинга за производительностью

Остальные ресурсы, такие как указатели инструкций, таблицы переименований регистров, реплицируются для одновременного слежения за выполнением и изменениями в логических процессорах. Предсказатель стека возвратов реплицируется для улучшения предсказания ветвлений инструкций возврата.

В дополнение реплицируются несколько буферов (например, двух входные буферы потоковых инструкций), для снижения нагрузки.

Разделенные ресурсы

Несколько буферов делятся пополам между процессорами. Они относятся к разделенным ресурсам. Причины этого деления:

· Операционная равнодоступность

· Возможность операций одного логического процессора не зависеть от зависших операций другого логического процессора

Промах кэша, неверное предсказание ветвления или зависимости инструкций могут помешать логическому процессору работать на полной мощности в течение некоторого числа циклов. Разделение предотвращает зависший логический процессор от блокирования.

|

|

|

Главное, буфера инструкций очередей для главного конвейера делятся между процессорами. Эти буфера включают очереди микрокоманд после исполнительного кэша трасс, очереди после стадии переименования регистра, разупорядочивающий буфер, который хранит очередь инструкций для изъятия и загрузочные и хранящие буфера.

В случае буферов загрузки и хранения, деление так же производиться в легком варианте, для получения реорганизации памяти для каждого логического процессора и для определения ошибок организации памяти.

Разделяемые ресурсы

Большинство ресурсов в физическом процессоре полностью разделяются для улучшения динамического использования ресурсов, включая кэши и все исполнительные блоки. Некоторые разделяемые ресурсы, адресованные линейно, например DTLB, включают бит идентификации логического процессора, для определения какому логическому процессору принадлежит информацию.

|

|

|