|

2.11.3.5. Двоично-десятичные счетчики

|

|

|

|

2. 11. 3. 5. Двоично-десятичные счетчики

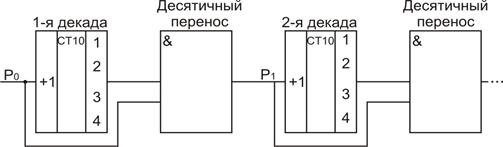

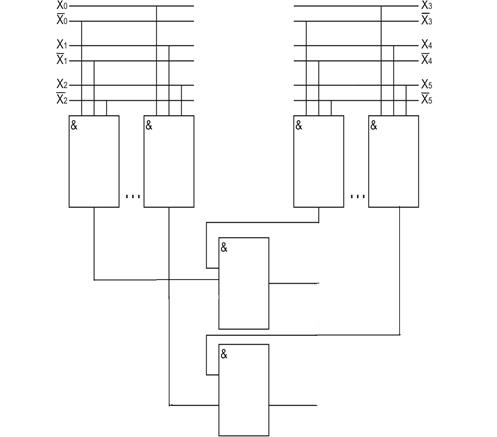

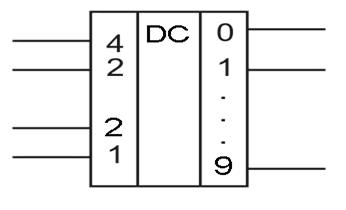

Рис. 2. 67. Обобщенная структура двоично-десятичного счетчика

Эти ФУ позволяют вести подсчет импульсов в десятичной системе счисления за счет использования различных двоично-десятичных кодов.

На рис. 2. 67 представлена обобщенная структура двоично-десятичного счетчика.

Построение такого счетчика сводится к построению логической схемы одной декады в соответствии с выбранным двоично-десятичным кодом (табл. 2. 19).

Таблица 2. 19

| № п/п | Веса разрядов | Наименование кода

| Сумма весов | |||

| 8421 | ||||||

| 5211 | 9 | |||||

| 4221 | 9 | |||||

| 3321 | 9 | |||||

Рассмотрим пример построения логической схемы одной двоично-десятичной декады для кода 5211(табл. 2. 20). Пользуясь этой таблицей, можно составить МОДИС- описание схемы для одной декады при коде 5211.

ТГ1 ’: =‘ ‘ЕСЛИ’ IТГ1 * IТГ2 * IТГ3 * Р0 ‘ТО’ 1 ‘ИНЕСЛИ’ ТГ1 * ТГ2 * ТГ3 * Р0 ‘ТО’ 0 ‘ИНАЧЕ’ ТГ1;

ТГ4 ’: =‘ ‘ЕСЛИ’ IТГ4 * ТГ1 * ТГ2 * ТР3 * Р0 ’ТО’ 1 ‘ИНЕСЛИ’ ТГ4 * ТГ2 * ТГ3 * ТГ1 * Р0 ‘ТО’ 0 ‘ИНАЧЕ’ ТГ4;

Анализ условных предложений для ТГ1 и ТГ4 показывает, что они соответствуют триггеру типа R-S.

Работу ТГ4 можно описать иначе, как триггер со счетным входом.

ТГ4 ’: =’ ‘ЕСЛИ’ ТГ1 * ТГ2 * ТГ3 * Р0 ‘ТО’ IТГ4 ‘ИНАЧЕ’ ТГ4;

Таким же образом следует составить описание для остальных триггеров и схем формирования десятичных переносов.

Далее в соответствии с этими выражениями нужно построить логические схемы, управляемые триггерами и сами триггеры.

|

|

|

Таблица 2. 20

Десятичная цифра | Двоично-десятичный код ТГ4 ТГ3 ТГ2 ТГ1 | |||

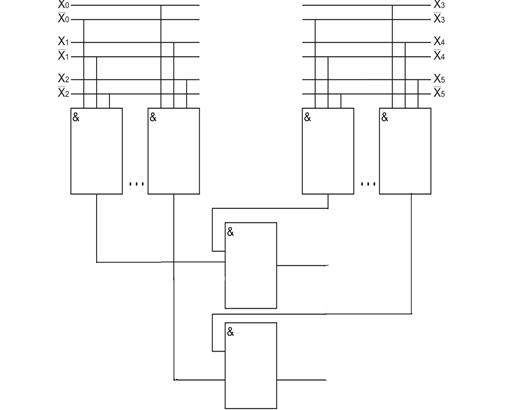

На рис. 2. 68 показана обобщенная логическая система для двух разрядов одной декады двоично-десятичного счетчика.

Рис. 2. 68. Обобщенная логическая схема для двух разрядов одной декады счетчика

2. 11. 4. Дешифраторы

Дешифратор (ДШ) - ФУ, который предназначен для декодирования (определения) состояния регистров или счетчиков, т. е. преобразования двоичного или иного кода в единичный позиционный код.

На рис. 2. 69 показано объединение регистра и дешифратора в одну схему.

Рис. 2. 69. Объединение регистра и дешифратора

Составим МОДИС-описание логической схемы дешифратора для трехразрядной двоичной переменной X.

X = {X0, X1... X3}

D0 ‘: =‘ IX0 * IX1 * IX2 * IX3;

D1 ‘: =‘ X0 * IX1 * IX2 * IX3;

...

D15 ‘: =‘ X0 * X1 * X2 * X3;

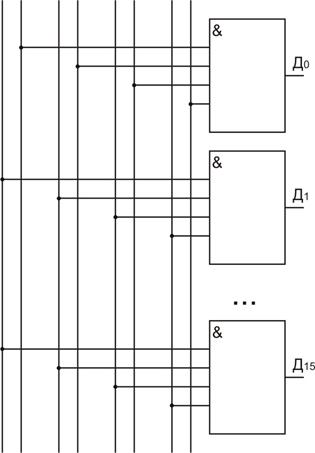

Дешифраторы бывают одноступенчатые (рис. 2. 70), двухступенчатые и многоступенчатые.

Рассмотрим одноступенчатый дешифратор.

Рис. 2. 70. Принципиальная схема одноступенчатого дешифратора

Сложность логической схемы дешифратора оценивается по суммарному количеству входов всех логических элементов, входящих в его состав. Для одноступенчатого дешифратора

M = n  - количество входов ЛС.

- количество входов ЛС.

n –количество разрядов в двоичном коде.

Если n =10, то M = 10 ∙ 1024 = 104 для одноступенчатого ДШ.

Рассмотрим теперь двухступенчатый дешифратор.

Допустим, что на входе дешифратора функция шести переменных

.

.

Запишем логическое выражение для одного из выходов дешифратора в виде конъюнкции от шести переменных X [0: 5]. Затем с помощью круглых скобок представим его в виде произведения двух конъюнкций от трех переменных. Таким же образом нужно записать выражения для всех остальных выходов дешифратора

|

|

|

.

.

Первая конъюнкция в круглых скобка представляет собой один из выходов одноступенчатого дешифратора функции трех переменных X [0: 2], вторая конъюнкция - соответственно от переменных X [3: 5]. Произведение двух этих конъюнкций в круглых скобках представляет собой вторую ступень дешифратора.

Соответствующая логическая схема двухступенчатого дешифратора представлена в виде фрагмента на рис. 2. 71. Подсчитаем суммарное количество входов логических схем для двухступенчатого дешифратора.

Рис. 2. 71. Двухступенчатый дешифратор

На рис. 2. 71 имеются два дешифратора первой ступени, каждый из них на три входных переменных, и один дешифратор второй ступени, который объединяет оба дешифратора первой ступени.

М2ст = ( n/2*2*n/2)*2+2*2n = n*2n/2 + 2n+1

При очень большом количестве разрядов строятся многоступенчатые дешифраторы.

.

.

Качество дешифраторов характеризуется, кроме того, быстродействием.

- задержка логического элемента “И”.

- задержка логического элемента “И”.

Временное запаздывание одноступенчатого дешифратора  , двухступенчатого -

, двухступенчатого -  .

.

При проектировании дешифратора необходимо выбрать некоторый оптимум между сложностью аппаратуры и временной задержкой, которую он вносит в систему.

Аналогично можно построить и двоично-десятичный дешифратор (рис. 2. 72).

Рис. 2. 72. УГО двоично-десятичного дешифратора

|

|

|