|

2.9. Триггеры интегральных систем элементов

|

|

|

|

2. 9. Триггеры интегральных систем элементов

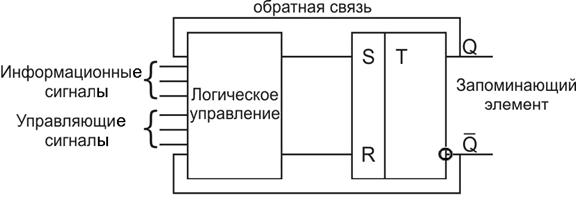

В состав всех интегральных систем (ИС) цифровых элементов входят микросхемы, на которых реализованы различные типы триггеров. Схемы триггеров всех типов можно представить в виде некоторой обобщенной структуры (рис. 2. 30).

Рис. 2. 30. Обобщенная структура триггера

Логические схемы реализуют алгоритм управления триггером. RS –триггер является запоминающим элементом, который хранит один двоичный разряд информации.

Информационные сигналы указывают, какая именно информация (0 или 1) должна быть записана в триггер. Управляющие сигналы определяют момент времени, в который происходит изменение информации в триггере. Кроме того, выходы триггера могут быть подключены к входу обратными связями, по которым поступает информация о текущем состоянии триггера. Классификация триггеров:

-по способу управления различают:

асинхронные триггеры;

синхронизируемые триггеры;

-по структуре различают:

однотактные (одноступенчатые);

двухтактные (двухступенчатые);

-по функциональному назначению:

RS-триггер;

Т–триггер (со счетным входом);

Д–триггер (или триггер- задержка);

JK-триггер универсальный.

2. 9. 1. Синхронизируемый RS- триггер

Рис. 2. 31 Логическая схема синхронизируемого RS-триггера

Существуют две структуры триггеров: однотактная и двухтактная.

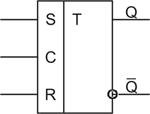

На рис. 2. 31 и 2. 32 показаны логическая схема и УГО однотактного синхронизируемого RS-триггера

S, R – информационные входы, S -вход установки в 1,

R -вход установки в нуль, С – управляющий вход (вход синхронизации).

Рис. 2. 32. УГО синхронизируемого RS-триггера

|

|

|

Работа любого триггера описывается в виде таблицы переходов, которая отражает зависимость состояния триггера от логических сигналов на его входах.

В табл. 2. 15 представлена таблица переходов для синхронизируемого RS-триггера.

t- момент поступления входных сигналов,

Q*- состояние триггера в момент t,

Qt+1 - состояние триггера в момент (t+1).

Таблица 2. 15

| Сt | St | Rt | Qt+1 |

| Q* | |||

| Q* | |||

| Q* | |||

| Q* | |||

запрещенная комбинация запрещенная комбинация

|

2. 9. 2 Двухтактный синхронизируемый RS- триггер

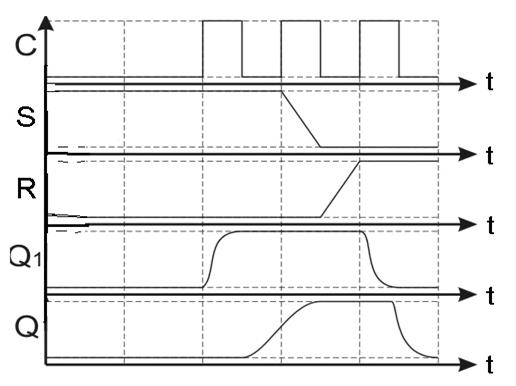

Рис. 2. 33. Временная диаграмма работы двухтактного

RS- триггера

Временная диаграмма работы этого триггера представлена на рис. 2. 33.

Как следует из этой диаграммы, в двух начальных временных тактах значение синхроимпульса C: =0 и триггеры обеих ступеней находятся в одинаковом состоянии - Q1: =0 и Q: =0. Так как S: =1, при поступлении в третьем временном такте очередного синхроимпульса С=1 по его переднему фронту устанавливается новое состояние в триггере первой ступени Q1: =1 (первый такт срабатывания). Затем инверсным синхроимпульсом состояние первого триггера принимается в триггер второй ступени Q: =1 (второй такт срабатывания двухтактного RS -триггера).

В четвертом временном такте C: =1, S: =0, R: =1 и так же, как описано выше, сначала устанавливается в нуль триггер первой ступени Q1=0, затем это состояние передается и во второй триггер Q=0.

Рис. 2. 34. УГО двухтактного R-S- триггера

Таким образом, задержка в срабатывании триггеров первой и второй ступеней равна длительности синхроимпульса.

Логическая схема рассматриваемого триггера, (который называется также двухступенчатым), построенная на элементной базе “И-НЕ”, представлена на рис. 2. 35. Как следует из этой схемы, она состоит из двух частей (ступеней), каждая из которых представляет собой однотактный синхронизируемый RS- триггер. УГО триггера показано на рис. 2. 34.

|

|

|

Рис. 2. 35. Логическая схема двухтактного R-S- триггера

|

|

|