|

Оперативное запоминающее устройство

|

|

|

|

Студент должен

Знать:

• Назначение, принцип работы ОЗУ, его параметры;

• Различия микросхем статического и динамического ОЗУ.

Уметь:

• По заданным параметрам выбрать по справочнику микросхему ОЗУ

Общие сведения

| ОЗУ (Оперативная память) - это обязательная составная часть компьютера, предназначенная для хранения переменной информации и допускающая изменение своего содержимого в ходе выполнения процессором операций по обработке информации. |

Вся информация, вводимая в ЭВМ и возникающая в ходе ее работы, хранится в этой памяти. ОЗУ представляет собой совокупность ячеек, разделенных на разряды для хранения в каждом бите информации. В любую ячейку памяти может быть записан набор нулей и единиц, образующий машинное слово - фиксированную, упорядоченную последовательность битов, рассматриваемую аппаратной частью компьютера как единое целое.

Машинное слово может быть различной длины в зависимости от типа ЭВМ и определяет наибольшее число, которое может удерживаться в ячейке памяти. При байтовой архитектуре минимальной единицей измерения информации является байт, а машинное слово (команда процессора) может равняться 2, 4 или 8 байтам. Следовательно, можно говорить об объеме памяти компьютера, измерять его в килобайтах, мегабайтах, гигабайтах в соответствии с количеством байтовых ячеек как дискретных структурных единиц памяти.

Помимо дискретности структуры свойством оперативной памяти является ее адресуемость. Все ячейки памяти пронумерованы, номер ячейки - это ее адрес. Он позволяет отличать ячейки друг от друга, обращаться к любой ячейке, чтобы записать в нее новую информацию вместо старой или воспользоваться уже хранящейся в ячейке, для выполнения каких-то действий с ней. При таком считывании хранящееся в ячейке слово не изменяется.

|

|

|

В оперативной памяти в виде последовательности машинных слов хранятся как данные, так и программы. Поскольку в любой момент времени доступ может осуществляться к произвольно выбранной ячейке, то этот вид памяти также называют памятью с произвольной выборкой - RAM (Random Access Memory).

Из микросхем памяти (RAM - Random Access Memory, память с произвольным доступом) используется два основных типа:

· статическая (SRAM - Static RAM);

· динамическая (DRAM - Dynamic RAM).

В статической памяти элементы (ячейки) построены на различных вариантах триггеров - схем с двумя устойчивыми состояниями. После записи бита в такую ячейку она может пребывать в этом состоянии сколь угодно долго - необходимо только наличие питания. При обращении к микросхеме статической памяти на нее подается полный адрес, который при помощи внутреннего дешифратора преобразуется в сигналы выборки конкретных ячеек. Ячейки статической памяти имеют малое время срабатывания (единицы-десятки наносекунд), однако микросхемы на их основе имеют низкую удельную плотность данных (порядка единиц Мбит на корпус) и высокое энергопотребление. Поэтому статическая память используется в основном в качестве буферной (кэш-память).

В динамической памяти ячейки построены на основе областей с накоплением зарядов, занимающих гораздо меньшую площадь, нежели триггеры, и практически не потребляющих энергии при хранении. При записи бита в такую ячейку в ней формируется электрический заряд, который сохраняется в течение нескольких миллисекунд; для постоянного сохранения заряда ячейки необходимо регенерировать - перезаписывать содержимое для восстановления зарядов.

Ячейки динамической памяти имеют большее время срабатывания (десятки-сотни наносекунд), но большую удельную плотность (порядка десятков Мбит на корпус) и меньшее энергопотребление. Динамическая память используется в качестве основной.

|

|

|

Обычные виды SRAM и DRAM называют также асинхронными - потому, что установка адреса, подача управляющих сигналов и чтение-запись данных могут выполняться в произвольные моменты времени - необходимо только соблюдение временных соотношений между этими сигналами. В эти временные соотношения включены так называемые охранные интервалы, необходимые для стабилизации сигналов, которые не позволяют достичь теоретически возможного быстродействия памяти.

Существуют также синхронные виды памяти, получающие внешний синхросигнал, к импульсам которого жестко привязаны моменты подачи адресов и обмена данными; помимо экономии времени на охранных интервалах, они позволяют более полно использовать внутреннюю конвейеризацию и блочный доступ.

В ОЗУ предусматриваются три режима работы:

· Режим хранения при отсутствии обращения к ЗУ;

· Режим чтения хранимых слов;

· Режим записи новых слов.

ОЗУ является энергозависимым устройством т.к. при отключении питания информация разрушается.

8.2.2. Структуры накопителей и исполнение запоминающих ячеек устройств статического типа

Основой ОЗУ является накопитель или матрица памяти, состоящая из отдельных запоминающих (бистабильных) ячеек. Обычно в качестве этих ячеек используются различного рода триггеры. Двоичная информация, записанная в такую ячейку, может сохраняться в этой ячейке до тех пор, пока не будет заменена другой или не будет снято напряжение питания.

При использовании такого накопителя решается две задачи:

1. Выбор конкретной ячейки накопителя, в которую будет записана или из которой будет считана информация;

2. Что нужно сделать — записать или прочитать информацию в ячейке.

Первая задача решается с помощью адресации всех ячеек накопителя. Вторая задача решается переводом ячейки памяти в режим записи или считывания по сигналу на входе схемы управления.

Накопитель или матрица памяти состоит из n строк. В состав каждой строки входят m запоминающих ячеек, образующих m-разрядное слово. Информационная емкость накопителя равна N=nm, где n число строк (или слов), m - число столбцов (или разрядов).

|

|

|

Соответствующие шины в накопителе управляются от дешифраторов строк (Х) и столбцов (Y), на входы которых поступают адресные сигналы А0…АN.

При записи и считывании осуществляется обращение (выборка) к одной или нескольким запоминающим ячейкам одновременно. Дешифраторы строк и столбцов выполняют выбор требуемых ячеек памяти с помощью адресных сигналов Х0...Хn и Y0... Уm.

Такая матрица запоминающих ячеек (ЗЯ) может работать в двух режимах:

пословном и двухкоординатном.

Структура пословной матрицы приведена на рисунке 8.3.

Рисунок 8.3

Как видно из схемы (рисунок 8.3), адресные шины Х0...Хn электрически связаны с каждой ЗЯ одного слова, в то время как разрядные шины Y0...Ym имеют связь с ЗЯ одноимённого разряда всех слов. При наличии в адресной шине Хi сигнала выбора i–го слова, соответствующего высокому уровню, состояние каждой ячейки в этом слове может быть считано по разрядным шинам Y0...Ym.

Если необходимо записать информацию по выбранному адресу Хi, то на разрядные шины Y0... Ym подаются соответствующие электрические сигналы, которые подводятся ко всем ЗЯ i-й строки (слова) (рисунок 8.4).

Рисунок 8.4

При работе матрицы ЗЯ в двукоординатном режиме с помощью шин строк и столбцов выбирается любая ячейка матрицы. В этом случае разрядная шина Р, которая является общей для всех ЗЯ, используется как для записи, так и для считывания информации в адресованных ЗЯ.

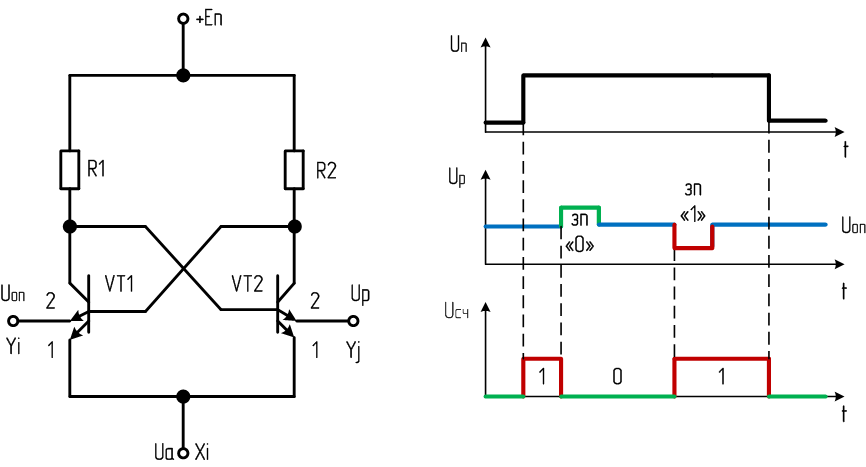

Простейшей ЗЯ является схема RS-триггера, построенная на двух многоэмиттерных биполярных транзисторах VT1 и VТ2, изображенная на рисунке 8.5,а.

а) б)

Рисунок 8.5

Первые эмиттеры обоих транзисторов соединены с адресной шиной ЛА потенциал которой Uа в установившемся состоянии должен быть самым низким. Вторые эмиттеры этих транзисторов присоединены к разрядным шинам Р и ЛА. На разрядной шине Р установлено опорное напряжение Uоп, а на шину ЛА подается напряжение Up. Режим работы схемы зависит от соотношения между напряжениями Uоп, Up и Ua.

В режиме хранения информации выполняется условие Ua < Uоп = Up. В этом случае схема находится в одном из устойчивых состояний, при котором открытым может быть транзистор VТ2 или VТ1. Ток протекает по первому эмиттеру открытого транзистора, а вторые эмиттеры обесточены. Например, если в триггер записана логическая 1, то транзистор VТ2 открыт, а транзистор VT1 закрыт. В этом случае за логическую единицу принимается наличие тока в транзисторе VТ2.

|

|

|

В режиме считывания с помощью адресного сигнала Хi, на шине устанавливается напряжение Ua > Uоп = Up.Если в триггер записана логическая 1, то ток открытого транзистора VТ2 потечет в разрядную шину Yj. Наличие тока в разрядной шине соответствует считыванию 1, а его отсутствие соответствует логическому 0.

Условия режима записи зависят от состояния, в которое необходимо установить ЗЯ. Если триггер находился в состоянии 1 (транзистор VТ2 открыт, транзистор VТ1— закрыт), то для записи 0 необходимо по разрядной шине Р подать напряжение Up,> Uоп сохраняя условие Uа> Up. При этом триггер перейдет в новое состояние, при котором транзистор VТ2 закроется, а транзистор VТ1 откроется. Для записи в ЗЯ логической 1 на шину Р следует подать напряжения Up <Uоп и обеспечить условие Ua >Uоп. Временные диаграммы работы ЗЯ в режимах записи логического нуля или единицы приведены на рисунке 8.5,б.

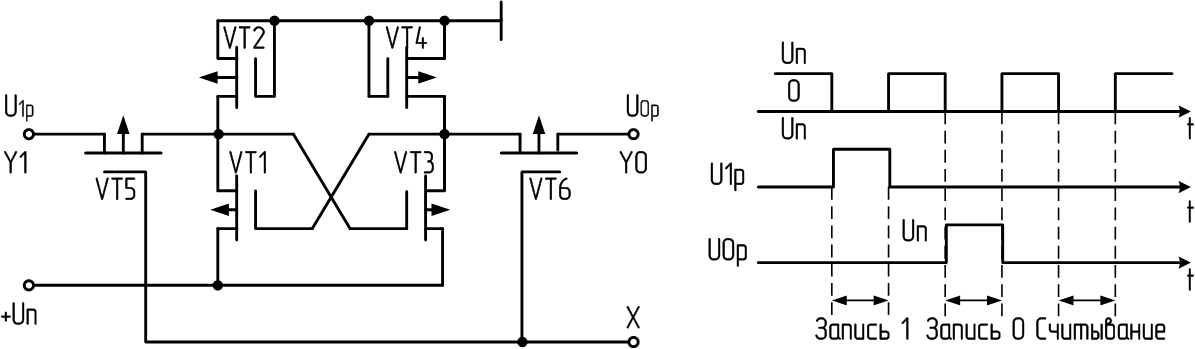

Запоминающая ячейка на RS-триггере, выполненном на p-канальных МОП транзисторах, приведена на рисунке 8.6,а.

а) б)

Рисунок 8.6

Триггер образован транзисторами VТ1,...,VТ4. Переключение триггера для записи и считывания выполняется транзисторами VТ5 и VТ6. Временные диаграммы работы триггера изображены на рисунке 8.6,б.

В исходном состоянии напряжения на разрядных шинах U1p и U0p равны нулю, а на шине слова Х установлено напряжение питания Еn. При этом транзисторы VТ5 и VТ6 закрыты, так как напряжение между затворами и истоками меньше порогового напряжения, и триггер находится в одном из устойчивых состояний, например, транзистор VТ3 открыт, а транзистор VТ1 закрыт.

Для записи логической 1 в ЗЯ на шину слова подается отрицательный сигнал, изменяющий напряжение в ней до нуля. Одновременно в разрядную шину Y1 подается положительный сигнал, изменяющий напряжение в ней до напряжения питания Un. При этом транзистор VТ5 открывается и положительный сигнал подается на затвор VТ3, запирая его. После запирания транзистора VТ3 отпирается транзистор VТ1 и на его стоке устанавливается положительное напряжение, что соответствует состоянию логической 1.

Для записи логического нуля в ЗЯ на шине слова устанавливается нулевое напряжение, а напряжение питания подается на разрядную шину Y0. При этом транзистор VT6 открывается и положительное напряжение через него подается на затвор VТ1, запирая его, что приводит к отпиранию транзистора VТ3.

|

|

|

Для считывания информации, записанной в ЗЯ, нужно подать отрицательный сигнал только на шину слова, изменив в ней напряжение до нуля. При этом оба транзистора VТ5 и VT6 открываются и через транзистор, подключенный к триггеру с положительным напряжением, протекает ток, поступающий в соответствующую разрядную шину.

Статические ОЗУ

Студент должен

Знать:

· Структуру матриц запоминающих ячеек при пословной и двухкоординатной организации;

· Элементы запоминающих ячеек.

Запоминающее устройство состоит из блоков: запоминающего массива и электронного обрамления.

Запоминающий массив (накопитель) содержит запоминающие элементы (ЗЭ), каждый из которых может принимать состояния логической 1 или логического 0, т. е. хранить один бит информации.

В запоминающем элементе хранится один разряд записанного двоичного слова; все n-разрядное слово записывается в запоминающих элементах, составляющих ячейку памяти. Ей соответствует определенный адрес, характеризующий положение этой ячейки в накопителе. Запись и считывание слова (обращение к ЗУ) производятся по адресу, которым выбирается определенная ячейка. Запоминающие элементы должны обладать двумя устойчивыми состояниями. К числу таких элементов относятся триггеры (полупроводниковые ЗУ).

Электронное обрамление содержит, в частности, дешифраторы адреса и усилители записи и считывания. Код адреса, поступающий на входы дешифратора, возбуждает один из его выходов. Этим разрешается запись слова в определенные ЗЭ или считывание изних.

Существует несколько способов объединения запоминающих элементов в накопителе (несколько видов организации ЗУ).

|

|

|