|

ЗУ с однокоординатной выборкой

|

|

|

|

Организация ЗУ, при которой одной линией выбирается группа запоминающих элементов (группа разрядов одного слова), называется словарной или однокоординатной. Смысл последнего названия станет ясен после рассмотрения такого ЗУ, упрощенная структура которого приведена на рисунке 8.7.

Рисунок 8.7

Запоминающий массив (ЗМ) представляет собой матрицу, в каждой строке которой располагаются ЗЭ, хранящие разряды одного слова. В каждом столбце матрицы находятся ЗЭ, хранящие одноименные разряды всех слов. В ЗМ (рисунок 8.7) могут быть зафиксированы четыре четырехразрядных слова, т. е. его емкость равна 16 бит.

Для записи слова, к примеру, в ячейку из элементов ЗЭ9—ЗЭ12 нужно выполнить следующие шаги:

1) подать сигнал выбора адреса на адресную линию ЛА (которая подключена только к элементам ЗЭ9—ЗЭ12);

2) сигналы, соответствующие значениям разрядов (0 или 1) записываемого слова, подать на разрядные линии ЛР1—ЛР4;

3) на линию Зп/Сч, общую для всех ЗЭ, подать сигнал, разрешающий запись. При этом ЗЭ (в данном случае третьей строки матрицы) переключаются в состояния, соответствующие значениям разрядов.

Считывание слова происходит при отсутствии на шине Зп/Сч сигнала, разрешающего запись, и при подаче сигнала на требуемую адресную шину. При этом потенциалы, соответствующие значениям разрядов слова (0 или 1), появляются на выходах разрядных усилителей считывания.

Выбор той или иной адресной линии (ЛА) производится дешифратором адреса, на вход которого поступает двоичный код номера ЛА — номера ячейки, в которую должно быть записано или из которой должно быть считано слово. Отметим, что ячейка, в которую записывается или из которой считывается слово, имеет одну координату. Ею является номер строки матрицы запоминающих элементов.

|

|

|

Описанное запоминающее устройство называют также двумерным ЗУ (запоминающие элементы расположены в одной плоскости), ЗУ типа 2D.

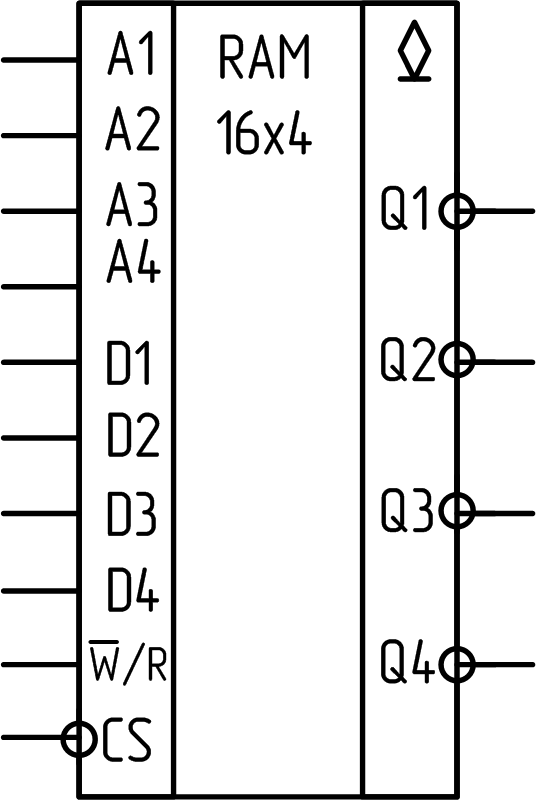

Рассмотрим ОЗУ с адресной организацией выборки 16 четырехразрядных слов (16 слов х 4 разряда = 64 бита) на ИМС К155РУ2. Зарубежный аналог SN7489N, SN7489J.

Функциональная схема микросхемы К155РУ2 представлена на рисунке 8.8.

Рисунок 8.8

Массив памяти образован 16 четырехразрядными цепочками триггеров. При сигнале СS=0 (V=0) одна из цепочек, соответствующая выставленному адресу А1— А4, переходит в рабочее состояние, и ее сигналы поступают на входы элемента И-НЕ (7—10).

При сигнале СS=1 (V=l) на всех выходах дешифратора DC низкие уровни и, следовательно, все триггеры отключены от выходных шин накопителя.

При СS =0 и W/R=0 вырабатывается сигнал записи и на выбранную цепочку поступают информационные сигналы (входы D1-D4). В этом режиме при смене информации на входе ОЗУ происходит запись.

В этом режиме при смене информации на входе ОЗУ происходит перезапись информации в данном слове массива. При сигналах СS=1 и W=0 входная информация проходит непосредственно на выход микросхемы, минуя массив триггеров (дешифратор не выбирает ни одной из цепей).

При V=1 и W=1 запрещена работа дешифратора, узла, вырабатывающего сигнал «Запись» «Считывание».

Таким образом, блок управления (десять логических элементов) обеспечивает работу ОЗУ в режимах: запись, считывание, сквозной перенос, хранение информации. В таблице 8.1 представлены режимы работы ИМС К155РУ2.

Таблица 8.1 Таблица состояний ОЗУ К155РУ2

| Режим работы | Вход | Выход Qn | ||

| CS | W/R | Dn | ||

| Запись | ||||

| Считывание | х | Dn | ||

| Запрет записи | ||||

| Отключение выходов | х |

Выходные логические элементы И-НЕ (7-10) выполнены по схеме с открытым коллектором, что позволяет соединять вместе выходы Q нескольких микросхем ОЗУ. При этом происходит наращивание емкости ОЗУ (две микросхемы - 32 слова, три - 48 и т.д.). Адресное управление А1-А4, информационные входы D1-D4 и выходы Q1-Q4 всех микросхем объединяют в общие шины, а выбор рабочего массива осуществляют дополнительным дешифратором по входам CS и W/R. Так построена микросхема К155РУ2.

|

|

|

Условное изображение представлено на рисунке 8.9.

Рисунок 8.9

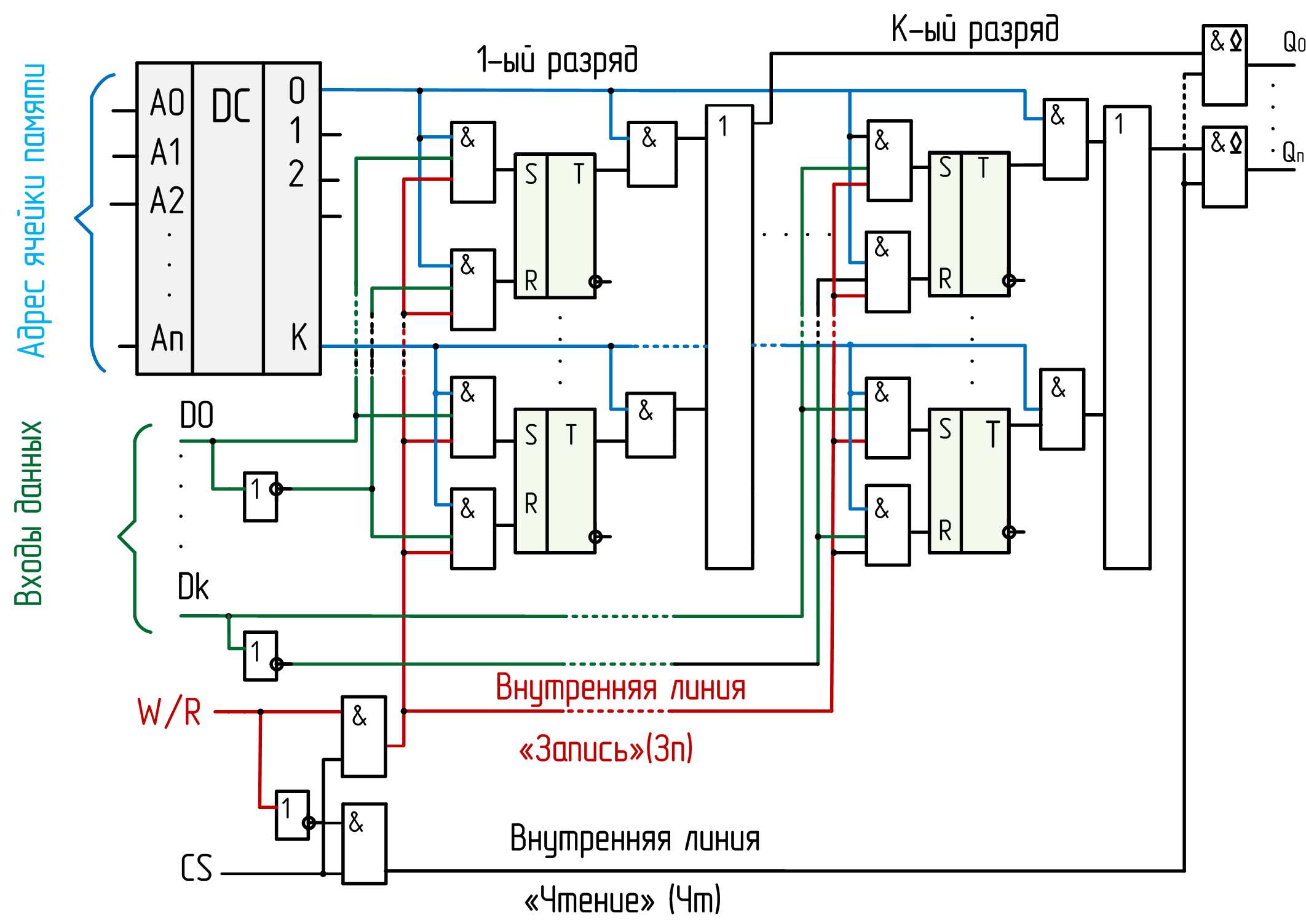

На рисунке 8.10 показан один из вариантов управления внутренними элементами микросхемы сигналами на ее входах. Разряды ячейки матрицы составляют триггеры с входной и выходной логикой. Каждую ячейку — строку матрицы — выбирают с выхода дешифратора.

Рисунок 8.10

Если CS=1 и W/R=1 то возбуждается линия «Запись» (Зп=1) и на входы S и R триггеров поступают взаимно инвертированные разряды записываемого слова с входов D0—Dк. При этом на линии «Чтение» — логический 0, благодаря чему выходы Q0—Qк трехстабильных элементов находятся в высокоомном состоянии: чтение информации с выходов триггеров исключено.

Когда CS= 1 и W/R — 0 возбуждается линия «Чтение» (Чт = 1): занесенная в ячейку информация появляется на выходах Q0-Qк. Выходы триггеров в одноименных разрядах всех ячеек связаны с определенным дизъюнктором. Поэтому какая бы ячейка памяти ни была выбрана с выхода дешифратора, ее содержимое будет выведено на выходы Q0—Qк.

При возбуждении линии «Чтение» (W/R = 0).сигнал на линии «Запись» Зп = 0 — конъюнкторы на входах всех триггеров матрицы блокированы и запись с входов DO—Dк осуществиться не может.

Вывод выбора кристалла CS микросхем ОЗУ позволяет объединять несколько микросхем для увеличения объема памяти ОЗУ.

|

|

|