|

Двоично-десятичные счетчики

|

|

|

|

И делители частоты

Двоично-десятичные коды

Для четырехразрядного двоичного числа любое одноразрядное десятичное число А может быть выражено в виде суммы:

, (4.13)

, (4.13)

где: Qn – двоичное число в соответствующих разрядах кодовой комбинации (0 или 1);

an – некоторые постоянные числа называемые весами разрядов.

Такой код называют взвешенным. Двоично-десятичные счетчики могут быть построены и в других кодах, например 2-4-2-1. Чаще других используют двоично – десятичный код 8-4-2-1.

Особую группу двоично-десятичных кодов образуют самодополняющиеся коды. Их особенность: при поразрядном инвертировании получается кодовая комбинация десятичного числа, дополняющего исходное десятичное число до числа 8.

У кода 8-4-2-1 имеется ряд преимуществ:

1. Двоичные комбинации для одноразрядных десятичных чисел в нём такие же, как и при двоичном счете.

2. Этот код однозначен – для каждого десятичного числа имеется только одна, соответствующая ему кодовая комбинация.

Таблица 4.19.

Таблица состояний для кода 8-4-2-1

| C | Q1 23 | Q2 22 | Q3 21 | Q4 20 |

4.8.1.

4.8.2. Структура двоично-десятичного счетчика

Для того, чтобы счетчик считал до 10, необходимо четыре триггера, поскольку с тремя триггерами счетчик будет считать только от 0 до 7.

Рис.4.62. Условное обозначение двоично-десятичного счетчика

Двоичный счетчик является делителем частоты с фиксированным коэффициентом деления (2; 4; 8; 16). В данной схеме (рисунок 4.63) используются JK – триггеры. Если их входы никуда не подключены, то считается что это соответствует уровню логической «1».

Рис.4.63. Двоично–десятичный счетчик К155ИЕ2 и его

использование в качестве делителя частоты

|

|

|

Таблица 4.20.

Режимы работы двоично-десятичного счетчика

| Режим | R1 | R2 | R3 | R4 |

| Сброс «0» | х | х | ||

| «9» | х | х | ||

| Счет | х х | х х | х х | х х |

Рис.4.64. Условное обозначение и цоколёвка

двоично-десятичного счетчика К155ИЕ2

Таблица 4.21.

Таблица соединений входов счетчика при различных коэффициентах

деления

| Коэф. Деления | |||||||||||

| Вход | |||||||||||

| Выход | 8,9 | 8,11 | 8,11 | ||||||||

| Соединения Перемычки | 1-12 2-12 3-9 6-10 | 2-9 3-8 6-10 | 1-12 2-8 6-10 | 1-12 2-12 3-8 6-10 | 1-11 2-9 3-8 6-10 | 1-12 6-9 7-8 2-10 | 1-12 2-4 6-10 | 1-12 2-12 3-11 6-10 | 1-12 |

4.8.3. Делитель частоты с переменным

коэффициентом деления

Разработаны специальные цифровые схемы двоичных счетчиков, у которых коэффициент деления частоты входных импульсов задается не перемычками и соединениями выводов, а двоичным кодом на специальных управляющих входах счетчика. Примером такого цифрового устройства является счетчик К155ИЕ8 (рисунок 4.65).

Рис.4.65. Микросхема К155ИЕ8

Назначения выводов счетчика:

- C – тактовый счетный вход;

- R – вход установки в «0»;

- D1 - D6 – управляющие информационные входы для установки коэффициента деления;

- V1 – стробирующий вход, управляющий дешифратором коэффициента деления;

- V2 – буферный вход, управляющий информационными входами (D1- D6);

- V3 – вход одиночно-каскадного счета;

- Q,  – прямой и инверсный выходы;

– прямой и инверсный выходы;

- P – разрешающий выход переноса для наращивания разрядов счетчика;

- Вывод 16 – питание +5 В.;

- Вывод 8 – (общий) корпус.

Нормальный режим работы счетчика – счетный, при этом сигналы на входах R; V1; V2 – должны иметь уровень логического «0». Вывод V3 может быть соединён с выходом переноса в старший разряд Р предыдущего счетчика, идентичного этому, для увеличения числа разрядов и коэффициента деления вдвое.

|

|

|

Данный двоичный счетчик позволяет делить частоту входных импульсов на число до  .

.

Коэффициент деления определяется формулой:

, (4.14)

, (4.14)

где

A-F – состояние логического сигнала на соответствующем информационном входе D (0 или 1);

M – коэффициент деления счетчика.

Частота сигнала на выходе относится к частоте сигнала на входе:

(4.15)

где

M – количество импульсов за период, равный 64 периодам входного тактового импульса.

Мультиплексоры

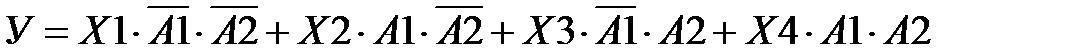

Назначение мультиплексоров – это коммутация нескольких входных каналов на один выход, например на рисуноке 4.66 показан самый простой мультиплексор двух входных каналов Х1 и Х2 на один выход Y и его механический аналог.

Рис.4.66. Схема простейшего мультиплексора

Рис.4.66. Схема простейшего мультиплексора

Изображённый на рисунке 4.66 логический переключатель – это простейший двухканальный мультиплексор на два входа и один выход. Принято, что наращивание числа каналов (разрядов) в мультиплексорах происходит на величину кратную  , где n = 1, 2, 3....

, где n = 1, 2, 3....

Буквенное обозначение интегральных микросхем мультиплексоров в схемах может иметь следующий вид: MS, MX, MUX. Полное название этого функционального элемента: мультиплексор – селектор. Условное графическое обозначение в схемах этого элемента на примере четырехканального коммутатора показано на рисунке 4.67, а соответствующая внутренняя структура – на рисунке 4.68.

Рис.4.67. Условное обозначение четырёхканального мультиплексора

Рис.4.68. Внутренняя структура четырехканального MS

(микросхема К155КП2)

Мультиплексоры-селекторы имеют управляющие входы – Аi; информационные входы – Bj; вход сброса в ноль (стробирования) – R;прямой – Q; и инверсный –  выходы.

выходы.

Принцип работы этих устройств следующий: мультиплексор передаёт на свой прямой выход Q логическое состояние того информационного входа Bj, номер которого соответствует двоичному коду на его управляющих входах Аi. Такой алгоритм функционирования может быть описан следующей переключательной функцией на примере двухканального мультиплексора:

. (4.16)

. (4.16)

В распространённой серии интегральных микросхем К155 имеются, например, следующие мультиплексоры-селекторы:

К155КП2 (два мультиплексора по 4 информационных входа со стробированием);

|

|

|

К155КП5 (восьмиканальный MS, то же, что К155КП7, но без входа стробирования R и инверсного выхода  );

);

К155КП1 (шестнадцатиканальный MS, имеет четыре управляющих входа, нет инверсного выхода  ).

).

Таблица 4.22.

Таблица состояний для восьмиканального мультиплексора К155КП7

| А1 | А2 | А3 | R | В1 | В2 | В3 | В4 | В5 | В6 | В7 | В8 | Q |

|

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | |||||||

| х | х | х | х | х | х | х | х | х | х | х |

|

|

|