|

Синтез комбинационных логических схем в базисе мультиплексоров и демультиплексоров

|

|

|

|

Мультиплексоры MS и демультиплексоры DC (цифровые коммутаторы), кроме своих прямых очевидных функций - коммутации входной информации на выход, могут применяться для реализации любых произвольных логических функций, то есть цифровые коммутаторы являются предельно универсальными элементами, причем, каждый из них представляет собой функционально полный базис.

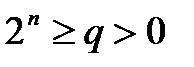

Универсальной – называется логическая схема, реализующая дизъюнкцию любых конъюнкций заданного числа переменных n:

, (6.8)

, (6.8)

где q - степень универсальности.

Элемент, у которого q = 2 n называется предельно универсальным, то есть на его основе можно реализовать любую функцию n переменных.

Запишем переключательную функцию 4-х канального мультиплексора, которая имеет следующий вид:

. (6.9)

. (6.9)

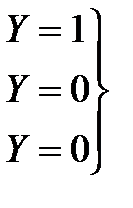

Пусть требуется реализовать комбинационную логическую схему, выполняющую некоторую функцию двух переменных, представленную в таблице.

Таблица 6.5.

Таблица состояний комбинационной схемы

| X1 | X2 | Y |

Если на адресные входы мультиплексора подать входные переменные Х1 и Х2, а информационные входы мультиплексора соединить с логическими константами «0» и «1» так, как показано на рисунке 6.7, то получится реализация требуемой схемы.

Рис.6.7. Реализация комбинационной схемы на 4-х канальном

мультиплексоре (MS)

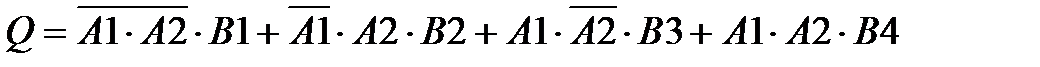

В общем виде для n-канального мультиплексора MS «1 из n» переключательная функция будет иметь следующий вид:

. (6.10)

. (6.10)

Мультиплексор - предельно универсальный логический элемент, так как функция Q учитывает все возможные двоичные комбинации входных переменных Аi.

В качестве примера реализации произвольных логических функций в базисе селекторов-мультиплексоров рассмотрим несколько способов синтеза схем цифровых компараторов.

|

|

|

6.6.1. Реализация двухразрядных цифровых

компараторов на мультиплексорах

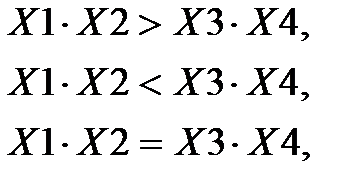

Алгоритм функционирования цифрового компаратора, сравнивающего двухразрядные двоичные числа X1X2 и X3X4, заключается в следующем:

Если  то

то  (6.11)

(6.11)

Эти формулы позволяют заполнить таблицу состояний цифрового компаратора:

Таблица 6.6.

Таблица состояний цифрового компаратора

| № | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

| X1 | 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 |

| X2 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 |

| X3 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 |

| X4 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 |

| Y | 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 |

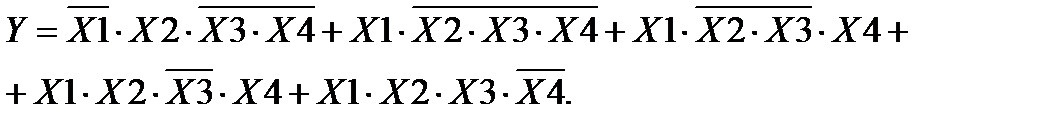

Исходя из таблицы состояний компаратора может быть записана его переключательная функция. После минимизации она будет иметь вид:

(6.12)

(6.12)

Поскольку число входных сигналов двухразрядного параллельного компаратора равно 4, то число возможных двоичных комбинаций равно 24 = 16. В соответствии с этим пронумеруем колонки таблицы состояний компараторов и для его реализации используем 16-ти канальный мультиплексор.

Входные сигналы подаём на управляющие входы Аi. Компаратор сравнивает два двухразрядных двоичных числа a и b.

Выходом компаратора Y будет служить выход мультиплексора Q. На информационные выходы Вj будем подавать логические сигналы «0» или «1» - такие, какие принимает функция Y в таблице состояний. Для каждого набора входных переменных на информационных входах:

. (6.13)

. (6.13)

Это первый способ синтеза схем на мультиплексорах MS.

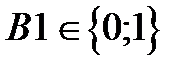

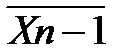

Второй способ, позволяющий вдвое упростить схемное решение системы, состоит в том, что сигналы на информационных входах Вj принадлежат другому множеству:

. (6.14)

. (6.14)

Выход MS является выходом компаратора (прямой выход Q). На управляющие выходы Аi подаём переменные X1, X2, X3. На информационные входы Bj подаём сигналы  , в соответствии с таблицей состояний компаратора для каждой пары двоичных наборов, как показано на рисунке 6.8.

, в соответствии с таблицей состояний компаратора для каждой пары двоичных наборов, как показано на рисунке 6.8.

|

|

|

Рис.6.8. Параллельный компаратор на 16-ти канальном MS

Рис.6.9. Второй способ реализации цифрового компаратора

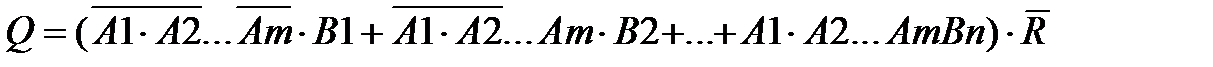

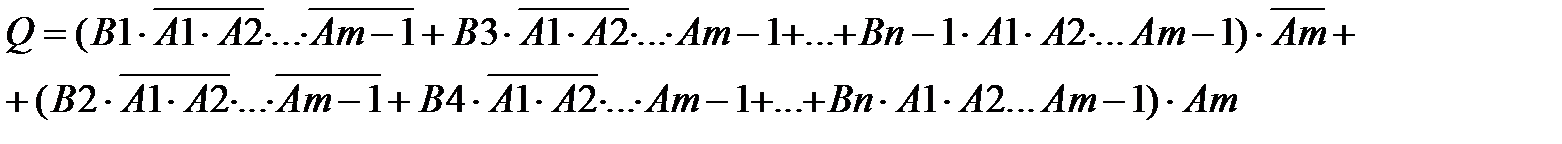

Третий способ: он заключается в использовании входа стробирования MS и позволяет ещё в два раза уменьшить требуемое число каналов MS (по сравнению со вторым способом) для реализации той же функции. Преобразуем переключательную функцию n -канального MS:

(6.15)

(6.15)

Синтезированная в результате схема представлена на рисунке 6.10.

Рис.6.10. Третий способ реализации цифрового компаратора

Существует ограничение при синтезе логических схем на MS. Это ограничение на число входных переменных. Для 16-ти канального MS при использовании третьего способа синтеза их максимальное число не превышает 6. Это объясняется тем что в одном корпусе стандартной микросхемы из-за ограничения числа выводов затруднительно расположить цифровой коммутатор более чем на 16 каналов.

Для дальнейшего увеличения числа входных переменных применяют цепочечные и древовидные структуры (рисунок 6.11).

Рис.6.11. Однородная цепочечная структура

Для цепочечной структуры на управляющие входы последующих MS подаётся выход предыдущего MS.

При древовидной структуре соединения MS выходы группы MS (корни дерева) подаются на информационные входы других MS – вершины дерева.

Таким образом, процедура синтеза комбинационных логических схем в базисе MS состоит в последовательности следующих операций:

1. Пронумеровать переменные от 1 до n.

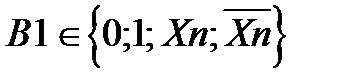

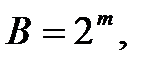

2. Выяснить требуемое число каналов В и по ним выбрать MS:  где m = n – первый способ синтеза; m = (n - 1) – второй способ (для MS без стробирования); m = (n - 2) – третий способ (для MS со стробированием).

где m = n – первый способ синтеза; m = (n - 1) – второй способ (для MS без стробирования); m = (n - 2) – третий способ (для MS со стробированием).

3. Заполнить таблицу состояний реализуемой функции.

4. Подать на входы Аi мультиплексора переменные с номерами от 1 до n - 1, либо до n - 2 либо до n.

5. Подать на входы Bi величины из множества  в соответствии с таблицей состояний. При использовании стробирования на первый MS подаётся нечётный набор номеров, на другой – чётный.

в соответствии с таблицей состояний. При использовании стробирования на первый MS подаётся нечётный набор номеров, на другой – чётный.

6. Подать на вход R одного MS переменную Xn - 1, на вход другого R – переменную  . Подать на R логический «0», если стробирование не используется.

. Подать на R логический «0», если стробирование не используется.

7. Применять цепочечные и древовидные структуры соединения MS, если число переменных n > 6.

|

|

|

8. При цепочечной структуре, выход предыдущего MS подать на управляющий вход последующего MS. При древовидной структуре выходы группы MS подать на информационные входы узлового MS. При использовании стробирования выходы MS подавать на логический элемент «ИЛИ».

6.6.1.

6.6.1.

6.6.2. Синтез комбинационных логических схем

на демультиплексорах (DC)

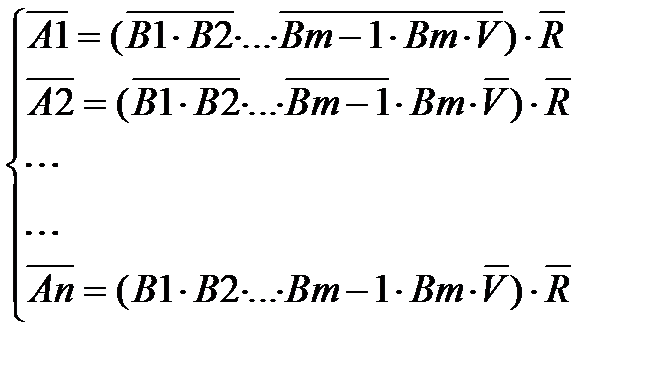

Обобщённая переключательная функция n -канального демультиплексора – декодера может быть записана в следующем виде:

(6.16)

(6.16)

В системе переключательных функций демультиплексора учтены все n = 2 m двоичные комбинации входных переменных Вj. Это позволяет также называть DC предельно универсальным логическим элементом, способным реализовать любую функцию m переменных. Таким образом, DC образуют функционально – полный базис. Если подать переменные X1...Xm на управляющие входы В1...Bm то, при сигналах на входах V, R = 0, значение логического «0» будет передаваться на тот выход Аi, номер которого соответствует текущей двоичной комбинации входных переменных.

Объединяя через схему «ИЛИ» те выходы DC, номера которых соответствуют номерам двоичных наборов, когда синтезируемая функция принимает единичные значения, получаем схему, реализующую эту функцию.

Объединение выходов DC осуществляется через логический элемент «ИЛИ». C целью упрощения схемы, в зависимости от количества логических «1» и «0» в таблице истинности для выходной функции, можно объединять и те выходы DC, для которых выходная функция принимает значение логического «0». В этом случае для объединения выходов DC применяют элемент «ИЛИ-НЕ».

Второй путь упрощения схемы состоит в применении схемы «проводного» или «монтажного ИЛИ». В этом случае применяют ИМС DC с открытым коллектором на выходе. При этом выходы DC соединяются непосредственно и, через один нагрузочный резистор, подключаются к источнику питания Еп, что также существенно упрощает схему.

Возможно выполнение логической схемы «ИЛИ» на диодах. В этом случае также требуется нагрузочный резистор.

|

|

|

Рис.6.12. Реализация логической функции цифрового компаратора при помощи DC

Таблица 6.7.

Таблица одновременной реализации одним DC всех основных логических функций

| X1 | X2 | X3 | X4 | И | НЕ | ИЛИ | И-НЕ | Искл. или | Неравнозначность | ИЛИ-НЕ |

Существенная особенность схем на DC состоит в возможности одновременного параллельного формирования одним DC нескольких переключательных функций входных переменных. При этом входные переменные подаются на управляющие входы DC, а объединения выходов DC осуществляется в нескольких логических схемах «ИЛИ» (по числу реализуемых функций). Одновременная реализация одним DC всех основных логических функций 4-х переменных приведена в таблице.

Точки на схеме матрицы горизонтальных и вертикальных шин обозначают места включения схем «ИЛИ» – диодных или логических.

Рис.6.13. Элемент диодной матрицы «ИЛИ»

Рис.6.14. Пример реализации всех логических функций на одном DC

Существуют ограничения на синтез логических схем на DC – ограниченное число входных переменных, определяемое числом управляющих входов DC. Значительное их увеличение затруднено из-за ограниченного числа выводов у микросхемы. Увеличить число входных переменных на единицу можно, используя вход стробирования R демультиплексоров DC.

6.6.1.

6.6.2.

6.6.3. Система переключательных функций

дешифратора (DC) при использовании

стробирования

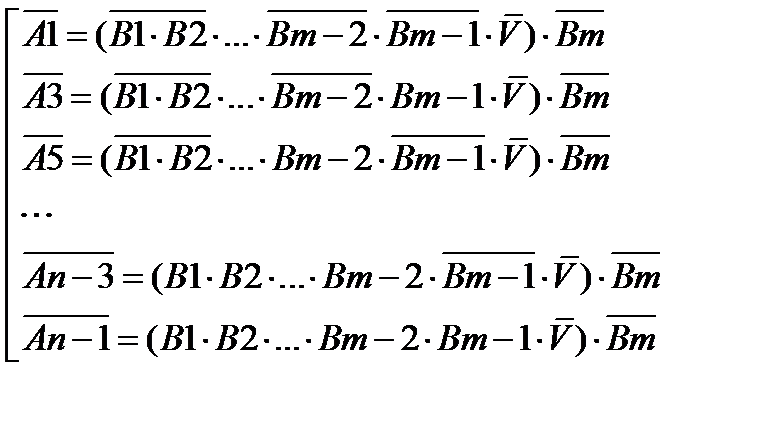

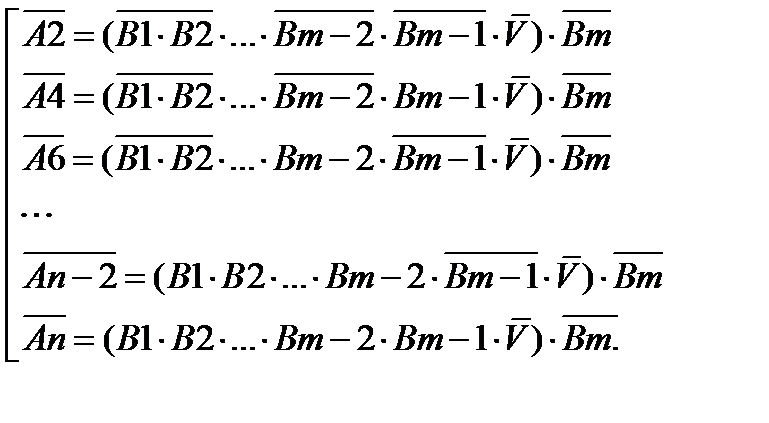

В системе переключательных функций обобщенного n-канального демультиплексора вынесем за скобки переменную  для нечетных номеров входных переменных Ai, а переменную Вm – для четных номеров входных переменных Ai:

для нечетных номеров входных переменных Ai, а переменную Вm – для четных номеров входных переменных Ai:

(6.17)

(6.18)

Из анализа этих систем (6.17) и (6.18) видно, что это переключательные функции двух дешифраторов, на вход R одного из них подана переменная Bm, на вход R другого –  . При этом каждый DC имеет в два раза меньшее число входов, чем первоначальный DC.

. При этом каждый DC имеет в два раза меньшее число входов, чем первоначальный DC.

Соответственно, при синтезе переключательных схем на DC с использованием стробирования, необходимо подать параллельно на управляющие входы двух DC переменные от X1 до Xn-1, подать переменную Xn на вход R одного, и с инверсией на вход R другого DC. Подать логический «0» на входы передачи данных V обоих DC; объединить выходы DC через схему «ИЛИ» в соответствии с таблицей состояний реализуемой функции.

Пример: Реализация 2-х разрядного параллельного компаратора на DC со стробированием

Использование стробирования позволяет вдвое упростить схемное решение, то есть применять демультиплексор с числом каналов вдвое меньшим, чем без использования стробирования; либо при том же числе каналов демультиплексора реализовать вдвое более сложные логические схемы.

|

|

|

Рис.6.15. Параллельный компаратор со стробированием

Таким образом, методика синтеза схем на демультиплексорах состоит в следующем:

1. Присвоить переменным номера от 1 до n.

2. Определить требуемое число входов и по ним – тип демультиплексора.

3. Подать все переменные с номерами от 1 до n на управляющие входы демультиплексора.

4. Подать на вход передачи данных V и на вход стробирования R разрешающий логический «0».

5. При использовании стробирования подать переменные с номерами от 1 до (n - 1) параллельно на управляющие входы двух DC, переменную Xn подать на вход R одного DC, а  – на вход другого DC.

– на вход другого DC.

6. Составить таблицу состояний реализуемых функций.

7. Объединить через схему «ИЛИ» с общей выходной шиной выходы DC, соответствующие двоичным наборам входных переменных, когда синтезируемая логическая функция равна логической «1».

8. Определить места объединений каждой шины с требуемым выходом DC, при одновременной реализации нескольких функций, по таблице состояний соответствующей функции.

9. Применять древовидные или клеточные структуры объединения DC при числе переменных n > 6.

6.1.

6.1.

6.2.

6.3.

6.4.

6.5.

6.6.

|

|

|