|

2.4.1. Запоминающие элементы. 2.5. Потенциальные системы цифровых элементов

|

|

|

|

2. 4. 1. Запоминающие элементы

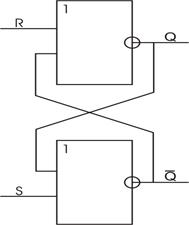

В качестве запоминающих элементов (ЗУ) в составе логических схем используются, в основном, статические триггеры. Триггер имеет два устойчивых состояния “1” и “0”. Простейшим ЗУ является однотактный R–S- триггер или триггер с раздельным управлением

Рис. 2. 9. УГО R–S - триггера с раздельным управлением

Q – прямой выход Q– инверсный выход

Q – прямой выход Q– инверсный выход

S (Set) – вход установки в “1”

R(Reset) – вход установки в “ 0 “.

Триггер находится в состоянии “1”, если на его прямом выходе будет потенциал, соответствующий значению “1”, на инверсном - “0” (рис. 2. 8). Существуют два типа R–S -триггеров: триггер с прямым управлением и инверсным управлением.

В работе триггера выделяются 3 режима:

1) режим хранения информации,

2) режим уcтановки в “0”,

3) режим установки в “1”.

R–S -триггер с прямым управлением строится на базе элементов “ИЛИ-НЕ” (рис. 2. 10).

Рис. 2. 10. Логическая схема R–S- триггера с прямым управлением

Таблица 2. 7

| St | Rt | Qt+1 | Режимы |

| Qt = Q* | Хранения | ||

| 1 | Установка в “1” | ||

| Установка в “0” | |||

| ↑ | Запрещенный |

Состояния на входах триггера в момент времени t и состояния на прямом выходе триггера в момент (t+1), т. е. после срабатывания триггера, и соответствующие режимы представлены в табл. 2. 7, которая называется таблицей переходов. Как следует из этой таблицы, состояние триггера изменяется при поступлении на один из его входов сигнала “1”.

|

|

|

Триггер с инверсным управлением (R–S -триггер) построен на базе элементов “И-НЕ”. В табл. 2. 8 представлена таблица переходов R-S- триггера с инверсным управлением, из которой следует, что изменение состояния триггера происходит при поступлении на один из его входов сигнала “0”.

Рис. 2. 11. Логическая схема R–S - триггера с инверсным управлением

Таблица 2. 8

| St | Rt | Qt+1 | Режимы |

| ↑ | Запрещенный | ||

| Установка в “0” | |||

| Установка в “1” | |||

| Qt | Хранения |

2. 5. Потенциальные системы цифровых элементов

Существует довольно значительное количество различных типов потенциальных систем элементов. Они различаются по типам электронных приборов, которые используются для реализации тех или иных логических операций.

ДТЛ-диодно-транзисторная логика

ТТЛ – транзисторно-транзисторная логика

ЭСЛ – эмиттерно-связанная логика

МДП (МОП) – логика непосредственных связей.

Основные характеристики потенциальных систем цифровых элементов:

1) Состав системы цифровых элементов

В ее состав должен входить функционально полный набор логических элементов.

2) Уровни логических сигналов

3) Температурные характеристики - диапазон температур, в пределах которого цифровой элемент сохраняет работоспособное состояние.

4) Статические характеристики цифрового элемента снимают при подаче на вход постоянного напряжения. Эти характеристики представлены на рис. 2. 11. На основе статических характеристик определяются номинальные значения логических сигналов и области устойчивой работы.

Условия надежной работы элемента:

U0 ном + Uпомехи  U0 max

U0 max

U1 ном – Uпомехи  U1 min.

U1 min.

.

Рис. 2. 11. Статические характеристики потенциального элемента

5) Динамические характеристики получаются при подаче на вход ЦЭ потенциальных импульсных сигналов (рис. 2. 12).

|

|

|

На основе этих характеристик определяются временные задержки ЦЭ:

6) Коэффициент объединения по выходу - нагрузочная способность цифрового элемента – количество элементов данного

типа, которое может быть подключено к выходу так, чтобы его технические характеристики оставались в заданных пределах (рис. 2. 13).

Рис. 2. 12. Динамические характеристики потенциального ЛЭ элемента

|

|

|

|

……….

……….

Рис. 2. 13. Коэффициент объединения по выходу

7) Коэффициент объединения по входу - количество логических элементов данного типа, которые можно подключить на вход логического элемента так, что его характеристики остаются в заданных пределах.

8) Надежность цифрового элемента характеризуется наработкой на отказ. Наработка на отказ – это интервал времени от момента включения питания на схему до момента, когда данный цифровой элемент выйдет из строя.

|

|

|