|

2.6. Система цифровых элементов типа ТТЛ

|

|

|

|

2. 6. Система цифровых элементов типа ТТЛ

Система цифровых элементов типа ТТЛ относится к системам среднего быстродействия и предназначена для построения различных вычислительных устройств и систем цифровой автоматики.

Основные характеристики:

1) источник питания Е=5В,

2) положительная логика

,

,

3) температурный диапазон -60…1250С,

4) время задержки tзад. ср. = 30 -50нс.

В состав системы элементов включено большое количество различных логических элементов, отличающихся коэффициентами объединения по входам “И”, “ИЛИ”, а также нагрузочной способностью. Кроме того, в состав системы входят различные типы триггеров. Однако все ЛЭ и триггеры построены на основе единой принципиальной схемы, основанной на использовании многоэмиттерных транзисторов.

2. 6. 1. Универсальный логический элемент ЛЭ ( К 155)

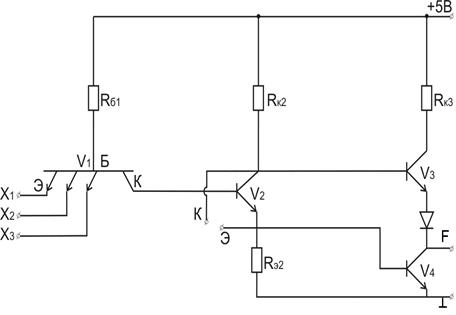

На рис. 2. 14 представлена принципиальная схема универсального логического элемента интегральной серии (ИС) К 155.

Рассмотрим ее принцип действия. Транзистор V1 – многоэмиттерный транзистор. В зависимости от того, какой сигнал подан на вход логической схемы, т. е. на эмиттер, переход “база – эмиттер” оказывается открытым или закрытым. Если на вход подан низкий уровень, то переход “база – эмиттер” открыт.

Рис. 2. 14. Принципиальная схема универсального логического элемента типа ТТЛ

Если хотя бы один переход “база - эмиттер” открыт, то ток из базовой цепи попадает соответственно в эмиттер, а в цепь коллектора при этом ток не проходит. Если на любой из входов подан высокий уровень сигнала, то соответствующий переход “база-эмиттер” закрыт.

Ток из базовой цепи в цепь коллектора попадает только в том случае, если закрыты все переходы “база-эмиттер”. Транзистор V1 реализует операцию “И”. Транзистор V2 выполняет функции инвертора. Транзисторы V3, V4 выполняют функции согласователей, усилителей мощности, т. е. обеспечивают на выходе схемы стандартные уровни выходного сигнала при небольшом выходном сопротивлении. Контакты К, Э используются для подключения логического расширителя (рис. 2. 15).

|

|

|

Рассмотрим принцип действия данного ЛЭ, заполняя таблицу истинности (ТИ) в табл. 2. 9. Подадим на все входы ЛЭ сигналы логического 0 и посмотрим, что будет на выходе.

Пусть X1 = X2 = X3: = 0, при этом все переходы “база-эмиттер” открыты и ток коллектора транзистора V1 равен 0, Iк1=0, следовательно, транзистор V2 закрыт, поэтому Uк2 ≈ 5В, Uэ2 ≈ 0 и транзистор V3 открыт, а V4 закрыт. На выходе ЛЭ будет F = Uв ≈ 2, 45В: =1.

Таблица 2. 9

| X1 | X2 | X3 | F |

| ... | |||

Если хотя бы на один из входов ЛЭ будет подан сигнал Х: =0, то соответствующий переход “база-эмиттер” в транзисторе V1 будет открыт и, следовательно, ЛЭ будет работать так же, как и в первом случае, т. е. на выходе ЛЭ будет F: =1.

Пусть X1 = X2 =X3 =Uв ≈ 2, 45 В, т. е. все переходы “база – эмиттер” в транзисторе V1 закрыты, ток коллектора равен току базы Iк1= Iб1 и транзисторы: V2 открыт, V3 закрыт, V4 открыт, и на выходе ЛЭ будет F: =0. Логическая операция, выполняемая данным элементом, представлена в таблице истинности 2. 9.

Данная таблица истинности соответствует логической операции “И-НЕ”.

F= ┐ ( X1& X2& X3) (2. 1)

Для расширения возможностей данного ЛЭ используется

логический расширитель, схема которого представлена на рис. 2. 15.

Подключение логического расширителя к универсальному ЛЭ осуществляется за счет объединения коллекторов и эмиттеров транзисторов V2 на рис. 2. 14 и 2. 15, которые включены на общую нагрузку.

|

|

|

Рис. 2. 15 Логический расширитель

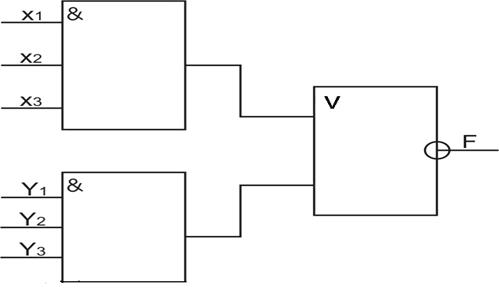

Соответствующая логическая структура показана на рис. 2. 16, при этом реализуется логическая функция типа “И-ИЛИ-НЕ”.

Соответствующая логическая структура показана на рис. 2. 16, при этом реализуется логическая функция типа “И-ИЛИ-НЕ”.

F = X1& X2& X3 V Y1& Y2& Y3 .

Рис. 2. 16. Логическая структура с расширителем

В МП-системе при обмене данными в каждый момент времени шина данных должна захватываться только одним из подключенных к ней устройств, которое получает при этом право выставлять на шину свои данные.

Технически эта задача обеспечивается тем, что все устройства, объединенные общей шиной, должны иметь трехстабильные схемы на выходе. Особенность этих логических схем состоит в том, что они могут находиться в трех состояниях. При этом могут быть следующие значения выходных сигналов:

стандартные логические сигналы F: = 0, F: =1 и в третьем состоянии F: = ¥ (Rвых=¥ ), что равносильно разрыву физической связи между логическим элементом и шиной данных.

Рассмотрим кратко, как работает трехстабильный логический элемент на примере ЛЭ типа ТТЛ серии 155 (рис. 2. 17).

Рис 2. 17 Принципиальная схема трехстабильного ЛЭ (ТТЛ)

Как следует из рис. 2. 17, представленная на нем схема отличается от стандартного ЛЭ типа ТТЛ присутствием транзистора V5, коллектор которого объединен с коллектором транзистора V2. Уровни логических сигналов ЛЭ ТТЛ

Uв> =2, 45: = 1 Uн< =0, 45: = 0

Управление режимами работы трехстабильного ЛЭ осуществляется сигналом Uупр, который поступает на базу V5.

Если Uупр: =0, то транзистор V5 – закрыт, ЛЭ работает в стандартном режиме в соответствии с выражением

F= ┐ (x1& x2)

Если Uупр: =1, то транзистор V5 – открыт, находится в режиме насыщения . Напряжение на коллекторе V2 - Uк2≈ 0. 2В,

и на эммитере V2 напряжение - Uэ2=0В.

Cледовательно, транзисторы V3, V4 – закрыты и Rвых=¥, F =¥.

Как указывалось выше, это означает, что данный ЛЭ практически отключен от шины данных.

|

|

|