|

Программы на основную память.

|

|

|

|

Программа загружается в ОП и занимает часть машинных ресурсов. Содержимое программы помещается в разных областях ОП: 1) размещение команд; 2) размещение данных; 3) размещение управляющих таблиц и 4) области ввода-вывода. Различают статическое размещение (перемещение) и динамическое.

При загрузке программы выделяют 2 случая:

1) емкость ОП больше емкости программы

2) емкость ОП меньше емкости программы. В этом случае имеется несколько методов выполнения программы. Наиболее распространенный случай – оверлейная структура, когда программа разбивается на части меньшие емкости ОП.

При выполнении программ различают абсолютный модуль программы, требующий размещения в одном и том же месте. При выполнении программы могут накладываться друг на друга по адресам ОП, а также между программами могут быть свободные участки. Наличие свободных участков носит название фрагментации памяти. Это явление нежелательно, и для записи программ в свободные, несмежные участки ОП в операционных системах имеется управляющая программа, называемая перемещаемый загрузчик.

Адресация в ЭВМ.

Линейная адресация существует только на уровне аппаратных средств, когда физический адрес выставляется на линии шины адреса и позволяет определить номер ячейки оперативной памяти (слово ОП), а также позволяет определить начальный адрес байта фиксированной единицы информации.

В программах линейная адресация отсутствует. Там существуют следующие способы получения адреса:

1) математический адрес

2) исполнительный адрес

3) линейный адрес

4) физический адрес.

Различают 16, 32, 64, 128 разрядную адресацию для различных видов ЭВМ.

При обращении к памяти на шине данных формируется линейный адрес. На базе линейной адресации тяжело организовать различные режимы работы систем (Virtual, Real, Protected и другие режимы).

|

|

|

Управление памятью.

В вычислительных системах на базе однокристальных процессоров введена сегментация памяти, и в общем случае адресация к любой ячейку памяти является в определении адреса границы сегмента (база) и смещения в сегменте. Эта пара носит название логического или виртуального адреса. Сегментные регистры содержат физические адреса памяти (границу параграфа). В первых процессорах (i86) размер сегмента составлял 64кб. Сегменты могли перекрывать друг друга, пересекаться и многократно пересекаться. Многократные пересечения сегментов сильно усложняли защиту информации в оперативной памяти. Любой программист мог обратиться к любому сегменту памяти. При вычислениях не проверялся адрес на корректность. При формировании адреса, который выходил за границы реальной физической памяти процессор получал фиктивные данные, либо зависал в ожидании поступления данных по шине.

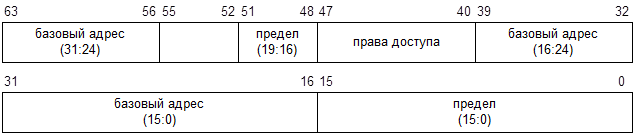

Начиная с i286, эта задача была решена. Использовался табличный способ управления, использовавшийся ранее на малых ЭВМ (PDP 8, PDP 11). Это позволило реализовать более сложную схему обращения к памяти и повысить скорость формирования физического адреса. Для этих целей было введено понятие дескриптор – описатель сегмента. Каждый сегмент хранится в восьми байтной структуре данных, которая называется дескрипторным регистром.

|

Базовый адрес – это начальный адрес сегмента (2, 3, 4, 7 байты дескриптора).

Предел – 20-ти битное поле, которое определяет границу сегмента. Предел равен размеру сегмента в байтах или в страницах (определяется битом гранулярность).

Пятый байт определяет: права доступа к сегменту, присутствие сегмента в памяти, уровень привилегий и целевое использование сегмента.

|

|

|

Дескрипторные таблицы.

Начиная с процессоров i386, допускается любое число сегментов памяти. Описывающие сегменты дескрипторы позволяют процессору следить за информацией о сегментах. Поэтому все дескрипторы располагаются в одном месте. Первые варианты дескрипторов реализовывались аппаратно, а потом стали размещать в ОП. Эта область памяти получила название дескрипторных таблиц. Дескрипторные таблицы делятся на 3 типа, отличающиеся способом использования:

1) GDT (global descriptor table) – глобальные дескрипторные таблицы. Это общесистемная таблица. Ее могут использовать все задачи. Для локализации GDT используется специальный регистр GDTR, в котором находится 32-х битное поле линейного базового адреса таблицы и 16-ти битное поле предела с битной гранулярностью. Значение предела L связано с числом дескрипторов N соотношением L=8*N-1.

2) IDT (interrupt descriptor table) – дескрипторная таблица прерываний. Она содержит дескрипторы специальных системных объектов. Эти объекты называются шлюзами и определяют точки входа процедур обработки прерываний и особых случаев. Данная таблица служит заменой таблицы векторов прерываний. Для локализации таблицы IDT служит системный регистр IDTR. Его формат аналогичен формату регистра GDTR.

Для перевода микропроцессоров в реальный режим необходимо создать обе дескрипторные таблицы и инициировать соответствующие системные регистры.

3) LDT (local descriptor table) – локальные дескрипторные таблицы. Используются в мультизадачной системе для каждой задачи в дополнение к глобальной дескрипторной таблице, она определяет сегменты доступные только этой системной задаче. Для локализации LDT предназначен 16-ти разрядный регистр LDTR, который содержит только селектор.

GDTR и IDTR определяются при загрузке базового адреса и пределов и выполняется только один раз при подготовке микропроцессора к заданному режиму работы (например R режим) и в дальнейшем содержимое регистров не меняется. Участки ОП в которых содержатся первые две дескрипторные таблицы не могут участвовать в свопинге (удаляться на жесткий диск). LDT не является необходимой и создается по мере необходимости. Для хранения LDT используются сегменты памяти, а их дескрипторы хранятся в GDT.

Формирование линейного адреса через дескрипторные таблицы.

В микропроцессорах начиная с i386 формирование линейного адреса выполняется двумя способами: 1) 16-ти битная адресация; 2) 32-х адресная адресация.

|

|

|